FPGA——zhixin培训 Day_06——数码管(2)+电子时钟

A.数码管

一、设计背景:

数码管可做电子时钟,可显示参数等。

二、设计需求:

设计六个数码管的驱动电路,使六个数码管能够循环显示“HELLO.”。

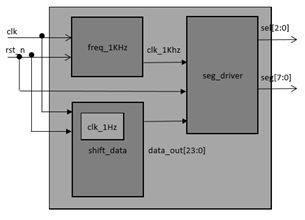

架构图:

四、代码:

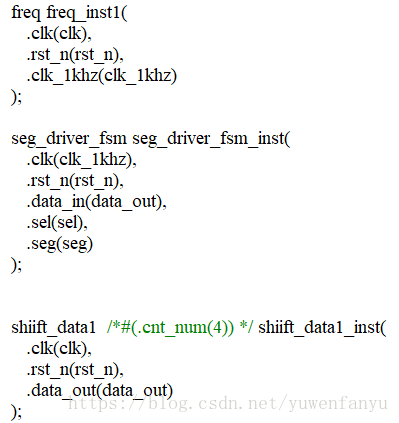

顶层模块:

例化三个子模块

Freq是产生1KHz的时钟,来刷新数码管,使六个数码管一起亮;

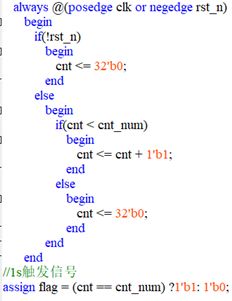

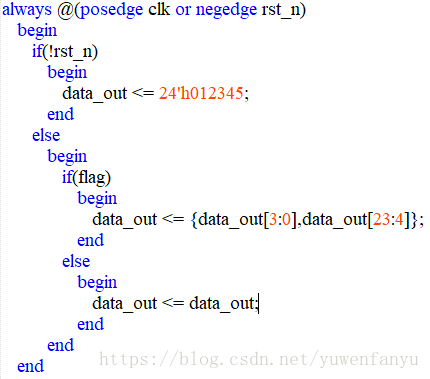

Shift_data1用来移位操作,使显示的值循环显示。该模块中移位需要按要求1s移位一次,因此需要产生一个1s的flag;

产生1秒的代码如下:

然后用来移位的代码如下:

接着,是数码管显示模块:

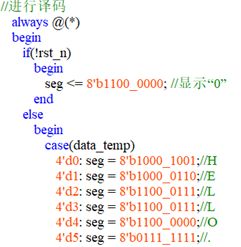

译码代码如下:

用状态机(FSM)写的给每个数码管赋值

Data_in是上个模块给的data_out的值;在顶层连线时候要注意。

B.电子时钟

一、设计背景:

数码管可做电子时钟,可显示参数等。

二、设计需求:

用6个数码管显示时,分,秒。

三、代码

方法一:

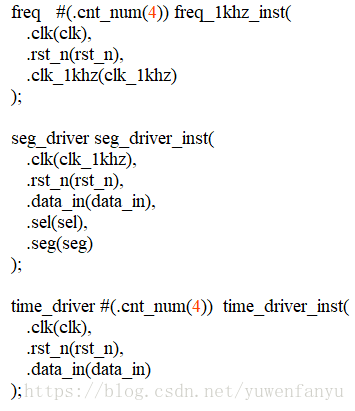

顶层模块:

说明:分频模块,是之前写好的,用于调用,产生的是1KHz的时钟,用于6个数码管显示;

Teme_driver:

1s就加一是写在该模块里面的,如下:

下面的时钟都用这个clk_1hz的时钟。

秒:

0 always @(posedge clk_1hz)

1 begin

2 if(!rst_n)

3 begin

4 cnt_sec0 <= 4'd0;

5 end

6 else

7 begin

8 if(cnt_sec0 == 4'd9)

9 begin

10 cnt_sec0 <= 4'd0;

11 end

12 else

13 begin

14 cnt_sec0 <= cnt_sec0 + 1'd1;

15 end

16 end

17 end

18

19

20 always @(posedge clk_1hz)

21 begin

22 if(!rst_n)

23 begin

24 cnt_sec1 <= 4'd0;

25 end

26 else

27 begin

28 if(cnt_sec1 == 4'd5 && cnt_sec0 == 9)

29 begin

30 cnt_sec1 <= 4'd0;

31 end

32 else if(cnt_sec0 == 9)

33 begin

34 cnt_sec1 <= cnt_sec1 + 1'd1;

35 end

36 else

37 begin

38 cnt_sec1 <= cnt_sec1;

39 end

40 end

41 end

42

43 assign data_in1 = {cnt_sec1,cnt_sec0};

分钟:

0 //min

1 always @(posedge clk_1hz)

2 begin

3 if(!rst_n)

4 begin

5 cnt_min0 <= 4'd0;

6 end

7 else

8 begin

9 if(cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

10 begin

11 cnt_min0 <= 4'd0;

12 end

13 else if(cnt_sec1 == 4'd5 && cnt_sec0 == 9)

14 begin

15 cnt_min0 <= cnt_min0 + 1'd1;

16 end

17 end

18 end

19

20 always @(posedge clk_1hz)

21 begin

22 if(!rst_n)

23 begin

24 cnt_min1 <= 4'd0;

25 end

26 else

27 begin

28 if(cnt_min1 == 5 && cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

29 cnt_min1 <= 4'd0;

30 else if(cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

31 cnt_min1 <= cnt_min1 + 1'd1;

32 end

33 end

小时:

0 //hour

1 always @(posedge clk_1hz)

2 begin

3 if(!rst_n)

4 begin

5 cnt_hour0 <= 4'd0;

6 end

7 else

8 begin

9 if((cnt_hour0 == 9 && cnt_min1 == 5 && cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9) || (cnt_hour1 == 2 && cnt_hour0 == 3 && cnt_min1 == 5 && cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9))

10 cnt_hour0 <= 4'd0;

11 else if(cnt_min1 == 5 &&cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

12 cnt_hour0 <= cnt_hour0 + 1'd1;

13 end

14 end

15

16 always @(posedge clk_1hz)

17 begin

18 if(!rst_n)

19 begin

20 cnt_hour1 <= 4'd0;

21 end

22 else

23 begin

24 if(cnt_hour1 == 2 && cnt_hour0 == 3 && cnt_min1 == 5 && cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

25 cnt_hour1 <= 4'd0;

26 else if(cnt_hour0 == 9 && cnt_min1 == 5 &&cnt_min0 == 9 && cnt_sec1 == 4'd5 && cnt_sec0 == 9)

27 cnt_hour1 <= cnt_hour1 + 1'd1;

28 end

29 end

30

31 assign data_in3 = {cnt_hour1,cnt_hour0};