XILINX FPGA 7系之 CLB/LUT/FF/Multiplexers

目录

1、CLB

2、Slice

2.1、SLICEM

2.2、SLICEL

2.3、SLICEL Vs SLICEM

3、LUT

4、FF

5、Multiplexers

5.1、MUX(4:1 )

5.2、MUX(8:1 )

5.3、MUX(16:1 )

6、Summary

Xilinx FPGA 的内部结构中最基本的构成便是 CLB 了,在更好的利用 Xilinx FPGA 之前,还是有必要更多的了解它的具体组成;

这里以 Xilinx 7 系列 FPGA 为 Base 来介绍它的基本组成单元 CLB, Xilinx 官方文档关于 CLB 的介绍位于:

ug474_7Series_CLB.pdf

1、CLB

CLB 的全称是 Configurable Logic Block,即可编程逻辑块,逻辑电路就是靠对 CLB 进行配置来实现各种各样的电路。一个 CLB 由如下部分组成:

1 个 CLB 包含了称之为 2 个 Slice 的单元,每个 Slice 之间并没有直接联系,而是都连接到一个交换矩阵,以访问通用路由矩阵;既然 CLB 由 2 个 Slice组成,那么接下来看看 Slice 的组成;

2、Slice

Xilinx 7 系列的 Slice 分为两类:SLICEL 和 SLICEM,FPGA中三分之二的 slice 是 SLICEL 而剩余的是 SLICEM

SLICEL 和 SLICEM 的区别主要是组成的资源不一样,所以他们最终能够构成的东西也有所区别;

2.1、SLICEM

一个 SLICEM 类型的 slice 的结构

由 SLICEM 的组成,从最左边开始看,最左边:

第一列:代表的是 LUT(Look Up Table),它是 CLB 的基本组成单元,可以看到,一个 SLICEM 拥有 4 个 6 输入的 LUT(A6:A1),O5、O6 是输出;

第二列:从下往上看,由 CIN 一直到 COUT,这部分是进位逻辑;

第三列:输入的 D,输出是 Q,是 D 触发器;

第四列:MUX;

第五列:也是 D 触发器(上面写了 FF/LAT,说明也可以配置为锁存器);

2.2、SLICEL

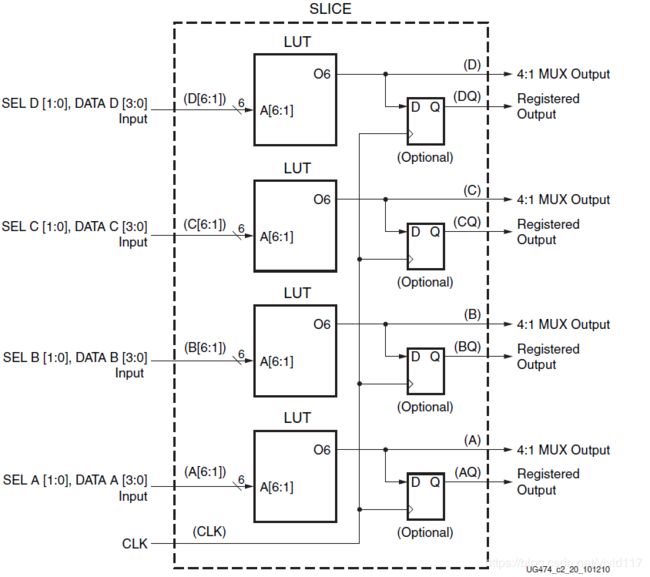

一个 SLICEL 类型的 slice 的结构

可以看到 SLICEL 类型的组成和 SLICEM 的组成基本差不多,仔细的看第一列呢?SLICEL 的 LUT 上明显比 SLICEM 的少很多东西,SLICEL 类型只有 A6:A1 和 O5、O6 输出,而 SLICEM 上内容更多;它代表 SLICEM 的 LUT 还可以作为 Distribute RAM(分布式内存)和移位寄存器逻辑;

2.3、SLICEL Vs SLICEM

每个 SLICEL 和 SLICEM 都拥有 4 个 6 输入 LUT,进位逻辑,以及 MUX 多路复用,和 8 个 FF,slice 均使用上面的元素来提供逻辑、算术;

SLICEM 的 LUT 能够配置为 Distribute RAM(分布式内存)和 Shift Register (移位寄存器逻辑) ;

Notes:在组成 CLB 的时候,有两种可能,一种是由两个 SLICEL 构成,另外一种是有一个 SLICEM 和 SLICEL;

所以整体来说,CLB 的构成如下所示:

3、LUT

LUT 查找表(Look Up Table)是 Slice 的基本组成部分,Xilinx 7 系列的 FPGA 内部每个 CLB 包含两个 Slice,每个 Slice 都包含 4 个 LUT,这些 LUT 都是 6 输入的(A1:A6),LUT 的本质是 RAM,6 输入意味着最大寻址是 2^6 也就是 64bit ,您可以将 LUT 想象为有 A1~A6 一共 6 个地址,可寻址 64bit 内容,烧写的时候,就是把这 64bit 内容准备好,当 A1:A6 输入不一样,那么寻址的 bit 内容也不一样,那么输出的 O6 也就不一样;

7系列FPGA中的函数发生器实现为六输入查找表(LUT)。slice的4个函数发生器(A,B,C和D)中的每一个都有六个独立输入(A输入A1至A6)和两个独立输出(O5和O6)。

1)函数发生器可以实现以下函数功能:

- 任意定义的六输入布尔函数

- 两个任意定义的五输入布尔函数,只要这两个函数共享公共输入

- 两个任意定义的布尔函数(3个和2个或更少输入)

2)6 输入功能使用:

- A1-A6 输入

- O6 输出

3)两个 5 输入或更少的函数使用:

- A1–A5 输入

- A6 驱动高

- O5 和 O6 输出

这里需要解释一下,配置为 1 个 6 输入的 LUT 和配置成 2 个 5 输入的 LUT 的具体情况:

一个 LUT 如下:

输入端为 A1~A6,可以寻址 2^6 = 64bits 的位,也就是 6 输入的 LUT 最终寻址是一个 bit,最终输出到 O6 上:

当配置成为 2 个 5输入的 LUT 的时候呢:

可以看到输入为 A1~A5,可以寻址就是 2^5=32bits,通过在 64bits 的 LUT 中烧录不同的 bit,可以做到同样的 A1~A5 的寻址,对应两个 32bits 空间存放的内容不一样,导致输出的 O6 和 O5 分别代表了两个 5 输入的 LUT 的输出;

4、FF

每个 slice 有 8 个 FF( flip-flop 即,触发器)。

从 SLICEM 和 SLICEL 的图解可以看到,中间那一列(4个)FF 和最后一列的 FF 对比起来,最后一列 FF 多了 “FF/LAT”,有 “FF/LAT” 的 FF 代表可以配置为边沿触发D型触发器或电平敏感锁存器,也就是说,一个 Slice 中的 8 个 FF,其中有 4 个只能作为 D 触发器,另外 4 个可以配置成为 D 触发器,或者锁存器;

D输入可以通过 AFFMUX,BFFMUX,CFFMUX 或 DFFMUX 的 LUT 输出直接驱动,也可以通过AX,BX,CX或DX输入绕过函数发生器的BYPASS slice输入直接驱动。 当配置为锁存器时,当CLK为低电平时,锁存器是透明的。对应如下右图

还有四个额外的存储单元,它们只能配置为边沿触发的D型触发器。 D输入可以由LUT的O5输出驱动,也可以由AX,BX,CX或DX输入的BYPASS slice输入驱动。 当原始的四个存储单元配置为闩锁时,这四个附加的存储单元将无法使用。对应如下左图

slice 中的两种配置版本: 4个寄存器和4个寄存器/锁存器

5、Multiplexers

7系列FPGA中的函数发生器和相关的多路复用器可以实现以下功能:

- 使用一个LUT的 4:1 多路复用器,每个 Slice 四个 4:1 MUX

- 使用两个LUT的 8:1 多路复用器,每个 Slice 两个 8:1 MUX

- 使用四个LUT的 16:1 多路复用器,每个 Slice 一个 16:1 MUX

5.1、MUX(4:1 )

每个LUT可以配置为4:1 MUX。 4:1 MUX可以通过触发器在同一片中实现。 一个slice中最多可以实现四个4:1 MUX,如下所示:

注意,这里其实是每一个 LUT 实现成为 MUX,LUT 的输入还是 A1-A6 一共 6 个,使用其中的 4 个 bit 表示输入的 4 MUX 的 Input 数据,使用另外 2 个 bit 作为选通信号!所以一个 LUT 可以做成 4:1 MUX,那么一个 SLICE 就可以做成 4 个 4:1 MUX 复用器;

5.2、MUX(8:1 )

每个 Slice 具有一个 F7AMUX 和一个 F7BMUX。 这两个MUX组合了两个LUT的输出,一个slice中最多可以实现 2 个8:1 MUX,如图所示:

5.3、MUX(16:1 )

当然也可以级联 4 个 LUT + F7AMUX + F7BMUX 在 F7AMUX + F7BMUX之后在接连 F8MUX 形成 MUX 16:1 这里不在多说;

6、Summary

由上所述,可以知道,Xilinx 7 系列(A,K,V,以及 ZYNQ)的 CLB 是衡量 FPGA 的资源的一种标杆,并且:

1 个 CLB 含 2 个 Slice

Slice 分为 SLICEL 和 SLICEM(三分之二的slice是SLICEL而剩余的是SLICEM)

1 个 Slice 包含 4 个 6 输入的 LUT、8个 FF(4个D触发器,4个可配D触发器和锁存器)

只有 SLICEM 是配置为 Distribute 64bit-RAM 或者 32bit 的 Shift Register 或者 2 个 16bit Shift Register。

1 个 CLB 可能是由 2 个 SLICEL 组成,或者有 1 个 SLICEL + 1 个 SLICEM

LUT 可以级联成为 4 个 1:4的 MUX,或者 2 个 1:8 的 MUX,或者1个1:16的 MUX

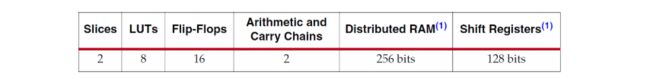

官方文档对一个 CLB 的资源描述为:

关于 Carry Chains、distributed RAM 和 Shift Registers 的详细内容,在以后的章节在接着分析,这里需要记住一点,这个表格中的 2 个 Slices,包含 8 个 LUT,每个 LUT 是 6 输入的,也就是 64bit,那么 8 个 LUT 不就是 8 x 64bit = 512 bit 啊,为啥只能够代表 256 的 distributed RAM?因为只有 SLICEM 才能够被配置成为 distributed RAM,一个 CLB 最多一个 SLICEM,所以need,也就是 256 bits了;

相关参考:

https://blog.csdn.net/huxiaokai2005/article/details/89460269

https://blog.csdn.net/huxiaokai2005/article/details/89460324

https://blog.csdn.net/vivid117/article/details/102841135