- 基于 STM32+FPGA 的快速傅里叶频域图像在 TFT 中显示的设计与实现(项目资料)(ID:8)

嵌入式资料库

嵌入式项目合集fpga开发stm32嵌入式硬件单片机

目录摘要1绪论1.1研究背景与意义1.2国内外研究现状1.3研究内容与目标2系统方案设计2.1总体架构设计2.2硬件方案设计2.2.1主控模块选型2.2.2FPGA模块选型2.2.3TFT显示模块选型2.2.4通信方案设计2.3软件方案设计2.3.1FFT算法实现方案2.3.2频域图像渲染方案3硬件电路设计3.1STM32最小系统电路3.2FPGA模块电路3.3TFT显示模块电路3.4软件IIC通

- 【优秀文章】7月优秀文章推荐

优秀文章智能自主运动体与人工智能技术——环境感知、SLAM定位、路径规划、运动控制、多智能体协同作者:fpga和matlabC++之红黑树认识与实现作者:zzh_zao【手把手带你刷好题】–C语言基础编程题(十)作者:草莓熊Lotso飞算JavaAI:从“码农”到“代码指挥官”的终极进化论作者:可涵不会debug前端网页开发学习(HTML+CSS+JS)有这一篇就够!作者:一颗小谷粒

- FPGA的开发流程

InnoLink_1024

FPGARTL设计Verilogfpga开发

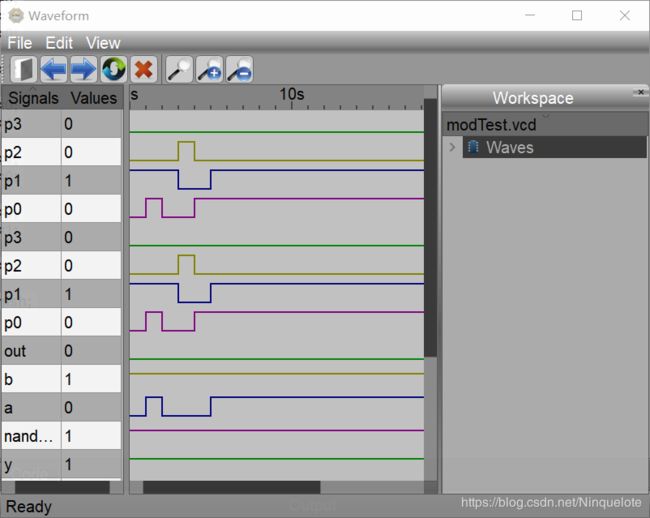

FPGA(现场可编程门阵列)的开发流程是一个系统化的过程,涉及从设计构思到最终硬件实现的多步骤工作。以下以XilinxKintex-7系列FPGA为例,详细介绍典型的FPGA开发流程,涵盖设计、实现、验证和部署等阶段,力求清晰、全面且简洁。FPGA开发流程概述FPGA开发流程通常包括以下主要阶段:需求分析与架构设计RTL设计(硬件描述语言编码)功能仿真综合(Synthesis)实现(Impleme

- 扒开嵌入式硬件的底裤(上)!从 PCB 到 FPGA/IC 设计,小白到 CTO 的必学秘籍 硬核知识点全揭秘!从c语言入门到mcu与arm架构及外设相关

small_wh1te_coder

嵌入式内核嵌入式开发嵌入式硬件算法c汇编面试驱动开发单片机

【硬核揭秘】嵌入式硬件工程师的“底裤”:从入门到牛逼,你必须知道的一切!第一部分:破冰与认知——嵌入式硬件工程师的“世界观”嘿,各位C语言老铁,以及所有对“让硬件听你话”充满好奇的朋友们!我是你们的老朋友,一个常年“折腾”在代码和电路板之间的码农。今天,咱们要聊一个真正能让你“硬”起来的话题——如何成为一个合格、优秀、牛逼的嵌入式硬件工程师!你可能正坐在电脑前,敲着C语言代码,刷着力扣算法题,心里

- basic verilog 语法--FPGA入门1

Kent Gu

FPGAfpga开发

1,Assign语法Assignisonlyforwiretypevarity;1.1definemodulemain(inputclkIn,//50M,20nsinputspi_clk,inputspi_mosi,inputspi_cs,inputreset_FPGA,outputwireout_LD_PULS_trig_Out//LDtrigout)1.2assignout_LD_PULS_t

- FPGA实现JPEG编码器的完整项目指南

本文还有配套的精品资源,点击获取简介:JPEG编码是一种广泛使用的数字图像压缩技术,通过在FPGA上实现该编码器,可以为嵌入式系统提供高效的图像处理。FPGA的可编程逻辑单元使其成为实现JPEG编码的理想平台。实现过程包括颜色空间转换、分块、离散余弦变换(DCT)、量化和熵编码等关键步骤。此外,testbench仿真用于验证设计的功能和性能,而资源优化确保了设计的高效性和低功耗。该实现过程需要深入

- FPGA原型验证方法学:提升芯片设计验证效率的利器

窦莎言Firm

FPGA原型验证方法学:提升芯片设计验证效率的利器去发现同类优质开源项目:https://gitcode.com/项目介绍在芯片设计领域,验证阶段是确保设计功能正确性和性能优化的关键环节。传统的验证方法虽然有效,但在复杂性和效率上存在一定的局限性。为了解决这一问题,FPGA原型验证方法学应运而生。本项目提供了一个名为“FPGA原型验证方法学”的资源文件,旨在帮助芯片设计工程师、验证工程师以及其他相

- FPGA原型验证资源下载:助力工程师提升工作效率

FPGA原型验证资源下载:助力工程师提升工作效率去发现同类优质开源项目:https://gitcode.com/项目介绍在当今电子设计领域,FPGA原型验证作为ASIC设计流程中的重要环节,对于确保设计质量、缩短产品上市时间具有至关重要的作用。FPGA原型验证资源下载,一个专为电子工程师设计的开源项目,提供了从ASIC代码到FPGA代码转换的全面指南,以及主流FPGA厂家工具的使用方法,是工程师们

- usb3.0开发

小xiao白

usb3.0

CYUSB3014开发板开发开发环境:SDK开发工具,编辑器和编译器使用Eclipse,使用固件例程slavefifo。测试数据使用controlcenter,测试速率使用streamer,均在Cypress下。相关文档在:SDK默认安装路径/Cypress/EZ-USBFX3SDK/1.3/doc下。本项目使用了EP0的in和out端点作为控制端点EP1的in和out端点作为pc与fpga传输数

- FPGA内部资源介绍

cycf

FPGA之道fpga开发

FPGA内部资源介绍目录逻辑资源块LUT(查找表)加法器寄存器MUX(复用器)时钟网络资源全局时钟网络资源区域时钟网络资源IO时钟网络资源时钟处理单元BLOCKRAMDSP布线资源接口资源用户IO资源专用高速接口资源总结1.逻辑资源块逻辑资源块是FPGA中最重要的资源,它在FPGA芯片中占的比重最大。Xilinx公司称它为CLB(ConfigurableLogicBlock),而Altera公司称

- 【教程4>第7章>第26节】基于FPGA的RS(204,188)译码verilog实现10——RS译码模块整体实现与性能仿真评估

fpga和matlab

#第7章·通信—信道编译码fpga开发RSverilogRS译码教程4

本课程学习成果预览目录1.软件版本2.RS译码模块整体实现介绍2.1伴随式计算(SyndromeCalculation)2.2擦除位置处理(ErasureHandling)2.3多项式乘法(PolynomialMultiplication)2.4欧几里得算法(EuclideanAlgorithm)2.5钱搜索(ChienSearch)3.RS译码模块整体FPGA实现4.RS译码仿真测试5.视频操作

- PCIe Crosslink

zly8865372

fpga开发

PCIeCrosslink:概念、应用与实现PCIeCrosslink(交叉连接)是一种特殊的PCIe链路连接方式,允许两个PCIe设备(通常是RootComplex或Endpoint)直接通过PCIe链路互连,而无需通过传统的PCIeSwitch或RootComplex转发。这种技术主要用于高性能计算(HPC)、FPGA加速、GPU直连等场景,以降低延迟并提高带宽利用率。1.PCIeCrossl

- 可编程逻辑器件的发展与比较

cycf

FPGA之道fpga开发

可编程逻辑器件的发展与比较文章目录可编程逻辑器件的发展与比较一、早期的离散逻辑芯片二、复杂可编程逻辑器件(CPLD)(一)CPLD的诞生(二)CPLD的结构(三)CPLD的特点三、现场可编程门阵列(FPGA)(一)FPGA的架构变革(二)FPGA的特点四、CPLD与FPGA的对比五、总结一、早期的离散逻辑芯片在可编程逻辑器件(PLD)发明之前,设计师们只能使用一些专用的小芯片来搭建系统,这些小芯片

- FPGA设计的上板调试

cycf

FPGA之道fpga开发

FPGA设计的上板调试指南文章目录一、如何解决问题(一)开发板状态检查当系统出现问题时,首先需要确认开发板是否工作正常。开发板的预测试和日常检查是确保调试顺利进行的关键步骤。1.开发板预测试预测试的定义:在开发板正式投入FPGA设计调试之前,编写一些功能简单的FPGA测试设计并运行,以确保开发板的硬件环境正常运行。这一步非常重要,因为未经过预测试的开发板可能会导致各种问题,甚至损坏芯片或电容。预测

- 呼吸灯 verilog FPGA 基础练习8

cycf

FPGAverilog编码基础篇fpga开发

呼吸灯verilogFPGA基础练习8发现问题,用技术解决问题。兴趣是自己的源动力!目录呼吸灯verilogFPGA基础练习8前言一、呼吸灯1.1呼吸灯原理1.2实现方案1.2.1功能代码1.2.2仿真代码1.2.3仿真结果1.2.4计数器的基本时间单位总结前言呼吸灯的练习的主要目的是对计数器使用的进阶,理解计数器计数使用的基础时间单位的变化,对计数器的影响。一、呼吸灯1.1呼吸灯原理我们知道同一

- 90.xilinx复位低电平(一般使用低电平复位)

cmc1028

笔记笔记

XilinxFPGA中的寄存器(Flip-Flop)**确实支持异步复位**,但具体实现方式取决于你使用的设计方法(HDL代码风格或原语实例化)。以下是详细说明:---###1.**Xilinx寄存器的复位特性**-**同步复位和异步复位均支持**,但需要通过代码或原语明确指定。-异步复位的信号通常会直接连接到寄存器的`CLR`(Clear,低电平有效)或`PRE`(Preset,高电平有效)端口

- 116-基于5VLX110T FPGA FMC接口功能验证6U CPCI平台

Anin蓝天(北京太速科技-陈)

fpga开发嵌入式硬件图像处理

一、板卡概述本板卡是Xilinx公司芯片V5系列芯片设计信号处理板卡。由一片Xilinx公司的XC5VLX110T-1FF1136/XC5VSX95T-1FF1136/XC5VFX70T-1FF1136芯片组成。FPGA接1片DDR2内存条2GB,32MBNorflash存储器,用于存储程序。外扩SATA、PCI、PCIexpress、千兆网络接口、SFP接口,自定义总线支持最大到266个IO。该

- FPGA FMC 接口

LEEE@FPGA

FPGA高速接口开发fpga开发FMC

1FMC介绍FMC接口即FPGAMezzanineCard接口,中文名为FPGA中间层板卡接口。以下是对它的详细介绍:标准起源:2008年7月,美国国家标准协会(ANSI)批准和发布了VITA57FMC标准。该标准由从FPGA供应商到最终用户的公司联盟开发,旨在为位于基板(载卡)上的FPGA提供标准的扩展卡外形、连接器和模块化接口。接口构成:整个FMC模块由子板模块、载卡两部分构成。子板模块和载卡

- 山东大学FPGA课程实验一 加法器设计

小田不甜~

fpga开发

【实验题目】设计一个16位二进制全加器模块。用层次化设计方法,设计一个16位二进制全加器模块。设计一个16位二进制超前进位全加器模块。设计一个16-bit8421-BCD码全加器模块。【实验软件工具】QuartusII;ModelSimSE.【实验要求】实验内容与原理说明(包括框图、逻辑表达式和真值表);实验模块程序代码(设计模块DesignBlock)和激励代码(激励模块TestBench);仿

- FPGA设计的时序分析概要

cycf

FPGA之道fpga开发

FPGA设计的时序分析文章目录FPGA设计的时序分析时序分析的概念和必要性时序分析的分类映射后时序分析时序约束与时序分析的关系特殊情况小总结时序分析的概念和必要性时序分析,也叫静态时序分析(StaticTimingAnalysis,简称STA),它通过完整的分析方式判断IC是否能在使用者的时序环境下正常工作,为确保IC品质提供了一个很好的解决方案。也许有人会问,我的FPGA设计已经通过了功能仿真,

- Xilinx FPGA ICAP原语实现多重配置

whik1194

ISEVivadoMicroBlaze系列教程FPGAxilinxICAPMultiboot多重配置

文章目录1.FPGA可以运行几个固件2.XilinxICAP原语简介3.ICAP原语模板的使用4.ICAP在Spartan-6上的使用5.ICAP在Kintex-7上的使用工程下载1.FPGA可以运行几个固件众所周知,常见的FPGA通常为SRAM结构,固件程序一般存放在外置的串行Flash中,比如SPIFlash,M25P16或N25Q128等。FPGA启动时,一般先从SPI起始地址开始加载数据到

- 基于 Kintex UltraScale 系列 2 路 QSFP+40G 光纤 PCIe 数据传输卡 / 光纤适配器(5GByte/s 带宽KU060光纤 PCIe 数据传输卡)

F_white

数据中心视频与图像采集处理机器视觉

PCIE732是一款基于PCIE总线架构的高性能数据传输卡,板卡具有1个PCIex8主机接口、2个QSFP+40G光纤接口,可以实现2路QSFP+40G光纤的数据实时采集、传输。板卡采用Xilinx的高性能KintexUltraScale系列FPGA作为实时处理器,板载2组独立的72位DDR4SDRAM大容量缓存。板卡具有1个RJ45千兆以太网口以及若干IO信号。一般应用于基于服务器的雷

- 中科亿海微SoM模组——基于FPGA+RSIC-V的计算机板卡

ehiway

fpga开发

基于FPGA+RSIC-V的计算机板卡主芯片使用中科亿海微EQ6HL45-CSG324FPGA芯片和高性能微控制器HPM6880,并集合ADCLHA6958H、6通道数字隔离器SiLM5760、SiLM5763、内存W634GU6QB等器件,板卡实现了大容量配置存储等功能的融合,为模拟信号采集、数字信号处理、逻辑控制等应用提供高性能混合信号处理通用硬件平台。图板卡硬件整体框图图板卡实物图EQ6HL

- mb_bootloop_le.elf是使用microblaze默认的elf文件,这个文件包括哪些内容?

hahaha6016

硬件设计fpga开发

一、mb_bootloop_le.elf说明1.mb_bootloop_le.elf是使用microblaze的FPGA的时候的默认的elf文件;2.XilinxSDK中的.elf文件全称为“ExecutableandLinkingFormat”(ELF)文件3.fpga开发中xilinxsdk的elf文件就是arm程序文件;elf文件大小就决定了你的堆栈大小要分配多大二、mb_bootloop

- 可编程逻辑器件的演进与对比分析

cycf

FPGA之道fpga开发

可编程逻辑器件的演进与对比分析目录离散逻辑芯片与早期PLD的限制CPLD的诞生与结构特点FPGA的架构创新CPLD与FPGA的核心差异总结1.离散逻辑芯片与早期PLD的限制在还没有发明出可编程逻辑器件(PLD:ProgrammableLogicDevice)之前,设计师们只能使用一些专用的小芯片来搭建系统,这些小芯片被称为离散逻辑芯片。这些早期的PLD产品日渐不能满足人们的需求,于是新的可编程逻辑

- Linux configfs机制

liujiliei

1、在使用intelSOC过程中,驱动的DTS需要在内核启动以后把FPGAcoreload以后加载PL侧设备的DTS,此时使用的是Linux的dts的overlay机制,该机制本质是使用Linux的configfs机制,在此分析。2、Linux内核驱动中使用的设备树作为驱动match的方法,在内核初始化时候会对dts解析,然后生成一个个的devicenode,根据node中的compatile与d

- FPGA和嵌入式系统的核心区别

2301_82243800

fpga开发

灵活性:FPGA具有高度的灵活性,可以根据需要重新编程以实现不同的功能。嵌入式系统的硬件功能通常是固定的,无法进行大规模的硬件级别的修改。开发周期:FPGA的开发周期相对较短,因为它可以通过重新编程来实现新功能,快速原型设计和迭代能力可以缩短开发周期。嵌入式系统的开发周期相对较长,因为它需要进行硬件设计、芯片制造和软件开发等多个环节。性能:FPGA芯片具有并行处理的能力,可以实现高性能计算和数据处

- [FPGA]嵌入式系统FPGA设计资源

元直数字电路验证

数模混合电路设计与仿真fpga开发嵌入式硬件

嵌入式系统FPGA设计资源一、供应商https://www.altera.com-AlteraFPGA供应商网站https://www.altera.com/events/northamerica/intel-soc-fpga-developer-forum/overview.html-SoC开发人员论坛https://www.altera.com/content/dam/altera-www/g

- FPGA(现场可编程门阵列)是什么?

Yashar Qian

#嵌入式fpga开发计算机体系结构嵌入式硬件

FPGA(现场可编程门阵列)是什么?FPGA(现场可编程门阵列,Field-ProgrammableGateArray)是一种可通过编程配置硬件电路的半导体芯片,其核心特点是硬件逻辑可重构,既能像软件一样灵活修改,又能像专用芯片(ASIC)一样高效运行。以下是通俗易懂的解析:⚙️术语拆解Field-Programmable(现场可编程):芯片出厂后,用户可通过硬件描述语言(如Verilog/VHD

- 异构计算解决方案(兼容不同硬件架构)

ARM2NCWU

硬件架构

异构计算解决方案通过整合不同类型处理器(如CPU、GPU、NPU、FPGA等),实现硬件资源的高效协同与兼容,满足多样化计算需求。其核心技术与实践方案如下:一、硬件架构设计异构处理器组合主从协作模式:采用通用CPU(如ARMCortex-M3)作为主处理器,搭配专用协处理器(如MSP430微控制器)处理特定任务(如射频通信),通过串口/USB/以太网实现通信。众核架构:集成CPU、GPU、N

- java Illegal overloaded getter method with ambiguous type for propert的解决

zwllxs

javajdk

好久不来iteye,今天又来看看,哈哈,今天碰到在编码时,反射中会抛出

Illegal overloaded getter method with ambiguous type for propert这么个东东,从字面意思看,是反射在获取getter时迷惑了,然后回想起java在boolean值在生成getter时,分别有is和getter,也许我们的反射对象中就有is开头的方法迷惑了jdk,

- IT人应当知道的10个行业小内幕

beijingjava

工作互联网

10. 虽然IT业的薪酬比其他很多行业要好,但有公司因此视你为其“佣人”。

尽管IT人士的薪水没有互联网泡沫之前要好,但和其他行业人士比较,IT人的薪资还算好点。在接下的几十年中,科技在商业和社会发展中所占分量会一直增加,所以我们完全有理由相信,IT专业人才的需求量也不会减少。

然而,正因为IT人士的薪水普遍较高,所以有些公司认为给了你这么多钱,就把你看成是公司的“佣人”,拥有你的支配

- java 实现自定义链表

CrazyMizzz

java数据结构

1.链表结构

链表是链式的结构

2.链表的组成

链表是由头节点,中间节点和尾节点组成

节点是由两个部分组成:

1.数据域

2.引用域

3.链表的实现

&nbs

- web项目发布到服务器后图片过一会儿消失

麦田的设计者

struts2上传图片永久保存

作为一名学习了android和j2ee的程序员,我们必须要意识到,客服端和服务器端的交互是很有必要的,比如你用eclipse写了一个web工程,并且发布到了服务器(tomcat)上,这时你在webapps目录下看到了你发布的web工程,你可以打开电脑的浏览器输入http://localhost:8080/工程/路径访问里面的资源。但是,有时你会突然的发现之前用struts2上传的图片

- CodeIgniter框架Cart类 name 不能设置中文的解决方法

IT独行者

CodeIgniterCart框架

今天试用了一下CodeIgniter的Cart类时遇到了个小问题,发现当name的值为中文时,就写入不了session。在这里特别提醒一下。 在CI手册里也有说明,如下:

$data = array(

'id' => 'sku_123ABC',

'qty' => 1,

'

- linux回收站

_wy_

linux回收站

今天一不小心在ubuntu下把一个文件移动到了回收站,我并不想删,手误了。我急忙到Nautilus下的回收站中准备恢复它,但是里面居然什么都没有。 后来我发现这是由于我删文件的地方不在HOME所在的分区,而是在另一个独立的Linux分区下,这是我专门用于开发的分区。而我删除的东东在分区根目录下的.Trash-1000/file目录下,相关的删除信息(删除时间和文件所在

- jquery回到页面顶端

知了ing

htmljquerycss

html代码:

<h1 id="anchor">页面标题</h1>

<div id="container">页面内容</div>

<p><a href="#anchor" class="topLink">回到顶端</a><

- B树、B-树、B+树、B*树

矮蛋蛋

B树

原文地址:

http://www.cnblogs.com/oldhorse/archive/2009/11/16/1604009.html

B树

即二叉搜索树:

1.所有非叶子结点至多拥有两个儿子(Left和Right);

&nb

- 数据库连接池

alafqq

数据库连接池

http://www.cnblogs.com/xdp-gacl/p/4002804.html

@Anthor:孤傲苍狼

数据库连接池

用MySQLv5版本的数据库驱动没有问题,使用MySQLv6和Oracle的数据库驱动时候报如下错误:

java.lang.ClassCastException: $Proxy0 cannot be cast to java.sql.Connec

- java泛型

百合不是茶

java泛型

泛型

在Java SE 1.5之前,没有泛型的情况的下,通过对类型Object的引用来实现参数的“任意化”,任意化的缺点就是要实行强制转换,这种强制转换可能会带来不安全的隐患

泛型的特点:消除强制转换 确保类型安全 向后兼容

简单泛型的定义:

泛型:就是在类中将其模糊化,在创建对象的时候再具体定义

class fan

- javascript闭包[两个小测试例子]

bijian1013

JavaScriptJavaScript

一.程序一

<script>

var name = "The Window";

var Object_a = {

name : "My Object",

getNameFunc : function(){

var that = this;

return function(){

- 探索JUnit4扩展:假设机制(Assumption)

bijian1013

javaAssumptionJUnit单元测试

一.假设机制(Assumption)概述 理想情况下,写测试用例的开发人员可以明确的知道所有导致他们所写的测试用例不通过的地方,但是有的时候,这些导致测试用例不通过的地方并不是很容易的被发现,可能隐藏得很深,从而导致开发人员在写测试用例时很难预测到这些因素,而且往往这些因素并不是开发人员当初设计测试用例时真正目的,

- 【Gson四】范型POJO的反序列化

bit1129

POJO

在下面这个例子中,POJO(Data类)是一个范型类,在Tests中,指定范型类为PieceData,POJO初始化完成后,通过

String str = new Gson().toJson(data);

得到范型化的POJO序列化得到的JSON串,然后将这个JSON串反序列化为POJO

import com.google.gson.Gson;

import java.

- 【Spark八十五】Spark Streaming分析结果落地到MySQL

bit1129

Stream

几点总结:

1. DStream.foreachRDD是一个Output Operation,类似于RDD的action,会触发Job的提交。DStream.foreachRDD是数据落地很常用的方法

2. 获取MySQL Connection的操作应该放在foreachRDD的参数(是一个RDD[T]=>Unit的函数类型),这样,当foreachRDD方法在每个Worker上执行时,

- NGINX + LUA实现复杂的控制

ronin47

nginx lua

安装lua_nginx_module 模块

lua_nginx_module 可以一步步的安装,也可以直接用淘宝的OpenResty

Centos和debian的安装就简单了。。

这里说下freebsd的安装:

fetch http://www.lua.org/ftp/lua-5.1.4.tar.gz

tar zxvf lua-5.1.4.tar.gz

cd lua-5.1.4

ma

- java-递归判断数组是否升序

bylijinnan

java

public class IsAccendListRecursive {

/*递归判断数组是否升序

* if a Integer array is ascending,return true

* use recursion

*/

public static void main(String[] args){

IsAccendListRecursiv

- Netty源码学习-DefaultChannelPipeline2

bylijinnan

javanetty

Netty3的API

http://docs.jboss.org/netty/3.2/api/org/jboss/netty/channel/ChannelPipeline.html

里面提到ChannelPipeline的一个“pitfall”:

如果ChannelPipeline只有一个handler(假设为handlerA)且希望用另一handler(假设为handlerB)

来

- Java工具之JPS

chinrui

java

JPS使用

熟悉Linux的朋友们都知道,Linux下有一个常用的命令叫做ps(Process Status),是用来查看Linux环境下进程信息的。同样的,在Java Virtual Machine里面也提供了类似的工具供广大Java开发人员使用,它就是jps(Java Process Status),它可以用来

- window.print分页打印

ctrain

window

function init() {

var tt = document.getElementById("tt");

var childNodes = tt.childNodes[0].childNodes;

var level = 0;

for (var i = 0; i < childNodes.length; i++) {

- 安装hadoop时 执行jps命令Error occurred during initialization of VM

daizj

jdkhadoopjps

在安装hadoop时,执行JPS出现下面错误

[slave16]

[email protected]:/tmp/hsperfdata_hdfs# jps

Error occurred during initialization of VM

java.lang.Error: Properties init: Could not determine current working

- PHP开发大型项目的一点经验

dcj3sjt126com

PHP重构

一、变量 最好是把所有的变量存储在一个数组中,这样在程序的开发中可以带来很多的方便,特别是当程序很大的时候。变量的命名就当适合自己的习惯,不管是用拼音还是英语,至少应当有一定的意义,以便适合记忆。变量的命名尽量规范化,不要与PHP中的关键字相冲突。 二、函数 PHP自带了很多函数,这给我们程序的编写带来了很多的方便。当然,在大型程序中我们往往自己要定义许多个函数,几十

- android笔记之--向网络发送GET/POST请求参数

dcj3sjt126com

android

使用GET方法发送请求

private static boolean sendGETRequest (String path,

Map<String, String> params) throws Exception{

//发送地http://192.168.100.91:8080/videoServi

- linux复习笔记 之bash shell (3) 通配符

eksliang

linux 通配符linux通配符

转载请出自出处:

http://eksliang.iteye.com/blog/2104387

在bash的操作环境中有一个非常有用的功能,那就是通配符。

下面列出一些常用的通配符,如下表所示 符号 意义 * 万用字符,代表0个到无穷个任意字符 ? 万用字符,代表一定有一个任意字符 [] 代表一定有一个在中括号内的字符。例如:[abcd]代表一定有一个字符,可能是a、b、c

- Android关于短信加密

gqdy365

android

关于Android短信加密功能,我初步了解的如下(只在Android应用层试验):

1、因为Android有短信收发接口,可以调用接口完成短信收发;

发送过程:APP(基于短信应用修改)接受用户输入号码、内容——>APP对短信内容加密——>调用短信发送方法Sm

- asp.net在网站根目录下创建文件夹

hvt

.netC#hovertreeasp.netWeb Forms

假设要在asp.net网站的根目录下建立文件夹hovertree,C#代码如下:

string m_keleyiFolderName = Server.MapPath("/hovertree");

if (Directory.Exists(m_keleyiFolderName))

{

//文件夹已经存在

return;

}

else

{

try

{

D

- 一个合格的程序员应该读过哪些书

justjavac

程序员书籍

编者按:2008年8月4日,StackOverflow 网友 Bert F 发帖提问:哪本最具影响力的书,是每个程序员都应该读的?

“如果能时光倒流,回到过去,作为一个开发人员,你可以告诉自己在职业生涯初期应该读一本, 你会选择哪本书呢?我希望这个书单列表内容丰富,可以涵盖很多东西。”

很多程序员响应,他们在推荐时也写下自己的评语。 以前就有国内网友介绍这个程序员书单,不过都是推荐数

- 单实例实践

跑龙套_az

单例

1、内部类

public class Singleton {

private static class SingletonHolder {

public static Singleton singleton = new Singleton();

}

public Singleton getRes

- PO VO BEAN 理解

q137681467

VODTOpo

PO:

全称是 persistant object持久对象 最形象的理解就是一个PO就是数据库中的一条记录。 好处是可以把一条记录作为一个对象处理,可以方便的转为其它对象。

BO:

全称是 business object:业务对象 主要作用是把业务逻辑封装为一个对象。这个对

- 战胜惰性,暗自努力

金笛子

努力

偶然看到一句很贴近生活的话:“别人都在你看不到的地方暗自努力,在你看得到的地方,他们也和你一样显得吊儿郎当,和你一样会抱怨,而只有你自己相信这些都是真的,最后也只有你一人继续不思进取。”很多句子总在不经意中就会戳中一部分人的软肋,我想我们每个人的周围总是有那么些表现得“吊儿郎当”的存在,是否你就真的相信他们如此不思进取,而开始放松了对自己的要求随波逐流呢?

我有个朋友是搞技术的,平时嘻嘻哈哈,以

- NDK/JNI二维数组多维数组传递

wenzongliang

二维数组jniNDK

多维数组和对象数组一样处理,例如二维数组里的每个元素还是一个数组 用jArray表示,直到数组变为一维的,且里面元素为基本类型,去获得一维数组指针。给大家提供个例子。已经测试通过。

Java_cn_wzl_FiveChessView_checkWin( JNIEnv* env,jobject thiz,jobjectArray qizidata)

{

jint i,j;

int s