计算机组成原理课设题目详解

计算机组成原理课设题目详解

一、实验一

1、实验名称:

验证74LS181运算和逻辑功能

2、实验目的:

(1) 掌握算术逻辑单元(ALU)的工作原理;

(2) 熟悉简单运算器的数据传送通路;

(3) 画出逻辑电路图及布出美观整齐的接线图;

(4) 验证4位运算功能发生器(74LS181)组合功能。

3、实验原理:

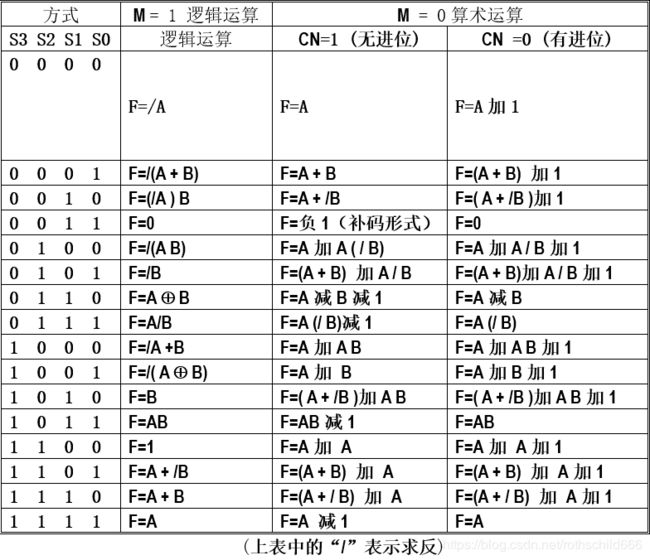

ALU能进行多种算术运算和逻辑运算。4位ALU-74LS181能进行16种算术运算和逻辑运算。功能表如下:

表1-1 4位ALU-74LS181算术运算和逻辑运算功能表

表1-2 ALU-74LS181引脚说明表

4、实验内容:

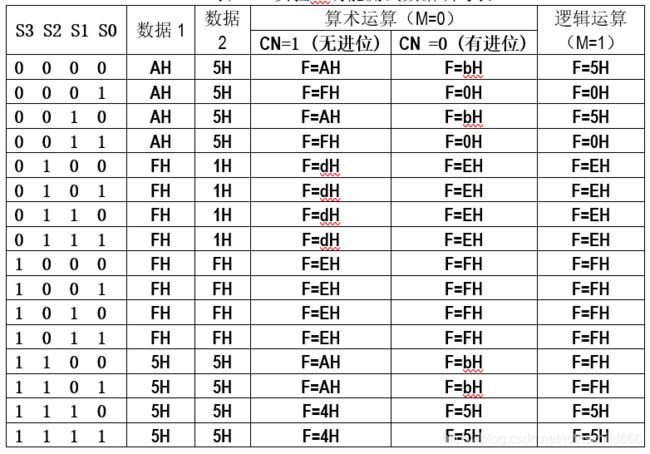

首先在使用multisim之前先了解了计算机组成原理课程设计指导书中multisim的使用方法和注意事项,然后了解实验一的74LS181运算和逻辑功能,结合指导书给出的74LS181运算和逻辑功能表,然后大概的理解了74LS181之后就开始在multisim画出逻辑电路图及布出美观整齐的接线图。在multisim中画逻辑图过程是首先是找到需要的电源、元器件如74LS181、DSWPK_8、DCD_HEX等,然后借鉴指导书给出的4位ALU验证电路示意图进行连线,然后自己再先测试一些数据来判断电路连接是否正确,然后通过改变原电路的引脚接口的数据来验证74LS181型4位ALU的逻辑算术功能,然后填写表1-3

表1-3 实验一功能测试数据填写表

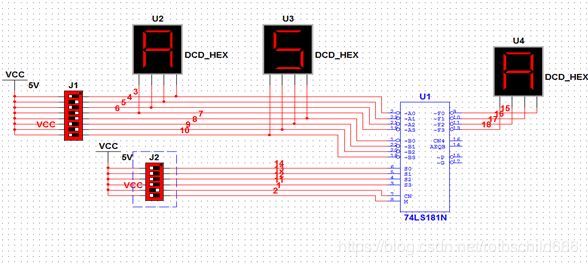

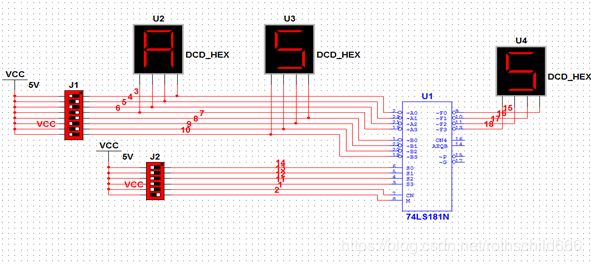

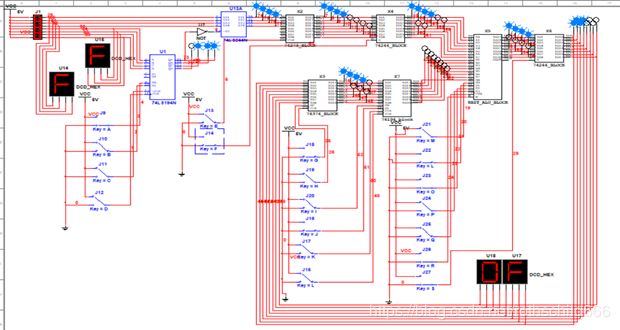

图1-1 表1-3第一组测试数据截屏(1)

图1-2 表1-3第一组测试数据截屏(2)

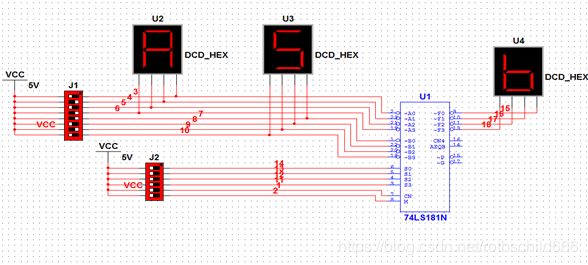

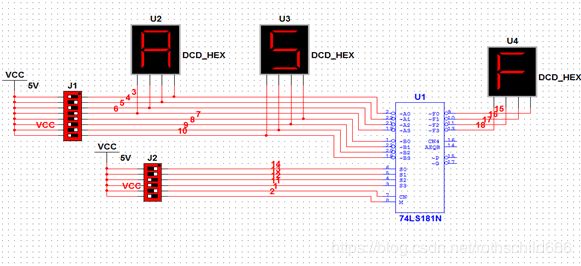

图1-3 表1-3第一组测试数据截屏(3)

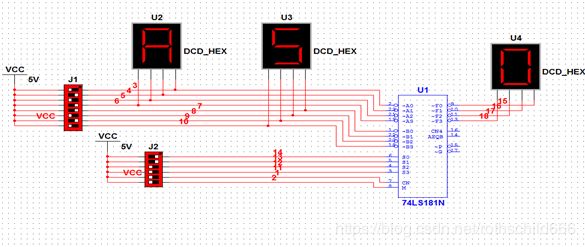

图1-4 表1-3第四组测试数据截屏(1)

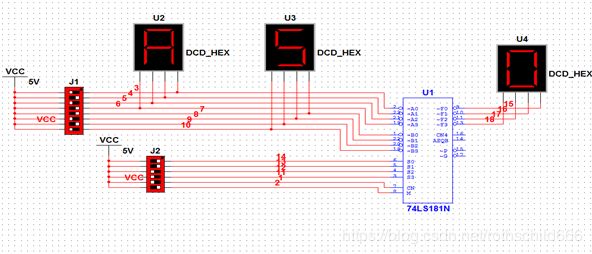

图1-5 表1-3第四组测试数据截屏(2)

图1-6 表1-3第四组测试数据截屏(3)

5、总结及心得体会:

通过使用multisim大概掌握算术逻辑单元(ALU)的工作原理,也基本熟悉了简单运算器的数据传送通路,同时也验证4位运算功能发生器(74LS181)组合功能,把书面知识和实践结合起来,对知识点了解更加深刻,理解也更加容易,所以以后还是要加强动手实践能力的锻炼。

二、实验二

1、实验名称:

运算器(2)

2、实验目的:

(1) 熟练掌握算术逻辑单元(ALU)的应用方法;

(2) 进一步熟悉简单运算器的数据传送原理;

(3) 画出逻辑电路图及布出美观整齐的接线图;

(4) 熟练掌握有关数字元件的功能和使用方法。

(5) 熟练掌握子电路的创建及使用。

3、实验原理:

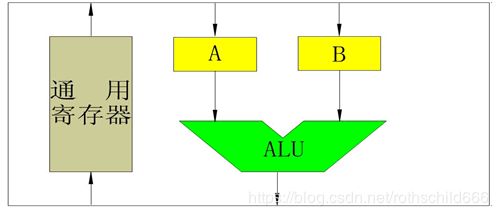

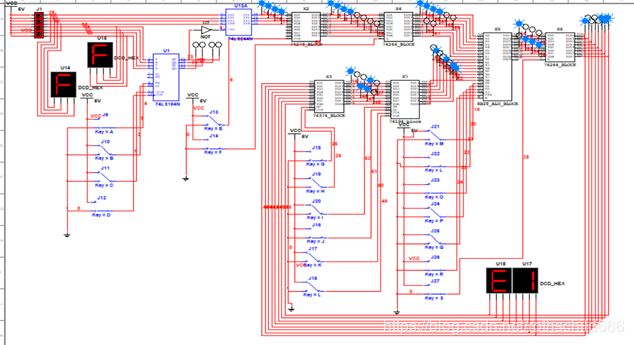

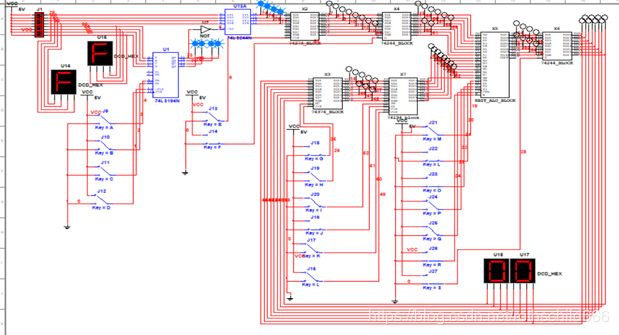

本实验仿真单总线结构的运算器,原理如图2-1所示。相应的电路如图2-2所示。电路图中,上右下三方的8条线模拟8位数据总线;K8产生所需数据;74244层次块为三态门电路,将部件与总线连接或断开,切记总线上只能有一个输入;两个74273层次块作为暂存工作寄存器DR1和DR2;两个74374层次块作为通用寄存器组(鉴于电路排列情况,只画出两个通用寄存器GR1和GR2,如果可能的话可设计4个或8个通用寄存器);众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;核心为8位ALU层次块。

图2-1 单总线结构的运算器示意图

图2-2运算器电路示意图

4、实验内容:

(1) 说明整个电路工作原理。

整个电路仿真单总线结构的运算器,完成算术和逻辑运算。

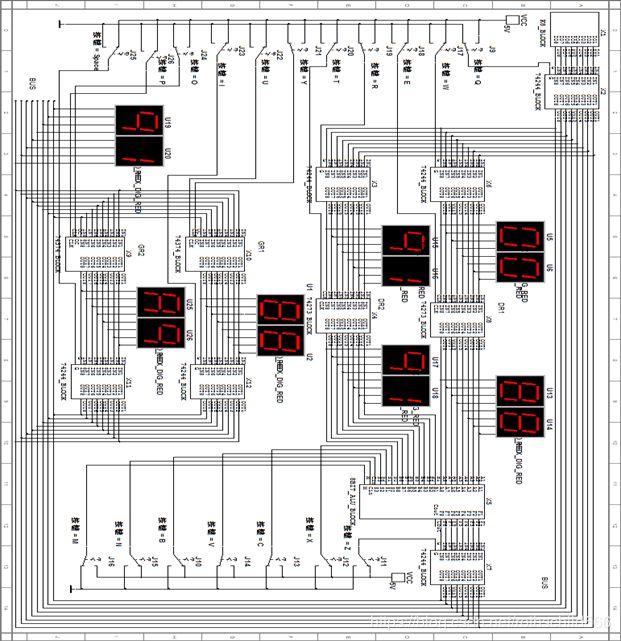

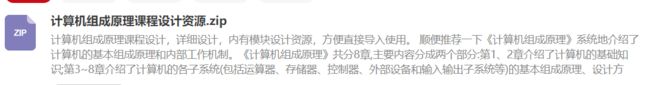

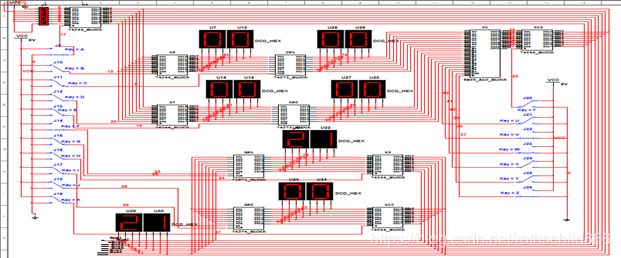

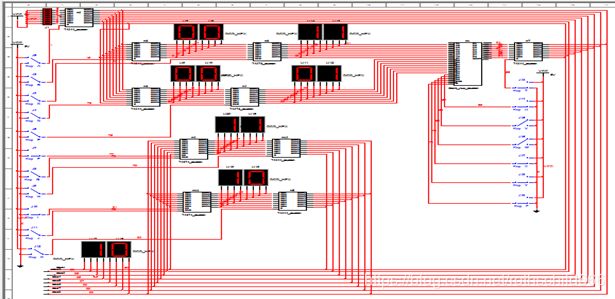

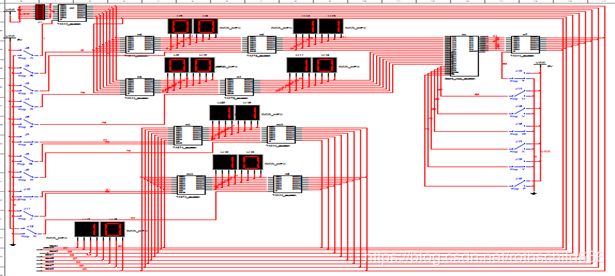

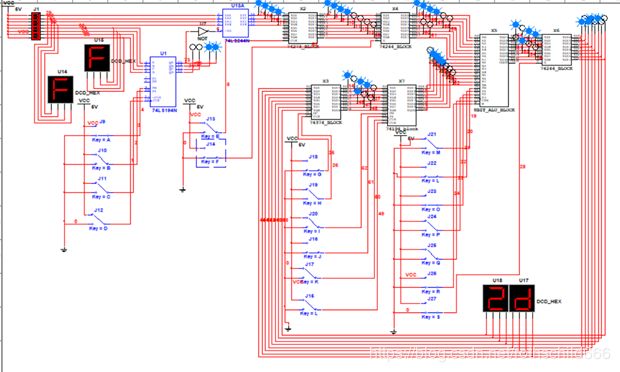

图2-3 实验二仿真单总线结构的运算器电路图

在Multisim中用“DSWPK_8”元件代替了K8层次块,DSWPK_8的八个按键用来控制数据输入的大小,左边有11个按键开关,其中J5、J2、J4、J9、J12是分别用来控制74244_BLOCK模块X2、X6、X3、X12、X5的工作情况,J3和J6分别控制74273_BLOCK模块X8的工作情况,J7和J8、J10和J11是分别用来控制74374_BLOCK模块X9、X10;右边有7个按键开关,J13是用来控制74244_BLOCK模块X7,剩下的6个按键开关是用来控制8BIT_ALU_BLOCK模块X1的工作情况比如8位运算器运算是逻辑运算还是算术运算等;更具体实验过程解释见下面。然后四个不同的模块又有不同的作用:

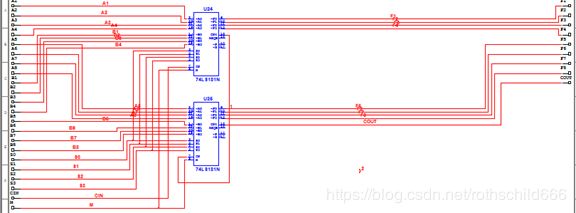

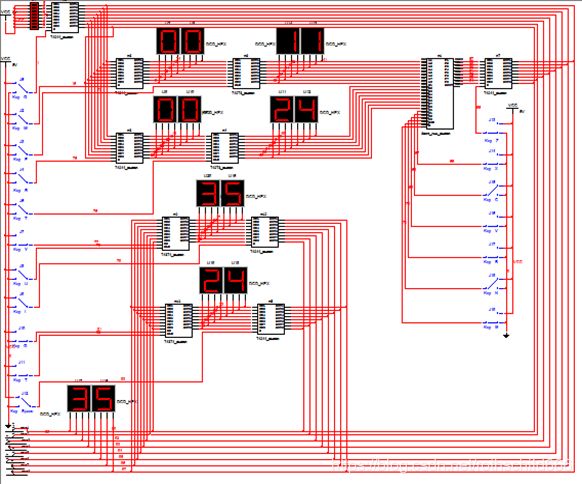

1、74244_BLOCK模块:74244_BLOCK模块,只有当控制电平G=0时,74LS244N元件开始工作。主要是起到控制隔绝电路的作用,同时也相当于控制数据的传输。

图2-4 74244_BLOCK模块电路图

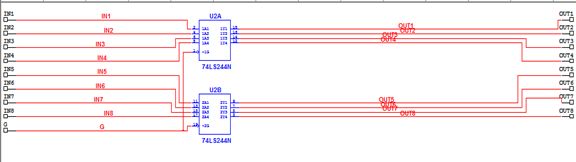

2、74273_BLOCK模块:74273_BLOCK模块,两个74273模块作为暂存工作寄存器,CLK上升沿触发,能够有效控制存储的数据是否是运算所需要的数据,尽量保证运算过程及结果的正确性。

图2-5 74273_BLOCK模块电路图

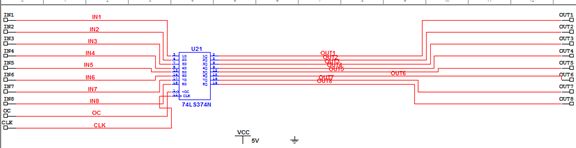

3、74374_BLOCK模块:74374_BLOCK模块,两个74374模块作为通用寄存器组,当oc为低电平时模块元件进行工作,CLK上升沿触发,能够有效控制存储的数据是否是运算所需要的数据,尽量保证运算过程及结果的准确性。

图2-6 74374_BLOCK模块电路图

4、8BIT_ALU_BLOCK模块:8BIT_ALU_BLOCK模块,8位ALU层次块,是整个电路的核心,它的工作原理和四位的ALU相似,可以用作逻辑运算和算术运算。

图2-7 8BIT_ALU_BLOCK模块电路图

(2) 说明74LS244N的功能及其在电路中作用,及输入信号G有何作用;

答:74LS244N是三态门,控制电平G=1时,起到隔绝电路的作用。控制电平G=0时,74LS244N元件开始工作。

(3) 说明74LS273N的功能及其在电路中作用,及输入信号CLK有何作用;

答:工作寄存器,其输出直接接到ALU的输入端,LCK为打入脉冲。

(4) 说明74LS374N的功能及其在电路中作用,及输入信号CLK和OC有何作用;

答:74ls374n作为通用寄存器(转送,暂存,计算),另具有三态门的作用。CLK作为打入脉冲的作用,而OC高电平为高阻态,逻辑操作不受影响。

(5) DSWPK_8产生任意数据存入通用寄存器GR1。

答:(1)DSWPK_8确定任意数(如11111111);(2)A=0(低电平),数据送总线;(3)G↑(正跳变)且F=0.该数存入GR1.

图2-8 DSWPK_8产生任意数据存入通用寄存器GR1电路图

(6) DSWPK_8产生任意数据存入通用寄存器GR2。

答:(1)DSWPK_8确定任意数(如00100101);(2)A=0(低电平),数据送总线;(3)J↑(正跳变)且I=0.该数存入GR2.

图2-9 DSWPK_8产生任意数据存入通用寄存器GR2电路图

(7) 完成GR1+GR2→GR1。

答:GR1+GR2→GR1.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2)I=0、K=0、E↑,GR2→DR2;(3)加法:S3~S0=1001B(对应XWVU四键)、Y=1、Z=0,此时结果在ALU的输出端,令T=0,结果送总线,G↑结果存入GR1.

图2-10 GR1+GR2→GR1运算电路图

(8) 完成GR1-GR2→GR2。

答:GR1-GR2→GR2.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2)I=0、K=0、E↑,GR2→DR2;(3)加法:S3~S0=0110B(对应XWVU四键)、Y=1、Z=0,此时结果在ALU的输出端,令T=0,结果送总线,J↑结果存入GR2.

图2-11 GR1-GR2→GR2运算电路图

(9) 完成GR1∧GR2→GR1。

答:GR1∧GR2→GR1.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2)I=0、K=0、E↑,GR2→DR2;(3)加法:S3~S0=1011B(对应XWVU四键)、Z=1,此时结果在ALU的输出端,令T=0,结果送总线,G↑结果存入GR1.

图2-12 GR1∧GR2→GR1运算电路图

(10) 完成GR1∨GR2→GR2。

答:GR1∨GR2→GR2.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2)I=0、K=0、E↑,GR2→DR2;(3)加法:S3~S0=1110B(对应XWVU四键)、Z=1,此时结果在ALU的输出端,令T=0,结果送总线,J↑结果存入GR2.

图2-13 GR1∨GR2→GR2运算电路图

(11) 完成GR1⊕GR2→GR1。

答:GR1⊕GR2→GR1.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2)I=0、K=0、E↑,GR2→DR2;(3)加法:S3~S0=0110B(对应XWVU四键)、Z=1,此时结果在ALU的输出端,令T=0,结果送总线,G↑结果存入GR1.

图2-14 GR1⊕GR2→GR1运算电路图

(12) GR1→GR2。(“”表示逻辑非运算)

答:~GR1→GR2.(1)A=1(屏蔽掉DSWPK_8)、F=0、H=0、B=0、C↑,GR1→DR1;(2) S3~S0=0000B(对应XWVU四键)、Z=1,此时结果在ALU的输出端,令T=0,结果送总线,J↑结果存入GR2.

图2-15 ~GR1→GR2运算电路图

(13) ~GR2→GR1。

答:(1)I=0、K=0、E↑,GR2→DR2;(2)S3~S0=0000B(对应XWVU四键)、Z=1,此时结果在ALU的输出端,令T=0,结果送总线,G↑结果存入GR1.

图2-16 ~GR2→GR1运算电路图

5、总结及心得体会:

通过使用multisim更加深入了解了算术逻辑单元(ALU)的工作原理,熟练掌握算术逻辑单元(ALU)的应用方法;进一步熟悉简单运算器的数据传送原理;画出逻辑电路图及布出美观整齐的接线图;熟练掌握有关数字元件的功能和使用方法,熟练掌握子电路的创建及使用以及掌握三态门的使用和原理。对于层次模块也有了系统的掌握,在电路连接过程中,也出现了一些问题,因为看起来比较复杂但是在耐心和细心的检查调整下,整个电路还是正常运行各种算数逻辑运算都是可以验证正确,同样也要增强自己的动手能力。

三、实验三

1、实验名称:

乘法实现

2、实验目的:

开放性实验,根据原理图实现乘法的电路设计并运行。

3、实验原理:

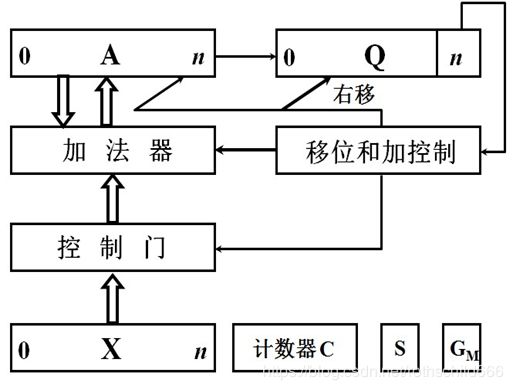

如图2-4是实现原码一位乘运算的基本硬件配置框图,根据该图用移位相加方法实现乘法,自行选择器件设计电路并运行。

图3-1原码一位乘运算的基本硬件配置

提示:用74LS181作为加法器,用74LS194作为移位寄存器;手动开关作为计数器,实现4位*4位的乘法。

4、实验内容:

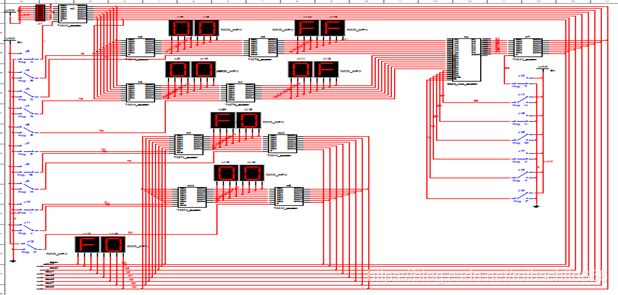

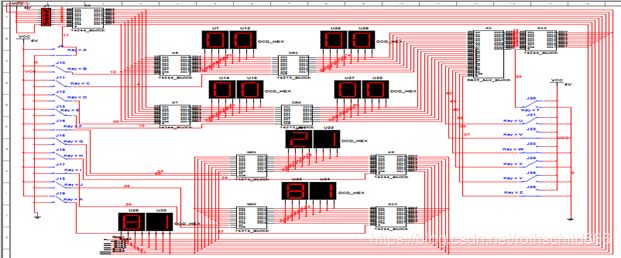

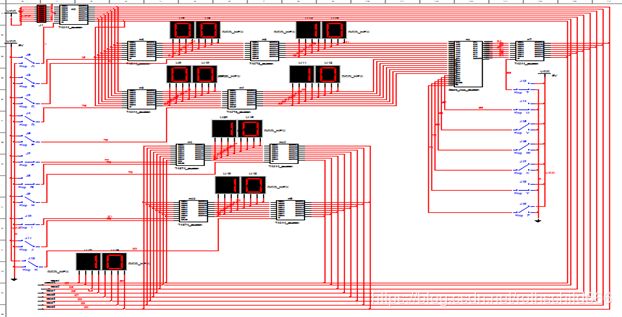

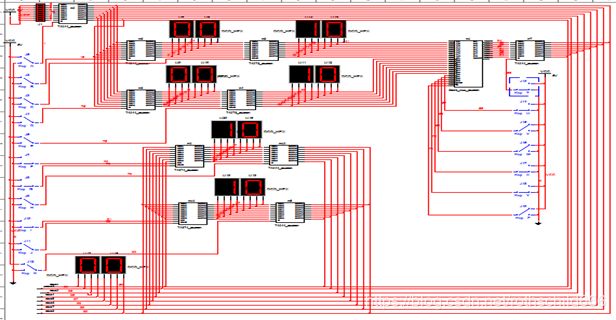

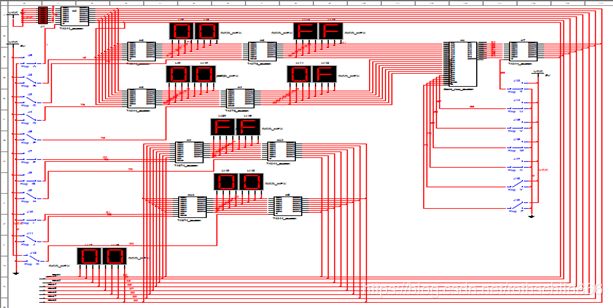

图3-2原码一位乘运算电路实现图

原码一位乘运算电路实现图:U14表示被乘数,U15表示乘数,由DSWPK_8输入乘数给74LS194控制三态门,并间接控制被乘数向74LS244的输入。存在数字寄存器74273中。然后将部分积结果存在74374中,利用移位寄存器X7将部分积的结果左移。后用移位寄存器U1将乘数右移,不断重复4次,直到结果输出。

图3-3原码一位乘F和F运算电路实现图(1)

原码一位乘F和F运算电路实现图(1)说明:我们首先用调控DSWPK_8使它输出两个F分别作为乘数和被乘数,然后74LS194三态门S0、S1为高电平时,将乘数传输到74LS194三态门。

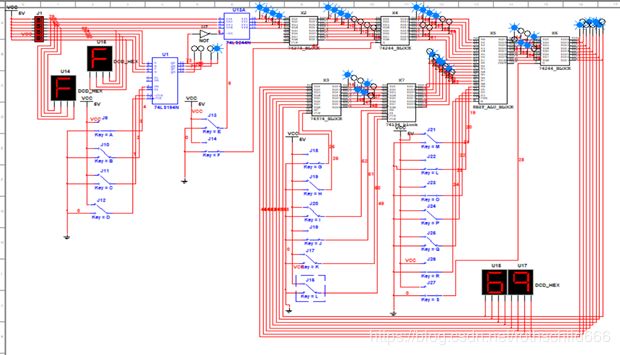

图3-4原码一位乘F和F运算电路实现图(2)

原码一位乘F和F运算电路实现图(2)说明:调节74LS194三态门S0为低电平、S1为高电平时,操作74LS194三态门中的CLK进行上升沿调节对乘数进行右移,当右移结果为1时,调节74244_BLOCK中的G=0,让被乘数能够传输过去到8BIT_ALU_BLOCK中到时和部分积进行加法运算。

图3-5原码一位乘F和F运算电路实现图(3)

原码一位乘F和F运算电路实现图(3)说明:操作74374_BLOCK模块X3中的CLK进行上升沿调节,使计算后的结果传输更新原来的部分积。然后操作74194_BLOCK将S0、S1为高电平,将部分积数据传输过来,然后又将S0为高电平、S1为低电平时,原部分积的数据进行左移。当乘数右移为1时,调节74244_BLOCK中的G=0,否则G=1。

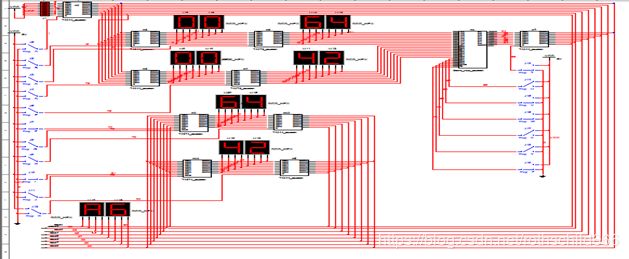

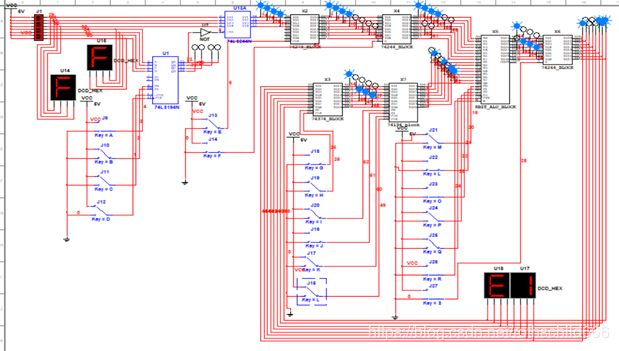

图3-6原码一位乘F和F运算电路实现图(4)

原码一位乘F和F运算电路实现图(4)说明:重复之前上述的步骤,乘数不断右移,右移的数据为1时,部分积和被乘数进行一次相加,然后进行一次左移。

图3-7原码一位乘F和F运算电路实现图(5)

原码一位乘F和F运算电路实现图(5)说明:到运算的最后,乘数的数据全部移完时,这时候部分积之更新最后计算的数据不再进行左移。

5、总结及心得体会

这个实验主要是练习补码一位乘的大致过程,十分考验我们对于补码一位乘的理解和思考思路,但由于模块限制只能支持整数运算。通过本次实验,我对于74LS194、74LS244等一些芯片有了更深的理解,同时在设计过程中也需要细心耐心,切勿急躁,否则连错会导致一系列错误而且还不容易找出来比较费时费力,整体收获还是比较大的,动手能力也得到加强。