FPGA开发流程——小白入手

良好的文件夹设置以及工程管理是学好 FPGA 设计的基础,在学习之初就应建立良好的习惯。

上图中,prj 为工程文件存放目录;rtl 为 verilog 可综合代码存放目录;testbench 为测试

文件存放目录;img 为设计相关图片存放目录;doc 为设计相关文档存放目录;prj 文件夹下

还建立了子文件夹 ip,用于存放 Quartus Prime 中生成的 IP 核文件。

建立工程

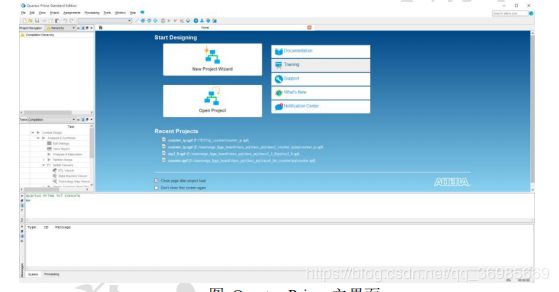

安装好quartus II 之后,打开软件

第一步,新建工程:单击New Project来启动一个工程向导

第二步:选择工程所在路径

注意:路径尽量选择英文路劲,防止报错

第三步:添加设计文件,若没有,可直接点击NEXT。

第四步:选择器件,选择完直接点Finish

设计输入

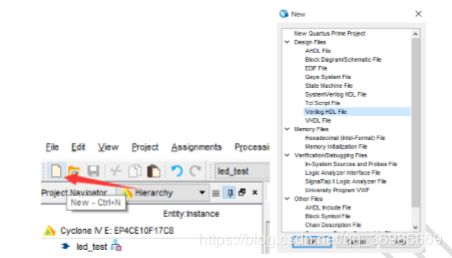

第一步:工程建立完成后,需要为工程添加新的设计文件,单击 File→New→Verilog HDL File,或者工具栏中的 New,此处选择 Design Files 中的 Verilog HDL File。

第二步:输入设计代码,并以led_test.v命名保存到工程对应的rtl文件夹下。

module led_test(a,b,key_in,led_out);

input a;

input b;

input key_in;

output led_out;

assign led_out=(key_in==0)?a:b;

endmodule

分析与综合

单击工具栏中的 Start Analysis & Synthesis 来进行分析和综合。如在设计过程有错误的 地方,在分析和综合后会提示 Error 或者 Warning,需针对不同情况进行修改。

全编译后可以在 RTL Viewer 中可以看到硬件逻辑电路。即一个二选一选 择器,符合设计预期

功能仿真

为了验证以上逻辑设计是否成功,在直接下载到开发板观察现象之前需编写激励文 件,此处再新建一个.v 文件并输入以下内容。并以 led_test_tb.v 保存到工程对应的 testbench 文件夹下。并再次进行分析和综合查看是否存在语法设计错误。

`timescale 1ns/1ps

module led_test_tb;

//激励信号定义,对应连接到待测试模块的输入端口

reg signal_a;

reg signal_b;

reg signal_c;

//待检测信号定义,对应连接到待测试模块的输出端口

wire led;

//例化待测试模块

led_test led_test0(

.a(signal_a),

.b(signal_b),

.key_in(signal_c),

.led_out(led)

);

//产生激励

initial begin

signal_a = 0;

signal_b = 0;

signal_c = 0;

#100;//延时 100ns

signal_a = 0

;signal_b = 0;

signal_c = 1;

#100;

signal_a = 0

;signal_b = 1;

signal_c = 0;

#100;

signal_a = 0;

signal_b = 1;

signal_c = 1;

#100;

signal_a = 1;

signal_b = 0;

signal_c = 0;

end

endmodule

设置仿真脚本

单击标题栏的 Assignments→Settings→Simulation,查看仿真工具以及语言是否与之前 的设置一致,否则根据实际使用情况进行相应的修改,如图 所示。选中 Compile test bench 单击 Test Benches 后点击 OK。

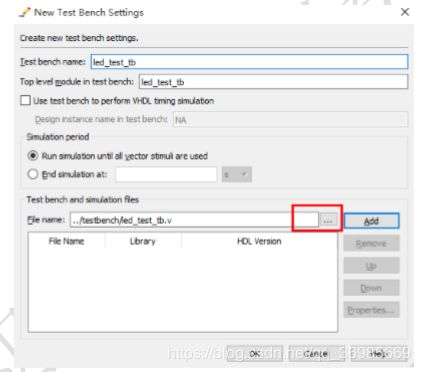

点击 New,弹出如图 2-11 所示的 Test Bench 设置文件对话框,找到已经编写好的激励 文件,单击 Add。在 Test bench name 中填写对应的激励名称。点击 OK 后回到主界面。

单击 Tools→Run Simulation Tool→RTL Simulation 来进行前仿真也就是常说的功能仿真。

如出现下图对话框,即仿真软件路径报错,可在 Tools→Options→EDA Tool Options 设置对应的仿真软件的路径即可。

至此,即可在仿真软件modelsim中看到如图2-15的波形文件,可以看出符合设计预期, 当 key_in 等于 0 时 led_out 等于 a,当 key_in 等于 1 时 led_out 等于 b。即功能仿真通过。

综合与布局布线

点击 Quartus II主界面的 Start Compilation,进行综合&布局布线。布局布线过程中 如遇出错,应根据编译错误信息具体修改。

时序仿真

点击 Tools→Run Simulation Tool→Gate Leval Simulation 或者在工具栏点击 Gate Leval Simulation 进行后仿真,也就是门级仿真。

弹出选择时序模型对话框,可针对相应情况具体选择。此时可选择第一个时序模型: 慢速工作、环境温度为 85℃、内核供电 1.2V 的情况进行仿真。

时序仿真完成后,可以在 Modelsim 的波形窗口中看到图 2-19 的时序仿真波形。从波 形中发现与之前的功能仿真相比有了一些差异,如:存在不希望存在的脉冲、且在 200ns 时,led 相对输入信号有一定时间的逻辑延时。

IO分配以及生成配置文件

IO 分配其方法不唯一,常用的有三种。在标题栏中 Assignments—Pin Planner 或者直 接单击工具栏的 Pin Planner 进行 IO 分配,同时也可通过编写 Tcl 文件的方式来实现引脚分 配.此处需针对不同板卡进行不同的设置

注意:在分配好引脚后,仍需再进行一次全编译才能使引脚分配生效

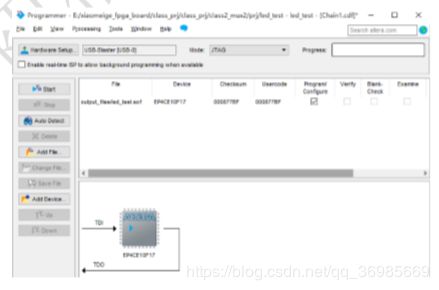

配置 FPGA 下载

单击工具栏中的 Programmer,弹出以下对话框。确认连接好下载器并在 Hardware Setup 中选中 USB-Blaster 以及被下载的.sof 文件后,单击 Start 即可将设计好的逻辑电路下 载到开发板中。