两层板如何做阻抗控制呢

两层板如何做阻抗控制呢?

这个问题可能很多人都会碰到,有的人在此等需要做阻抗控制的情况都选择做多层板。诚然,多层板在阻抗控制,EMC等等方面都有着天然的优势。然而,在价格上和周期上,两层板就有着绝对优势了。

对于成本非常敏感而又不是太复杂的产品,尽管对于我们硬件工程师而言,有一堆的理由要求使用多层板。然而在面对毛都不懂的老板“别人能做,你为什么不能做?”这个问题时只得低下我们高傲的头颅。

好,那下面就来说说如何做的问题。

两层板做阻抗控制

先大致说下特征阻抗是怎么来的?信号在导线中传播的时候,会有电流的存在,那么就有电流返回路径,一般参考平面构成返回路径,特征阻抗就是电压大小与电流大小的比值。因此,阻抗控制的关键就是要有参考平面构成电流返回路径。

通常,多层板都有参考平面,两层板是没有专门的参考平面的。强行参考会因为板厚太厚导致计算出的走线宽度非常宽而无法使用。

所以,我们只能给“做”一个电流返回路径出来,当然了,这个路径必须均匀,保证特征阻抗不变。这个方法就是包地,也就是共面阻抗。

共面阻抗与哪些因素有关

我们知道,特征阻抗的公式是分布电感除以分布电容,然后开根号。

因此,共面阻抗的大小与走线宽度,包地间距的关系很大。包地间距越小,走线越宽,则分布电容越小,阻抗越大。

几种常见的共面阻抗控制

很多人都在嘉立创打板,并且嘉立创也公布了自己常规的板材参数,所以我就以嘉立创为例子了。

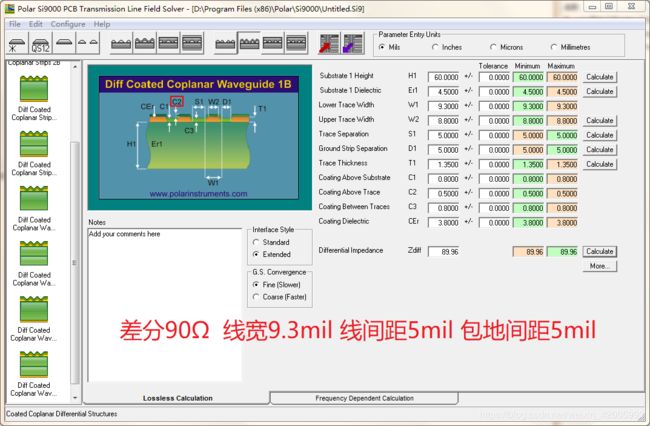

几种阻抗参数如下表,是使用SI9000工具计算得出的

需要说明的是,本人实际在嘉立创做过含有USB2.0,USB3.0,HDMI等等含有差分90Ω和100Ω的信号的两层板,功能是没有问题的。虽然没有做过阻抗测量,但是实测HDMI信功能(PCB板按上述走线100mm左右,接口外接HDMI线缆长度5m,信号为4K@30fps)功能是OK的,想来阻抗应该是相差不多的。

以下是SI9000对应的阻抗截图

当然了,如果去其它家制板,对应参数需要相应调整下。

需要注意,可以看到,单端50Ω阻抗线宽为23mil,这么宽的线几乎是无法接受的,那么如何处理需要50Ω阻抗的信号线呢?那么我们来看看一个华为海思的两层板案例。

海思两层板阻抗案例

案例来源于华为海思机顶盒HI3798MV100方案,含有DDR3,网口,USB3.0,HDMI等等需要做阻抗的信号。下面先看看其SDK里面的硬件设计指南里面的阻抗要求。

从表里面,HDMI差分线,DDR差分线,USB差分等等要求都跟标准一样,但是DDR单端走线4层板要求做50Ω,而2层板表示要优先控制线宽和线距,其对应阻抗为60-70Ω。

为什么2层板和4层板的阻抗要求会出现双标呢?

关于这个问题,我思考了一下,主要原因还是因为2层板共面阻抗做50Ω要求的线宽很宽,达到20多mil,这个是没法拉线的,因此只能放开阻抗要求,允许一定的信号反射的。从这里看,2层板做阻抗还是有一定的局限性的,最好还是做4层板,信号质量更好。

那么实际50Ω做成了60-70Ω对信号有多大的影响呢?

这个问题海思自然不会告诉我们,它只会让咱抄他们的demo走线,按照的它的要求去做板功能就不会有问题,如下图:

但是作为爱钻的咱,显然还是想看看信号到底是啥样子的,正好上期文章我们用Geogebra做的信号反射模型就派上用场了。

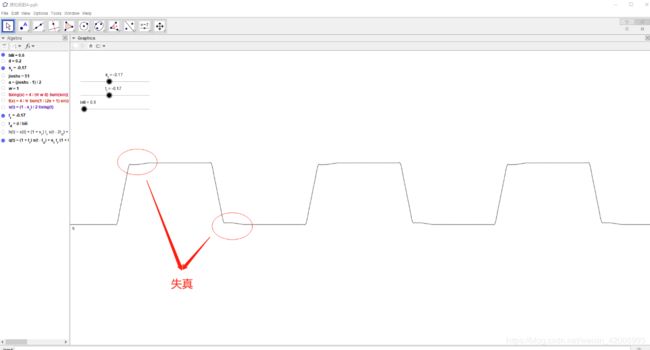

Geogebra相关参数如下:

海思的PCB的DEMO中DDR走线最长1000mil左右,对应的时延是167ps,实际工作中DDR3的时钟频率为800Mhz,查询DDR3协议,对应上升沿要求最大为100ps,可以计算得上升沿与信号走线延时的比值为bili=0.6。

另外,阻抗实际为70欧姆,那么源端反射系数为Sr=(50-70)/(50+70)=-0.17

同理,终端反射系数为Tr=-0.17

代入到Geogebra模型中,看到波形情况如图:

从图上,我们就能直观看到失真确实不是很严重。

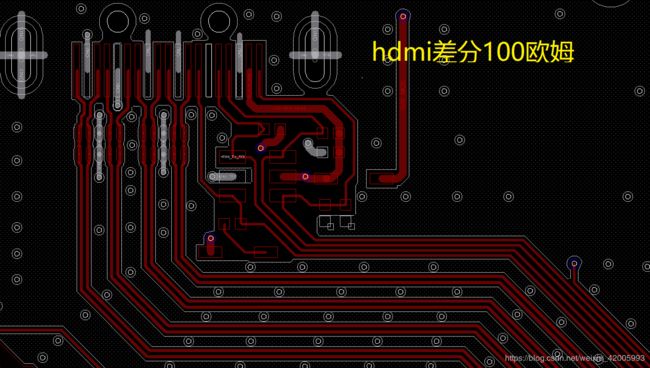

下面看看PCB实际走线情况

注意,上图是需要控50Ω单端地址线走线,不是差分线,可以看到,其走线并没有2面都包地,只是包了一面,这应该是因为地址线太多,没法两面都包地,实际阻抗模型在SI9000里面也没有找到,所以并不清楚阻抗到底是多少,也不知道该如何计算。既然海思SDK文档里面说了阻抗是60-70Ω,姑且是相信是这样吧,汗。。。。

下面是差分100Ω和90Ω

可以看到,这些包地都是很连贯的,中间没有断,这很重要。如果断了,就相当于4层板信号线跨分割走线了。

本文小结

---两层板阻抗控制是通过包地来实现的,即共面阻抗

---两层板50Ω单端阻抗不好控制,差分90Ω,100Ω相对容易

---两层板阻抗控制包地是很重要的,包地间距要严格要求,并且需要连贯

文件共享:需要查看海思的2层板阻抗设计文档,以及PCB的demo板的源文件,还有Geogebra的源文件,可以扫描下方二维码,关注微信号,在微信号里面回复“两层阻抗”,即可获得下载链接。