Vivado HLS(2015.4版本)使用教程(zynq 7010系列)

1.新建一个项目。

第一步:新建

第二步:核心算法文件。(可以跳过该步骤)

第三步:测试激励文件添加。(可以跳过)

第四步:解决方案和开发板型号选择。

2.编写程序文件。(一般source文件(.h和.cpp)存到新建的src文件下,testbench文件(.cpp)存放到新建的test文件下。)

3.程序编写完成后,进行C仿真(simulation)。

出来一个界面,直接默认跳过即可。

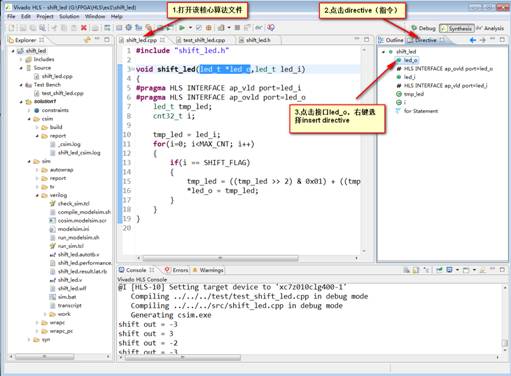

4.对接口进行约束。

第一步:进入核心算法文件。(比如:shift_led.cpp)

第二步:进行插入指令约束。

对下面界面进行配置。(选择源文件就是对所有文件起限制作用,放到指令文件里就是选择该指令文件时才起作用。)

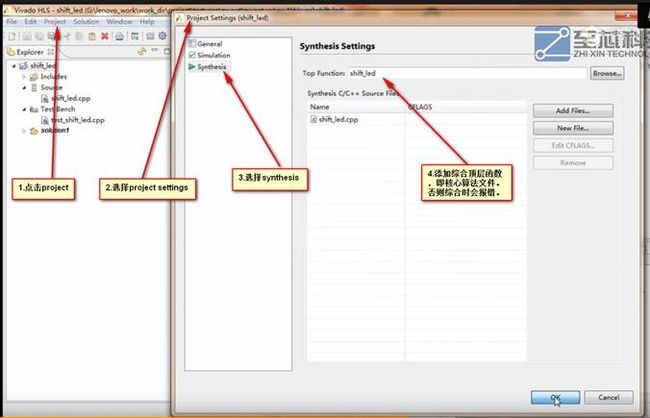

5.进行C综合(synthesis)。

第一步:前面没有设置核心文件,这里需要添加上去,否则综合(synthesis)时,会报错。

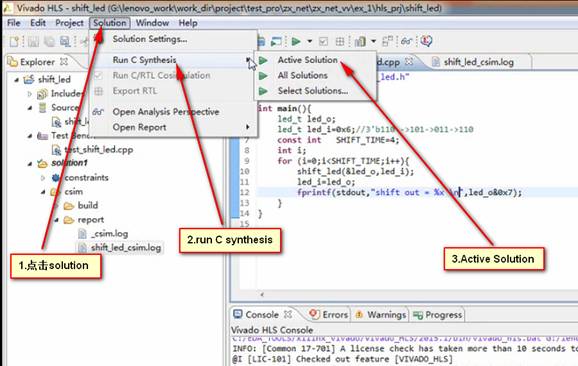

第二步:进行C综合(synthesis)。该步骤就是从C程序往Verilog程序(也称为RTL级代码)转。

6.进行C/RTL联合仿真。(生成RTL级testbench文件,并直接进行激励,生成波形文件。)

配置下面的页面:

7.“solution”–"Export RTL"即可从HLS生成vivado下可用的IP核。(如果想看modelsIM的仿真结果,可以用modelsim到项目目录下查看,例如:

G:\FPGA\HLS\ex1_vv\shift_led\solution1\sim\verilog\shift_led.wlf)