Vivado HLS设计流程及实例演示

引言

Vivado HLS给FPGA设计提供了一种新的方式,可以让软件工程师直接介入FPGA开发,加速了各种算法在FPGA上实现和应用的进程,特别是在如今人工智能大潮流下,Vivado HLS可以加速各种机器学习,深度学习算法在FPGA上的实现,加速算法落地和产业实现。

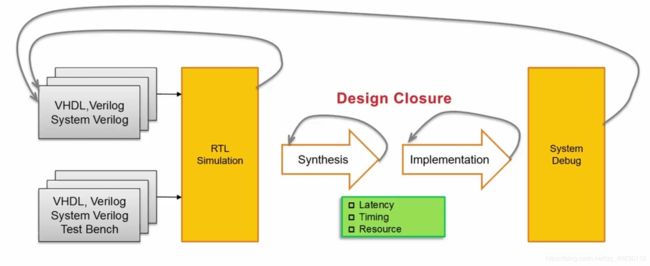

1、传统的RTL设计流程

传统用于FPGA设计的方法都是基于RTL描述的,RTL即基于Verilog/VHDL等硬件描述语言直接对所需要实现的硬件进行描述,然后生成相应的硬件电路,基本流程如下图所示:

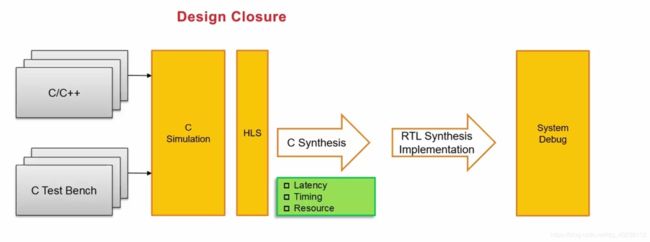

2、基于C/C++的Vivado HLS设计流程

基于C/C++的Vivado HLS设计流程采用C/C++高级程序语言进行FPGA开发,可以使软件工程师直接介入FPGA硬件开发,可以加速各种应用落地,基本流程如下所示:

在Vivado HLS中与在Vivado中类似,具体的设计流程有添加C源文件,添加C测试文件,C仿真,C综合,C/RTL联合仿真,导出RTL等几个步骤,基本流程如下图所示:

3、Vivado HLS设计流程实例讲解

在开始实例讲解之前,我们先介绍一下我们实例中需要的几个源文件。为简单起见,本实例主要实现一个简单的数组加法。

顶层文件:VectorAdd.c,此文件为设计的顶层文件,并且一个Vivado HLS只能有一个顶层文件,一个顶层文件中只能包含一个函数,如果需要调用其他子函数的话,可以再其他文件中定义了之后在顶层文件中调用。

#include "VectorAdd.h"

void VectorAdd(data_t A[N],data_t c,data_t B[N])

{

unsigned int i;

myloop:

for(i=0;i头文件:VectorAdd.h,此文件为头文件,主要为一些宏定义和函数声明。

#define N 5

typedef int data_t;

void VectorAdd(data_t A[N],data_t c,data_t B[N]);

测试文件:VectorAdd_tb.c,此文件为整个工程的测试文件,Vivado HLS中默认main函数为测试函数,其中main函数必须是有返回值的函数,其中定义返回1为测试失败,返回0为测试成功。

#include "VectorAdd.h"

#include "stdio.h"

int main()

{

data_t A[N]={-4,-3,0,1,2};

data_t c=5;

data_t B[N]={0};

data_t RefB[N]={1,2,5,6,7};

unsigned int i=0;

unsigned int errcnt=0;

VectorAdd(A,c,B);

for(i=0;i0)

{

printf("test failed\n");

return 1;

}

else

{

printf("test pass\n");

return 0;

}

}

介绍完所需的几个文件后,下面我们开始一步一步的介绍如何创建工程和工程设计。

第一步:创建工程

第二步:添加顶层文件

第三步:添加测试文件

第四步:创建solution和选择芯片类型

第五步:C仿真

![]()

第六步:C综合

![]()

综合完成之后,可以查看资源,时序,延时等报告

综合完成之后生成了Verilog和VHDL代码。

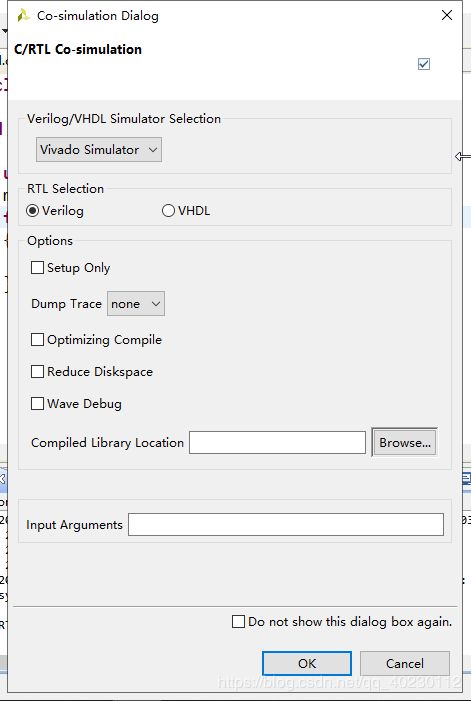

第七步:C/RTL协同仿真

![]()

C/RTL协同仿真后可以查看相应的RTL仿真波形。

![]()

第八步:导出RTL

![]()

至此,所有的流程全部走完。

最后推荐大家观看一个Vivado HLS相关的视频,非常有作用,附上链接。

https://www.bilibili.com/video/BV1J5411t7uE?from=search&seid=15422041471200940090