FPGA学习笔记(一)—— 模块和端口

笔记基于解决问题的思路来书写;

1,什么是自上而下和自下而上的设计方法?

简单来说,自上而下:从顶层模块开始,对需要的模块一步一步往下分解,直到分解到无法再分解的基础模块

自下而上:从所需要的功能模块开始搭建,比如需要一个park模块,我就从最基本的乘法器开始搭。

一般而言,从上而下是,逻辑思路比较多,对各个模块之间的联系处理,而自下而上,是生产这些小的模块,把这些能够处理的信息流通过端口放出来。

2,什么模块呢?

模块就是一个基本的功能块,它可以是一个简单的触发器,也可是一个PARK。通过输出输出的接口被高层的模块调用。

3,什么是模块实例?和模块有什么区别?

模块的声明就类似与一个模板,比如一个处理数据的子函数,而在FPGA中,使用这个模板就可创建实际的对象。

而在模块被调用的时候,Verilog 会对这个模板创建一个唯一的模块对象,它具有独自的名字,和输入,输出。

而从模板到实际对象的这个过程就叫实例化,创建的对象叫做实例。

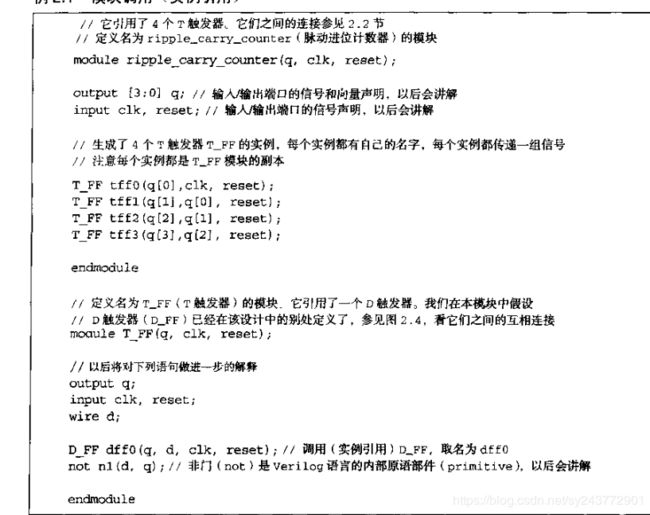

比如下面这个 ripple....它这个模块,通过内部的语句 T_FF 定义了4个触发器实例 tff0 tfff1 tff2 tff3,

这三个实例有自己的名字,还有输入输出。

注:模块内不可再定义模块

4, 深入探究模块内部,模块是由哪几个部分组成的?

变量声明(input,output,parameter)

数据流语句(assign , wire)

低层模块实例,(同3中模块实例)

行为语句块(always 和 initial 语句),

任务和函数 (这就太多了)

5,什么是端口?

模块的外部环境交互的接口,对外部环境而言,他的内部是不可见的,就相当于电路板里面的元器件芯片,我们只对他输入和取他的输出。

6,端口列表是什么?

端口列表就是一系列模块与外部环境交互的管脚,它是两部分的一个连接装置,一部分位于模块内部,一部分位于模块外部,端口外部是输出还是输入需要在模块内部进行端口声明。它有自己的顺序,还有自己的名称。

7,端口连接规则是什么?

当一个模块在另外一个模块内被调用的时候,

输入端口:从模块内部讲,必须是线网数据类型,因为在内部需要处理,只能是一个类型

从模块外部讲,可以是reg数据类型也可以是线网类的,这是为了能够接受各种数据类型

输出端口:从模块内部将,可以是reg数据类型也可以是线网类的,是因为可以选择输出的类型

从模块外部讲,必须是线网数据类型,因为模块输出的数据必须是线网类型,便于顶层的reg数据和各个模块之间数据区分。

内外两个部分最好具有相同的线宽

8,端口连接的方式是什么?

第一:顺序连接方式,严格对应调用模块的端口位置顺序,输入对应输入的位置,输出对应输出的位置,

第二:命名端口连接,这是用在大型的设计中,模块端口太多,一一对应太难,这样端口是按照名字连接,而不是顺序位置。

语句: fulladd4 fa_byname( .cout(COUT) , .sum(SUM) , .b(B) , .cin(CIN) , .a(A),);

这些COUT , SUM ,B, CIN ,A就是他们的名字,

9,什么是层次命名?

由根模块名以及其中调用的模块实例名次序组成,比如根模块stimulus的Qbar端口,他的子模块由m1,m1的子模块为n1,那么这个端口信号为 stimulus.m1.n1.Qbar