FPGA学习嵌入式硬件最小系统搭建(一)(NIOS II处理器设置)

FPGA学习嵌入式硬件最小系统搭建(一)(NIOS II处理器设置)

本期学习目的:利用NIOS II系统点亮LCD1602屏及5.7寸LCD(8080接口)。

前言概述

上篇文章介绍了嵌入式硬件系统概述,并提到了基于FPGA的嵌入式系统是能够充当微处理器的系统,那么一个未处理器系统它需要哪些器件呢?

首先是最核心的MCU处理器,因此Altera就提供了一个软核处理器NIOS核,该系列软核是32位RISC嵌入式处理器,具有超过200DMIP的性能,手册上列举了一大堆优势,具体详见手册。

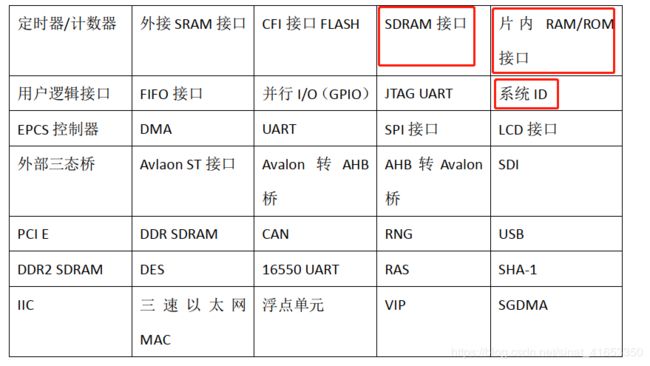

这里最核心关键的就是Altera提供了NIOS II开发包,里面包含了一套通用的外设和接口库,部分IP和接口如下表所示,具体资料详见《Embedded Peripheral IP User Guide》手册。

而且用户还可以自定义自己需要的具有特殊要求外设。

因为本期学习中NIOS II开发包中就存在LCD1602的组件IP核,因此就不需要自定义IP核了,在点亮LCD1602后将会点亮5.7寸大屏,因此在那里将会重点学习如何去自定义个人专属的IP核。

NIOS II 最小系统开发流程

首先先建立工程,然后直接打开Qsys菜单,老版Quartus显示为SOPC Builder。

然后可以看出Qsys整体页面布局,在左边就是组件IP核库,右边空白部分就是我们要搭建最小系统的区域,实际上搭建最小系统,就是调用组件IP核库里的器件,然后将这些器件连连线,分配一下时钟和地址等等操作。

NIOS软核处理器介绍

在组件库搜索NIOS会出现NIOS processor组件,

【core Nios II】

我们先将器件首页需要配置的首页编好序号。

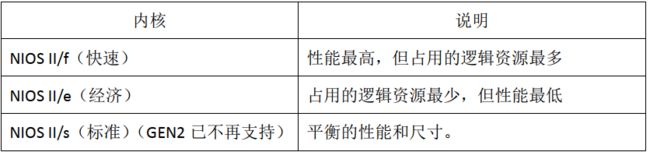

先从【select a nios ii core】【序号2】开始介绍:这里列举了Nios II系统的三种内核及特性

这里选择NIOS II/f,默认即可。

【序号3】就是Hardware Arithmetic Operation即硬件算术运算,这里可以选择嵌入式乘法器和逻辑元素两个选项。

还可以选择是否勾选Hardware divide硬件除法器。

【序号4】代表的是复位向量【Reset Vector】

上图看出该复位向量设置有3个选项。

查阅手册得知,复位向量其实是在为系统选择哪一个非易失性存储模块重置代码。

【序号5】表示异常向量【Exception Vector】

结合手册解读出该设置异常向量存储器列表是选择了异常向量存储器模块,例如在典型的系统中,为异常代码选择一个低延迟内存模块。

【序号6】表示是否启用“包括MMU”,该设置会将Nios II MMU包含在Nios II硬件系统中。

但是在手册备注中一般不选择启用MMU,除非操作系统(linux系统)要求,因此一般我们也不需要选择设置。

【Caches and Memory Interfaces】【缓存和内存接口】

该页包括指令缓存和数据缓存的设置,

【Instruction Master】

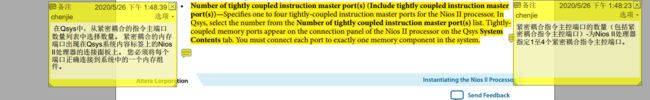

下面两张图片介绍了了Instruction master的三个设置项主要功能和如何配置。

【Data Master】

在【Data Master】有6个选项,含义分别如下:

Omit data master port---------从Nios II处理器中删除Avalon-MM数据主端口。 仅当“数据缓存”设置为“无”并且紧密耦合的数据主端口的数量大于零时,才能成功删除该端口。尽管Nios II处理器可以完全在紧密耦合的内存中运行,而不需要Avalon-MM指令或数据主机,但是,如果省略Avalon-MM指令或数据主机,则无法进行软件调试。

data cache---------指定数据缓存的大小。 有效大小为512字节至64 KB,或无。

根据数据缓存指定的值,又有以下选项设置:

data cache line size---------有效大小为4字节,16字节或32字节

Burst transfers---------Nios II处理器可以使用突发传输来填充其数据高速缓存行。 通常,当处理器数据存储在DRAM中时,启用处理器数据总线上的突发,而当处理器数据存储在SRAM中时,禁用突发。

向DRAM突发通常可以改善内存带宽,但可能会消耗额外的FPGA资源。 请注意,启用突发后,对从站的访问可能会通过其他硬件(称为突发适配器)进行,这可能会降低fMAX。

仅对于大于4个字节的数据高速缓存行启用突发。 对于16字节的行大小,突发长度为4;对于32字节的行大小,突发长度为8。 数据高速缓存突发始终在高速缓存行边界上对齐。 例如,对于32字节的Nios II数据高速缓存行,对地址8的高速缓存未命中会导致具有以下地址序列的突发:0、4、8、12、16、20、24和28。

Number of tightly coupled data master port(s) (Include tightly coupled data master port(s))---------为Nios II处理器指定1-4个紧密耦合的数据主端口。 在Qsys中,从“紧密耦合的数据主端口的数量”列表中选择数字。 紧密耦合的内存端口出现在Qsys系统内容标签上的Nios II处理器的连接面板上。 您必须将每个端口正确连接到系统中的一个内存组件。(跟【Instruction Master】设置一致。)

【Advanced Features Tab】【高级功能选项卡】

该页是NIOS II processer高级功能选项卡,可以启用Nios II处理器的特殊功能。一般也没管过,具体有啥高级功能自行查阅.

【MMU and MPU Settings】该页设置选项卡用于Nios II处理器上配置MMU和MPU。 在简易最小系统中默认即可。

【JTAG Debug Module】

可以看出JTAG Debug Module有四个等级,而且不同级别的调试消耗不同的片上资源。

由于SDRAM及RAM等存储器未设置,因此在最小系统开始选好NIOS II处理器后,选项设置默认即可,等后期存储资源添加后再来设置。