期末嵌入式复习 - 20190703

第1章 嵌入式系统概述

嵌入式系统基本概念

嵌入式系统的组成

嵌入式处理器

嵌入式操作系统

嵌入式应用软件

1 嵌入式系统基本概念

1)嵌入式系统的定义

2)嵌入式系统与PC的区别

3)嵌入式系统与单片机系统的区别

4)嵌入式系统的特征

5)嵌入式系统的应用

1)嵌入式系统的定义

计算机工业的分类

传统分类:按照计算机的体系结构、运算速度、结构规模分为大型计算机、中型机、小型机和微型计算机,并以此来组织学科和产业分工,这种分类沿袭了约40年。

现代分类:按计算机的嵌入式应用和非嵌入式应用将其分为通用计算机和嵌入式计算机。通用计算机即通常所说的个人计算机(PC),嵌入式计算机即是指嵌入式系统。

1)嵌入式系统的定义

IEEE(国际电气和电子工程师协会)定义:

嵌入式系统是“用于控制、监视或者辅助操作机器和设备的装置”(原文为devices used to control, monitor, or assist the operation of equipment, machinery or plants)。

1)嵌入式系统的定义

嵌入式系统的定义

嵌入式系统是嵌入到对象体系中的专用计算机系统。

微波炉、空调、小汽车、数码相机等内部都是由一个计算机系统来控制的,计算机系统嵌入在其中。

嵌入式系统是微波炉中的计算机系统

微波炉是一个嵌入式系统

一、嵌入式系统简介

嵌入式系统的基本概念

嵌入式系统的全称是嵌入式计算机系统

(Embedded Computer System)

一般定义 :

嵌入式系统是以应用为中心、以计算机技术为基础,软硬件可剪裁,对系统的功能、可靠性、成本、体积、功耗等有严格要求的专用计算机系统。

2)嵌入式系统与PC的区别

嵌入式系统的硬件和软件都必须高效率地设计、“量体裁衣”、去除冗余,力争在较少的资源上实现更高的性能;PC的软硬件都很庞大、臃肿。

嵌入式系统的目标代码通常是固化在非易失性存储器(ROM,EPROM,EEPROM,FLASH)芯片中;PC放在硬盘中。

2)嵌入式系统与PC的区别

嵌入式系统使用的操作系统一般是实时操作系统(RTOS),系统有实时性约束;PC无此限制。

嵌入式系统需要专用开发工具和方法进行设计——交叉开发;PC直接开发。

通用PC软、硬件技术高度垄断;嵌入式系统技术不容易被垄断。

PC为通用计算机系统,嵌入式系统为专用计算机系统

嵌入式系统 PC机

嵌入式系统一般是专用系统,而PC是通用计算平台

嵌入式系统的资源比PC少得多

嵌入式系统软件故障带来的后果比PC机大得多

嵌入式系统一般采用实时操作系统

嵌入式系统大都有成本、功耗的要求

嵌入式系统得到多种微处理体系的支持

嵌入式系统需要专用的开发工具

3)嵌入式系统 与 单片机系统的区别

嵌入式系统通常指基于32位微处理器设计的系统(往往带操作系统);单片机系统指基于4位、8位与16位微处理器设计(不使用操作系统)的系统。

嵌入式系统设计的核心是软件设计,约占70%左右的工作量,硬件只占30%;单片机系统软硬件设计工作所占比例基本相同,即约为1:1

嵌入式软件职位与硬件职位的需求比约为7:3,单片机系统约为1:1,甚至软硬件职位不分。

单片机系统可看作是低端嵌入式系统,而以32位微处理器为代表的嵌入式系统则是中、高端嵌入式系统。

嵌入式系统 单片机系统

4)嵌入式系统的特征

嵌入式系统中至少有一片微处理器,是一专用计算机系统;

嵌入式系统软、硬件根据需要进行定制,一般有功耗低、体积小、集成度高、成本低、可靠性高、时时性强等要求。具体要求随应用环境而异。

嵌入式系统采取交叉开发方式进行开发

2. 嵌入式系统的特点

(1)面向具体应用。

(2)是一个技术密集、资金密集、高度分散、不断创新的知识集成系统 。

(3)具有更高的技术要求。

(4)硬件和软件设计要求高效率 。

(5)嵌入式系统一般具有较长的生命周期。

(6)嵌入式系统一般采用具有实时处理能力的嵌入式实时操作系统。

(7)嵌入式系统中的软件一般都采用固化的方式。

(8) 嵌入式系统中软件与系统硬件一体化。

(9)嵌入式系统本身不具备自主开发能力,必须有一套专门的开发环境才能对其进行开发,一般采用交叉开发方式。

3. 嵌入式系统

硬件层

嵌入式系统中的所有硬件设备,是嵌入式系统的物质基础,一般由嵌入式微处理器、存储系统、通信模块、人机接口、I/O接口(A/D、D/A、通用I/O等)以及电源等。

中间层

位于硬件层和操作系统之间的一层,是对硬件层的抽象并使嵌入式操作系统与硬件层无关,是实现嵌入式操作系统夸硬件平台运行的一种技术,其具体表现形式是实现硬件层控制和驱动的程序代码。

嵌入式操作系统(Embed Operation System)

嵌入式系统的灵魂,实现了处理器管理、存储器管理、设备管理、文件管理和用户接口等功能。

应用层

应用层由基于EOS开发针对具体应用开发的应用程序。

第1章 嵌入式系统概述

嵌入式系统基本概念

嵌入式系统的组成

嵌入式处理器

嵌入式操作系统

嵌入式应用软件

4. 嵌入式操作系统

运行在嵌入式计算机系统上支持嵌入式应用程序的操作系统,是用于控制和管理嵌入式系统中的硬件和软件资源、提供系统服务的软件集合 。内核:

任务管理、存储管理、文件系统管理、输入输出设备管理

嵌入式操作系统主要特点:

微型化

代码质量高

专业化

实时性强

可裁减、可配置

第2章 ARM编程模型

2)RISC体系结构

CISC(Complex Instruction Set Computer)复杂指令集计算机,

20世纪70年代在小型计算机上发展起来的一种计算机体系结构

指令复杂,开发成本高,

Intel80386 耗资1.5亿,耗时3年

IBM FS高速机耗资数亿美元未成功

指令长度不等,大量微码

IBM370,208种指令、长度16位~48位,微程序420K

DEC VAX-11/780,303种指令、长度16位~456位、微程序480K

不利于VLSI实现。大量复杂指令,指令长度不等

统计发现,20%的简单指令(取数、运算、转移等)占CPU动态执行时间的80%~90%;80%的复杂指令只占CPU动态执行时间的20%。花那么大的代价设计和实现的复杂指令很少用到,使用复杂指令值得吗?

RISC( Reduced Instruction Set Computer )精简指令集计算机

1980年,Patterson,Ditzel的论文《精简指令集计算机》提出了RISC的设计思想:精简指令集的复杂度,简化指令实现的硬件设计,硬件只执行使用频度最高的那部分简单指令,大部分复杂的操作则由简单指令的组合完成。

伯克利分校很快据此设计出了RISC原型机RISCI与RISCII

ARM是第一个采用RISC结构的商用微处理器

RISC与CISC比较

RISC指令格式和长度固定,类型少,功能简单、寻址简单方式少;CISC指令长度不等、类型多、功能复杂。

RISC使用硬连线指令译码逻辑,易于流水线实现;CISC采用微码ROM译码。

RISC大多数指令单周期完成;CISC指令多为多周期完成。

RISC除Load/Store指令外,所有指令只对寄存器操作;大多数CISC指令皆可对主存及寄存器器操作。

RICS的不足

RISC代码密度没有CISC高,CISC中的一条指令在RISC中有时要用一段子程序来实现。

RISC不能执行x86代码

RISC给优化编译程序带来了困难

2)ARM体系结构版本的变种

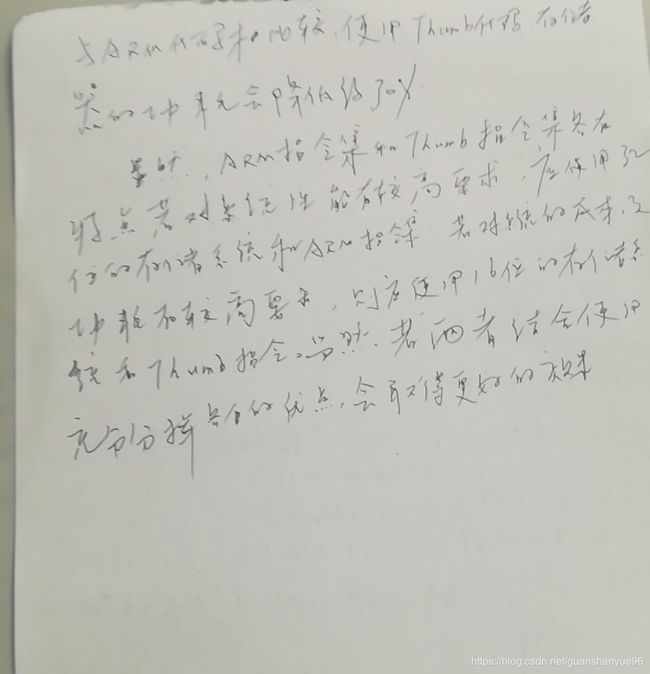

T变量(Thumb指令集)

Thumb指令集是把32位的ARM指令集的一个子集重新编码后形成的具有更高密度的16位指令集。

V4后始有T变种,即V4T, V5T

Thumb技术产生的背景

V4前,基于CISC的8位、16位处理器不能满足移动电话、磁盘驱动器、调制解调器等不断出现的新需求。基于CISC的32核太复杂,在体积、功耗及成本等方面不能满足要求;

RISC32位核处理能力虽能满足要求,但代码密度低,需较大存储空间。

因需要一种处理性能强、代码密度高的处理器,于是产生了Thumb.

Thumb技术的特点

Thumb指令是ARM指令的一个子集,它从标准32位ARM指令集中抽出36条指令格式,重新编成16位的操作码(便于存储);运行时,16位的Thumb指令又由处理器解压成32位的ARM指令,在ARM环境下执行。因此,Thumb技术具有:

比16位处理器更高的处理性能(运行在ARM环境:地址空间、寄存器、移位器、算术逻辑单元、存储器接口宽度等都是32位)

Thumb技术的特点(续)

比32位处理器更高的代码密度 ,同样的程序运行在Thumb状态下时其代码尺寸仅为ARM状态下的60%~70%

Thumb技术始于ARM7TDMI(V4T),支持Thumb的核仅仅是ARM体系结构的一种扩展,所以编译器既可以编译Thumb代码,又可以编译ARM代码

Thumb状态与ARM状态之间可方便地进行切换,切换时不需付任何代价(包括时间等)。

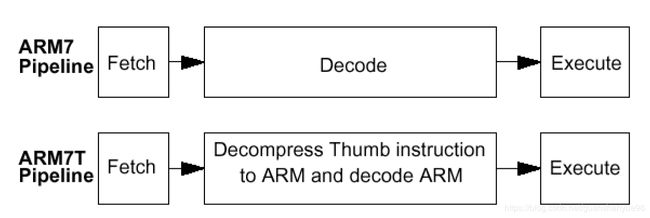

Thumb技术的实现

ARM7T将指令的执行分为3个阶段:取指令、译码和执行,即3级流水线。

利用译码阶段的一个未用的时钟位相,将Thumb指令解压还原为32位的ARM指令

Thumb技术的局限

完成相同的操作,Thumb指令通常需要更多的指令,因此在对系统运行时间要求苛刻的场合ARM指令集更为适合;

Thumb指令集没有包含进行异常处理所需的一些指令,因此在异常中断时需要使用ARM指令,这种限制决定了Thumb指令需要和ARM指令配合使用。

M变量(长乘指令)

长乘指令是一种生成64位相乘结果的乘法指令(此指令为ARM指令),M变种增加了两条长乘指令

32位整数乘32整数产生64位整数

32位整数乘32整数加32位整数产生64位整数

V3始引进M变种,现已为标准部分

E变量(增强型DSP指令)

E变种增加了一些附加指令,用于典型DSP算法的处理,主要包括:

16位数据乘法和乘加操作指令

实现饱和有符号数加减法操作指令

Cache预取指令PLD

E变种始用于V5T,V5前及非M、非T版本中E无效

J变量( Java指令、Jazelle技术)

ARM的Jazelle技术提供的Java加速器运行Java代码比JavaVM快8倍,功耗降80%

Jazelle技术可在单处理器上同时运行ARM和Java指令,取代原需要双处理器或协助处理器的场合。

SIMD变量(ARM媒体功能扩展)

SIMD指令针对音视频处理设计,为下一代的Internet应用产品、移动电话和PDA等需要流式媒体处理的终端设备提供解决方案。

使处理器的音视频性能提高2~4倍

可同时进行2个16位操作数或者4个8位操作数的运算

用户可自定义饱和运算的模式

可进行2个16位操作数的乘加/乘减运算及32位乘以32位的小数运算

ARM体系结构版本变种汇总

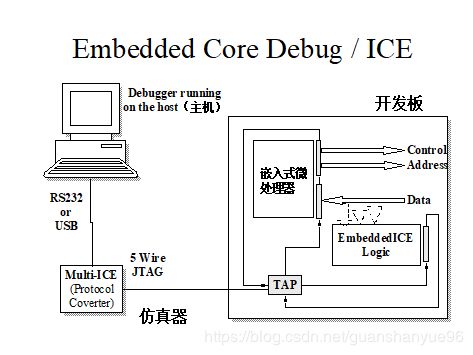

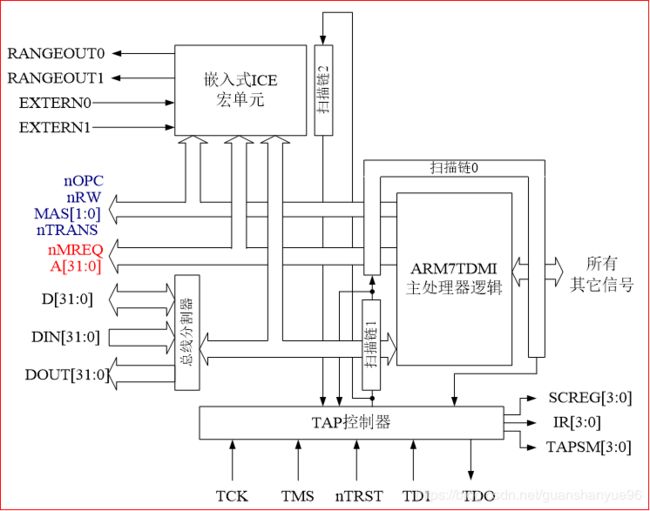

二、ARM内核结构

T功能模块(16 Thumb ): 可以在兼顾性能的同时减少代码尺寸。

M功能模块: (增强型乘法器)可生成全64位的结果。

D功能模块(Debug ):该内核中放置了用于调试的结构。

I功能模块(EmbeddedICE Logic):用于实现断点观测及变量观测的逻辑电路部分

3 ARM核概述

目前在用的ARM处理器系列主要有6个

ARM7(ARM7TDMI)

ARM9

ARM10E

ARM11

SecurCore

Cortex

ARM核命名规则

命名规则的字符串表达式如下:

ARM{x}{y}{z}{T}{D}{M}{I}{E}{J}{F}{-S}

其中花括号的内容表示可有可无。前三个参数含义在下面说明:

{x}表示系列号,例如:ARM7,ARM9,ARM10

{y}表示内部存储管理和保护单元,例如:ARM72,ARM92

{z}表示含有高速缓存(Cache),例如:ARM720,ARM940

其余体系结构版本变量已经在前面幻灯片给出。

ARM核命名规则(续)

说明:

①在ARM7TDMI之后出产的所有ARM内核名称,即使“ARM”字串后面没有包含“TDMI”字符串,也都默认包含了该字串。

②对于2005年以后ARM公司投入市场的ARMv7体系结构的处理器核,使用字符串“ARM Cortex”打头,随后附加一个字母后缀“-A”,“-R”或者“-M”,表示该处理器核适合应用的领域;

其中:后缀A表示应用(Application)、 R表示实时控制(Real time)、M表示微控制器(Micro Controller)。

ARM内核采用了RISC型处理器结构,具有低功耗、成本低、功能强等突出优势,在嵌入式系统及应用领域具有重要的影响,其主要特点包括:

采用了RISC型处理器结构;

低功耗、成本低、功能强;

采用ARM/Thumb(32位/16位)双指令集;

具有多处理器状态模式;

具有在线仿真调试功能;

具有协处理器接口;

具有优化设计的片上总线AMBA(AHB/ASB/APB);

具有灵活方便的接口。

4. ARM工作状态

具有T变种(V4T、V5T)的ARM处理器核可以工作在以下2种状态:

ARM状态

ARM状态下指令长度为32位,ARM指令,字对准

Thumb状态

Thumb状态下长度为16位, Thumb指令,半字对准。

ARM处理器可以在ARM和Thumb两种状态之间进行切换 ,状态的切换不影响处理器的模式或寄存器的内容

ARM处理器如何在两种工作状态之间进行切换?

进入Thumb状态

执行BX Rm指令进入Thumb状态。当操作数寄存器Rm的bit[0]为1时,执行该指令进入Thumb状态。

异常处理返回时,自动切换到Thumb状态(若在Thumb状态进入异常)

进入ARM状态

执行BX Rm指令进入ARM状态。当操作数寄存器Rm的bit[0]为0时,执行该指令进入ARM状态。

进行异常处理时进入ARM状态。处理器进行异常处理时,把PC放入异常模式链接寄存器LR中,将异常向量地址装入PC,进入ARM状态进行异常处理。

ARM处理器启动时处于什么状态?

ARM处理器启动时,只能处于ARM状态

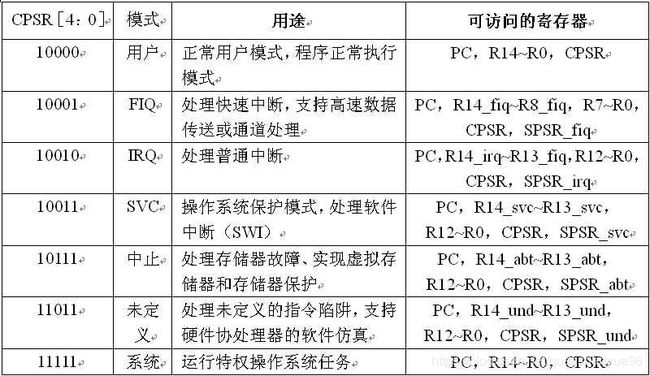

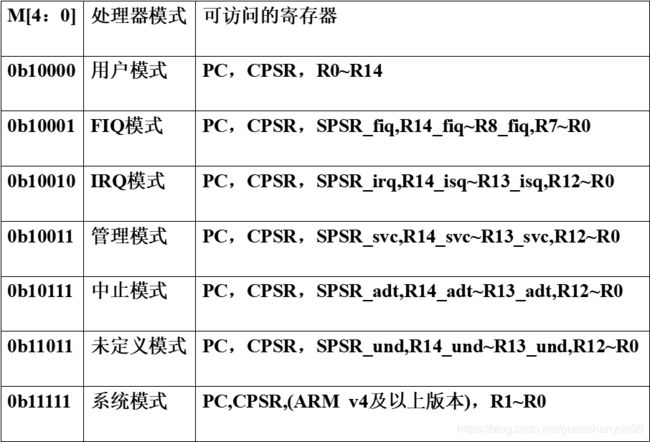

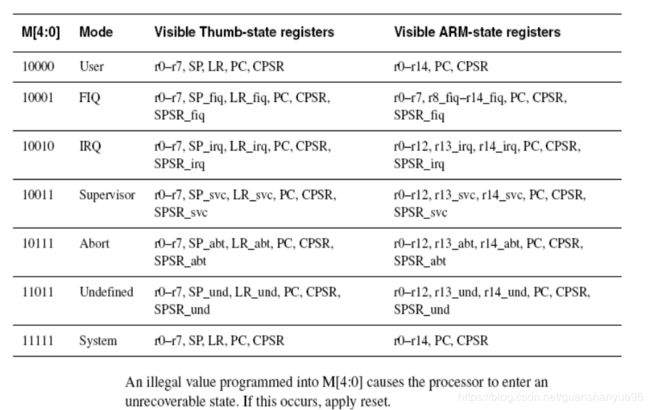

5. ARM工作模式

ARM支持7种工作模式,由CPSR的低5位决定。

用户模式是最基本的工作模式,大多数用户程序运行在用户模式下,在此模式下应用程序不能访问一些受操作系统保护的资源,也不能进行模式切换。在用户模式下运行的程序处于用户等级。

用户模式外的其它6种模式(FIQ、IRQ、SVC、中止、未定义与系统)则能访问受操作系统保护的资源,也能进行模式切换,比用户模式有更高的权。在此6种模式下运行的程序处于特权等级。

如何变换模式?

在特权等级下可通过修改CPSR的模式位进入相应的模式;发生异常中断时处理器会自行修改模式位进入相应的异常中断模式

在任一时刻处理器只能在一种模式下工作,如上电启动与发生复位中断时,处理器自动切换到SVC模式下运行;发生软中断时,处理器也将自动切换到SVC模式下运行;响应IRQ中断时,处理器自动切换到IRQ模式下运行。

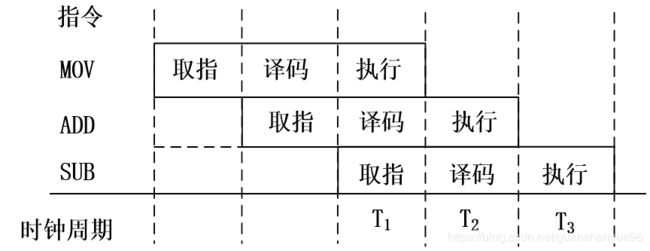

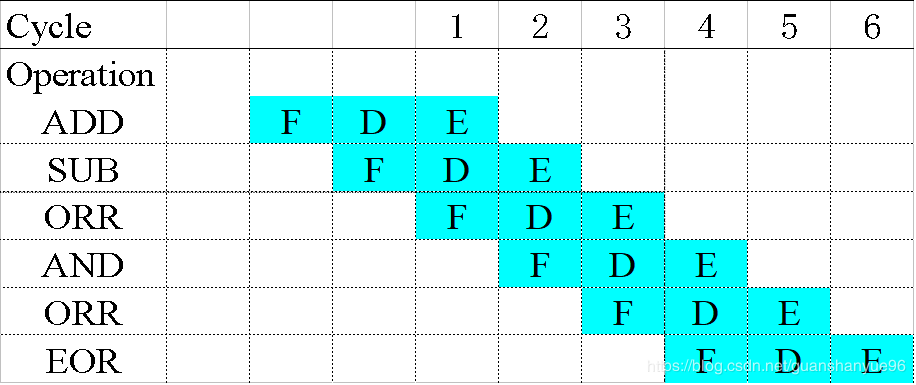

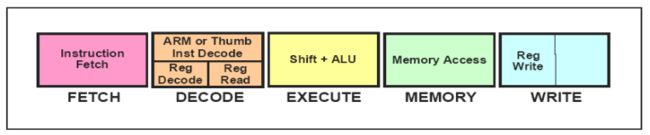

三级指令流水线是ARM7TDMI的主要特征之一,三级指令流水线指令的执行分为取指、译码和执行三个阶段,各阶段所完成的操作详细分解表如下:

![]()

ARM7TDMI单周期指令最佳流水线

MOV、ADD、SUB指令为单周期指令。从T1开始,用3个时钟周期执行了3条指令,指令平均周期数等于1个时钟周期。

4. ARM启动方式

ARM内核真正支持的启动方式只有一个:通过操作CP15来实现对reset vector的重定向

memory remap:这一机制并非ARM内核本身所支持的,而是在SoC的时候人为修改memory的访问逻辑而实现的

5.ARM处理器运行模式

ARM微处理器运行模式要注意的问题

1、ARM微处理器的运行模式可以通过软件改变,也可以通过外部中断或异常处理改变。

2、大多数的应用程序运行在用户模式下,当处理器运行在用户模式下时,某些被保护的系统资源是不能被访问的。

3、除用户模式以外,其余的所有6种模式称为非用户模式或特权模式(Privileged Modes);

4、其中除去用户模式和系统模式以外的5种又称为异常模式(Exception Modes),常用于处理中断或异常,以及需要访问受保护的系统资源等情况。

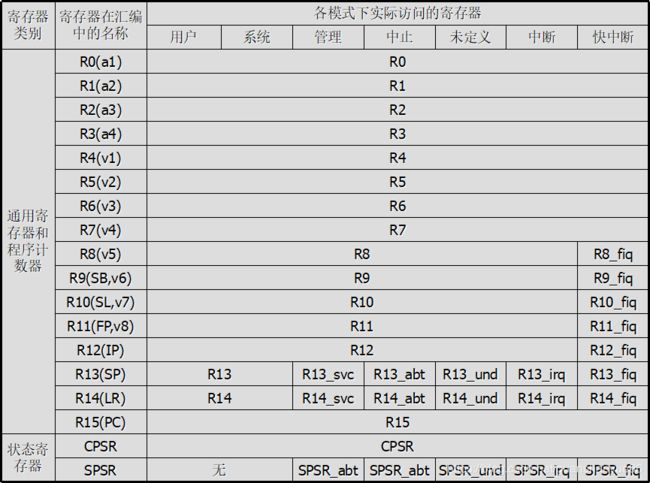

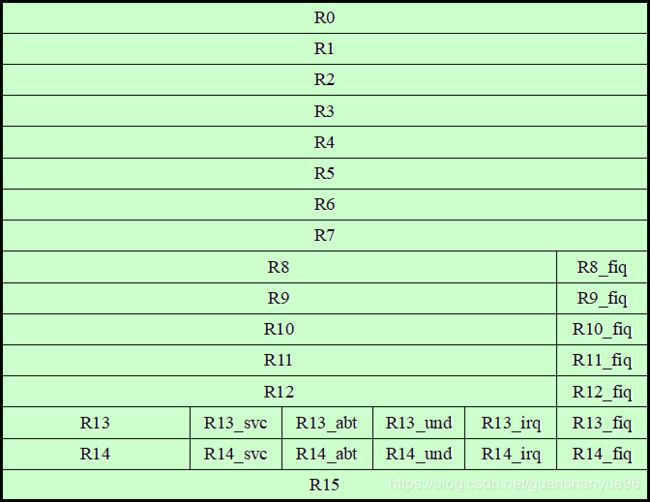

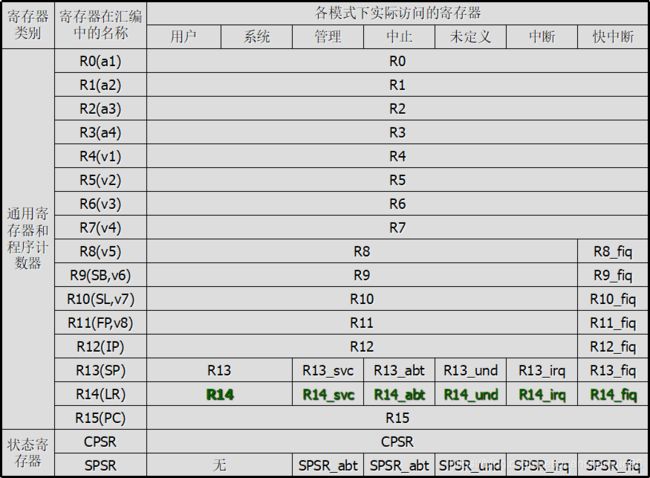

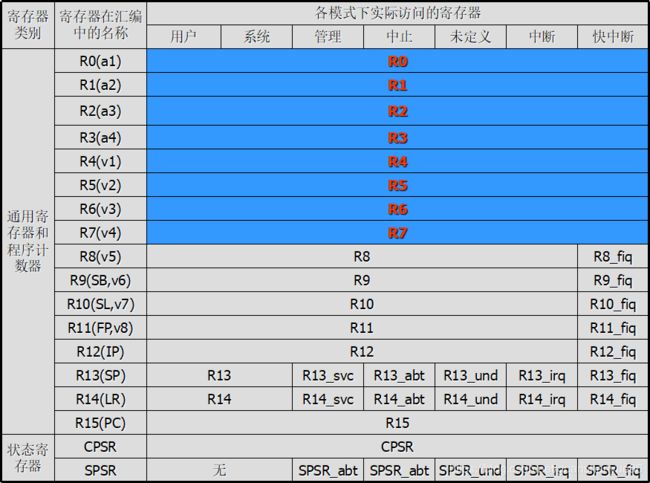

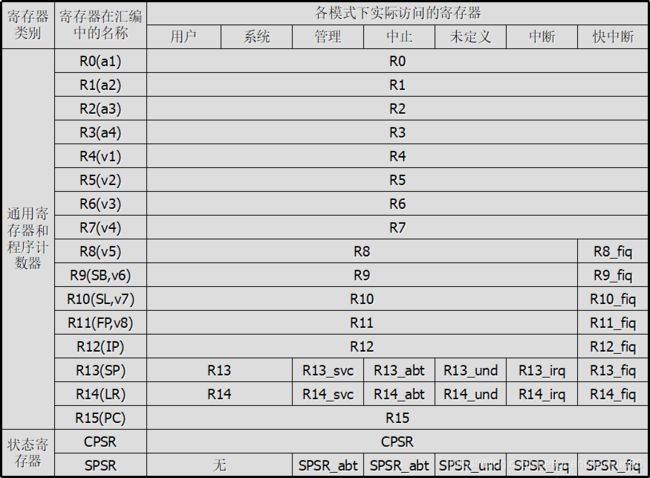

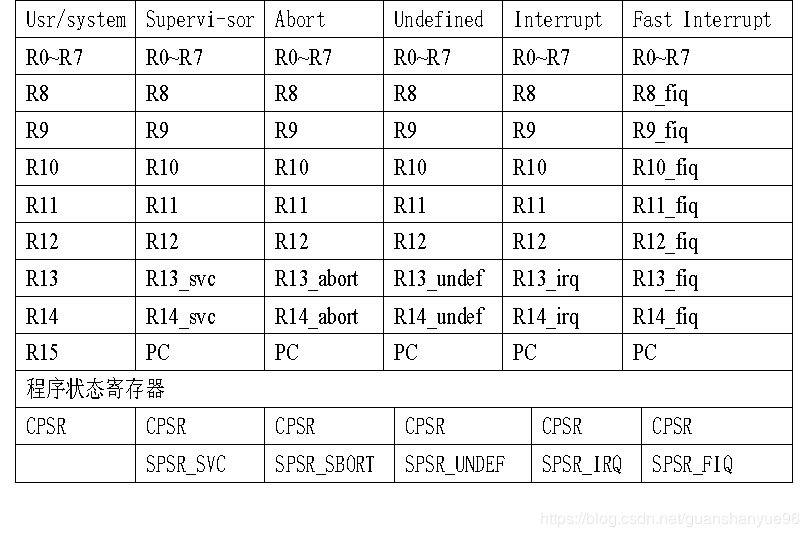

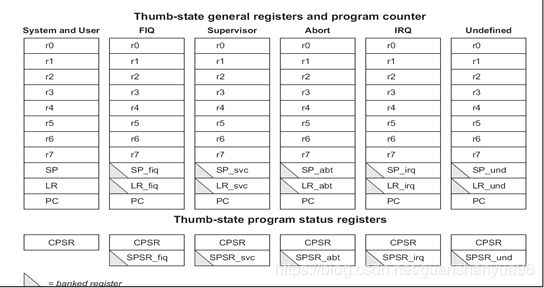

ARM状态下总共有37个寄存器,可分为两类:

通用寄存器 (31个)

R0~R15;

R13_svc、R14_svc;

R13_abt、R14_abt;

R13_und、R14_und;

R13_irq、R14_irq;

R8_frq~R14_frq。

状态寄存器(6个)

CPSR、SPSR_svc、SPSR_abt、SPSR_und、SPSR_irq和SPSR_fiq

这37个寄存器不能被同时看到,在特定工作模式下能使用的寄存器没这么多!

1) ARM状态下的寄存器

通用寄存器

不分组寄存器(The unbanked registers):R0~R7 。

分组寄存器(The banked registers):R8~R12 。

分组寄存器(The banked registers;

R13~R14.

程序计数器:R15(PC)

不分组寄存器R0~R7

R0~R7不分组寄存器用于保存地址或数据。是所有处理器模式下共用的寄存器,在模式切换时必须进行保护,进堆。

分组寄存器R8-R12

FIQ模式有单独的分组寄存器R8_fiq~R12_fiq,FIQ(快速中断)处理程序不用保存和恢复中断现场,中断处理更加快速。

FIQ以外的分组寄存器R8~R12为四种异常模式(Svc,Abort,Undef,IRQ)共用,模式切换时需保护。

所有的37个寄存器,分成两大类:

31个通用32位寄存器;

6个状态寄存器。

在汇编语言中寄存器R0~R13为保存数据或地址值的通用寄存器。它们是完全通用的寄存器,不会被体系结构作为特殊用途,并且可用于任何使用通用寄存器的指令。

其中R0~R7为未分组的寄存器,也就是说对于任何处理器模式,这些寄存器都对应于相同的32位物理寄存器。

在汇编语言中寄存器R0~R13为保存数据或地址值的通用寄存器。它们是完全通用的寄存器,不会被体系结构作为特殊用途,并且可用于任何使用通用寄存器的指令。

其中R0~R7为未分组的寄存器,也就是说对于任何处理器模式,这些寄存器都对应于相同的32位物理寄存器。

寄存器R8~R14为分组寄存器。它们所对应的物理寄存器取决于当前的处理器模式,几乎所有允许使用通用寄存器的指令都允许使用分组寄存器

寄存器R8~R12有两个分组的物理寄存器。一个用于除FIQ模式之外的所有寄存器模式,另一个用于FIQ模式。这样在发生FIQ中断后,可以加速FIQ的处理速度。

寄存器R13、R14分别有6个分组的物理寄存器。一个用于用户和系统模式,其余5个分别用于5种异常模式。

寄存器R13常作为堆栈指针(SP)。在ARM指令集当中,没有以特殊方式使用R13的指令或其它功能,只是习惯上都这样使用。但是在Thumb指令集中存在使用R13的指令。

R14为链接寄存器(LR),在结构上有两个特殊功能:

在每种模式下,模式自身的R14版本用于保存子程序返回地址;

当发生异常时,将R14对应的异常模式版本设置为异常返回地址(有些异常有一个小的固定偏移量)。

1) ARM状态下的寄存器

分组寄存器R13

R13通常用做堆栈指针SP ,习惯用法,非强制

每一种异常模式都有自已的物理R13

分组寄存器R14

R14称作子程序链接寄存器(Link Register-LR),简称LR,用于存放当前子程序的返回地址。当程序执行子程序调用指令BL,BLX时,当前的PC将保存在R14中。执行完子程序后,只要将R14复制到PC,子程序即可返回。

每一种异常模式都有自已的物理R14

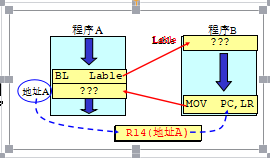

R14(LR)寄存器与子程序调用

调用流程

1.程序A执行过程中调用程序B;

2.程序跳转至标号Lable,执行程序B。同时硬件将“BL Lable”指令的下一条指令所在地址存入R14(LR);

3.程序B执行最后,将R14寄存器的内容放入PC,返回程序A;

R14寄存器注意要点

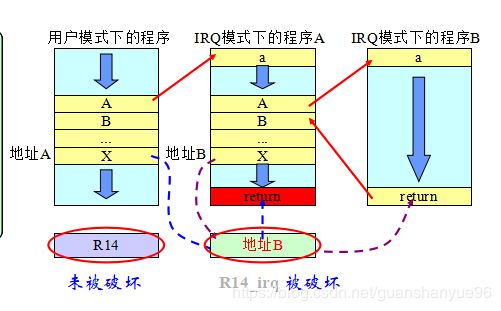

6. 在程序B返回到程序A,然后在返回到用户模式下被中断的程序时,发生错误,将不能正确返回;

1) ARM状态下的寄存器

程序计数器R15

寄存器R15被用作程序计数器,也称为PC

R15值的改变将引起程序执行顺序的变化,这有可能引起程序执行中出现一些不可预料的结果

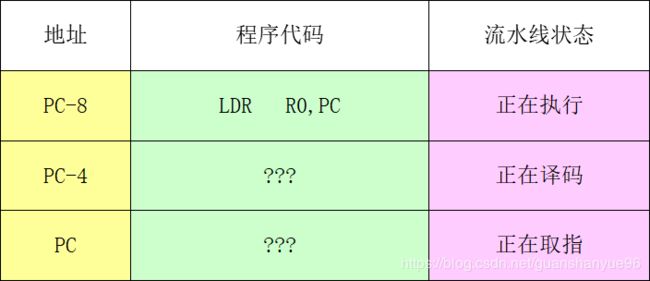

ARM处理器采用多级流水线技术,因此保存在R15的程序地址并不是当前正在被执行的指令的地址,而是当前正被取的指令的地址

一些指令对于R15的用法有一些特殊

寄存器R15为程序计数器(PC),它指向正在取指的地址。可以认为它是一个通用寄存器,但是对于它的使用有许多与指令相关的限制或特殊情况。如果R15使用的方式超出了这些限制,那么结果将是不可预测的。

正常操作时,从R15读取的值是处理器正在取指的地址,即当前正在执行指令的地址加上8个字节(两条ARM指令的长度)。由于ARM指令总是以字为单位,所以R15寄存器的最低两位总是为0。

1) ARM状态下的寄存器

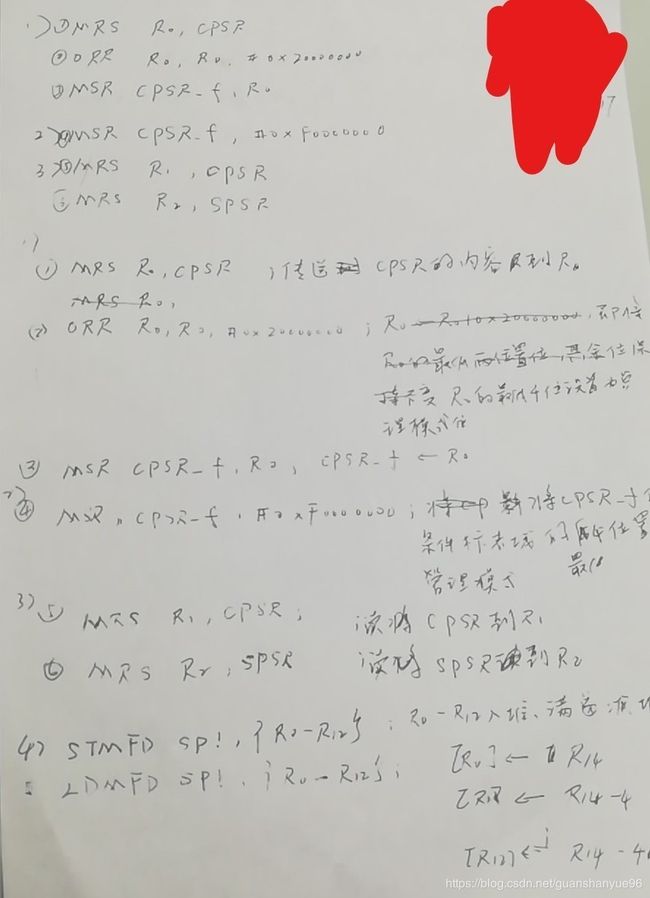

状态寄存器

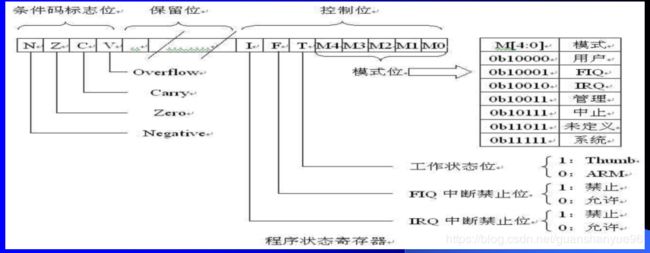

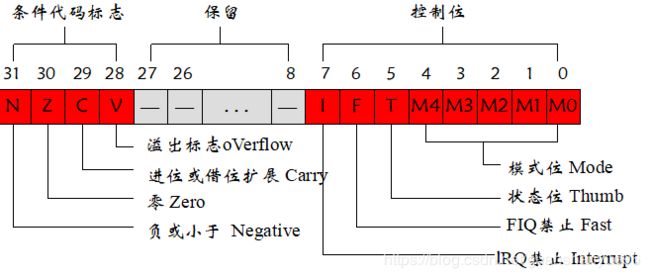

CPSR(Current Program Status Register):当前程序状态寄存器,指示当前程序的状态信息,包括条件码标志、中断禁止位、当前处理器模式以及其它状态和控制信息。

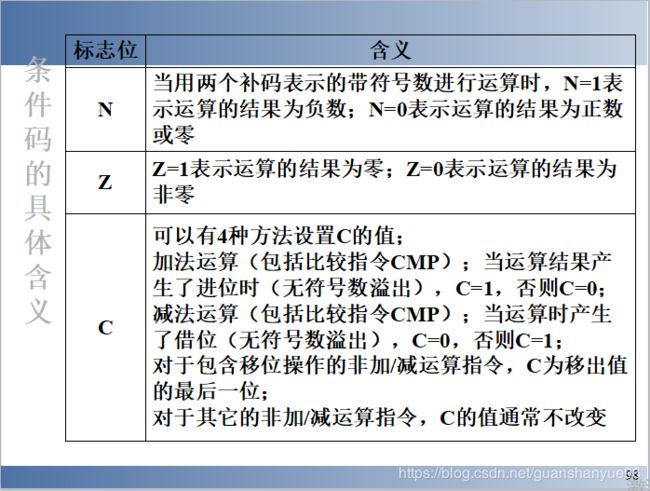

2 .程序状态寄存器

① 条件码标志(Condition Code Flags)

N、Z、C、V均为条件码标志位。它们的内容可被算术或逻辑运算的结果所改变,并且可以决定某条指令是否被执行。

② 控制位

PSR的低8位(包括I、F、T和M[4:0])称为控制位,当发生异常时这些位可以被改变。如果处理器运行特权模式,这些位也可以由程序修改。

中断禁止位I、F

I=1 禁止IRQ中断

F=1 禁止FIQ中断

T标志位:该位反映处理器的运行状态。

对于ARM体系结构v5及以上版本的T系列处理器,当该位为1时,程序运行于Thumb状态,否则运行于ARM状态。非T系列处理器,当该位为1时,执行下一条指令以引起未定义的指令异常;当该位为0时,表示运行于ARM状态。

运行模式位M[4:0]:M0、M1 、 M2、M3、M4是模式位。这些位决定了处理器的运行模式。具体含义如下表:

注意:并不是所有的运行模式位的组合都是有效的,其他的组合结果会导致处理器进入一个不可恢复的状态!

③ 保留位

PSR中的其余位为保留位,当改变PSR中的条件码标志位或者控制位时,保留位不要改变,在程序中也不要使用保留位来存储数据。保留位将用于ARM版本的扩展。

1) ARM状态下的寄存器

CPSR为所有模式共用,因此模式切换时需要保护。如何保护?

SPSR(Saved Program Status Register)

程序状态保存寄存器。每种异常模式都有一个对应的SPSR物理寄存器( SPSR_svc、SPSR_abt、SPSR_und、SPSR_irq、SPSR_fiq ),当异常出现时,用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。 SPSR的格式与CPSR相同。

3 .ARM状态下的寄存器

表为ARM状态下的寄存器组织

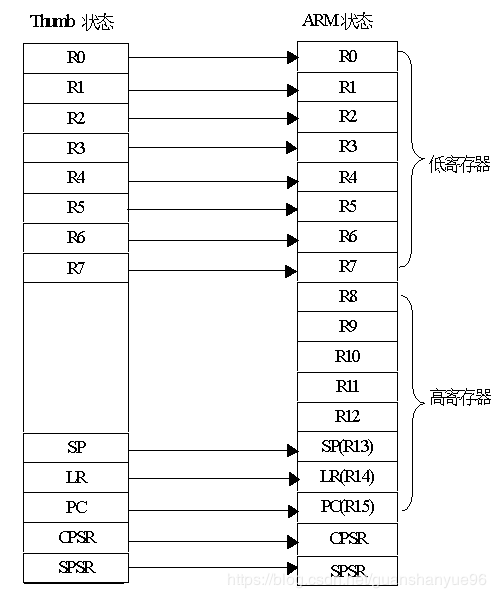

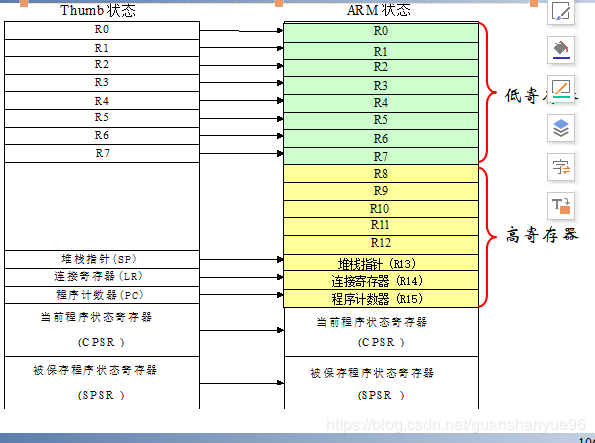

2)Thumb状态下的寄存器

Thumb状态下的寄存器集是ARM状态下寄存器集的子集。程序员可以直接访问8个通用的寄存器(R0~R7),程序计数器PC、堆栈指针SP、连接寄存器LR和当前状态寄存器CPSP。每一种特权模式都各有一组SP,LR和SPSR。

2)Thumb状态下的寄存器

Thumb状态寄存器与ARM状态寄存器关系:

Thumb r0–r7 与 ARM r0–r7 相同

Thumb CPSR / SPSRs 与 ARM CPSR / SPSRs相同

Thumb SP 映射到 ARM r13

Thumb LR映射到 ARM r14

Thumb pc映射到 ARM pc (r15).

Thumb状态寄存器在Arm状态寄存器上的映射

ARM态与Thumb态寄存器总结

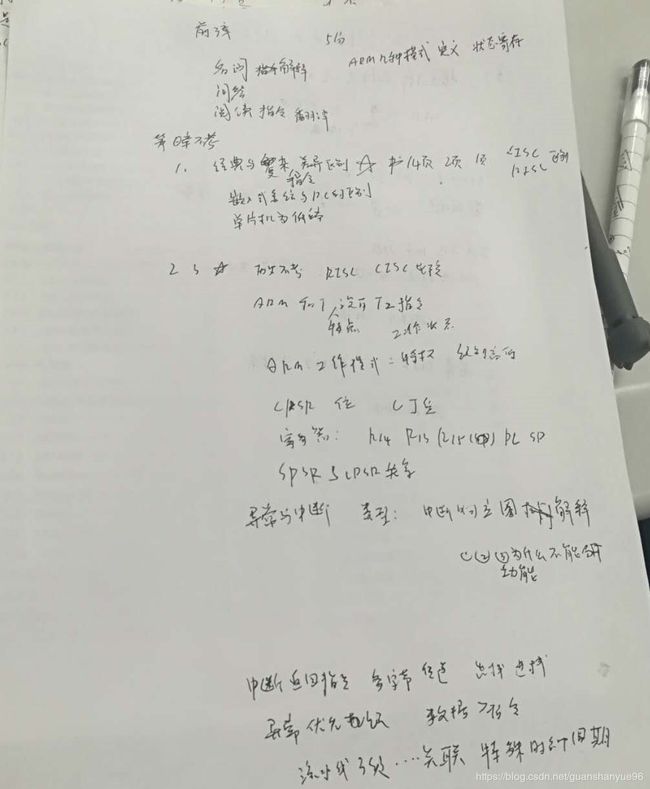

复习

ARM工作状态?

ARM

Thumb

ARM工作模式?

![]()

ARM状态下的寄存器?

Thumb状态下的寄存器?

第2章 ARM编程模型

三、ARM中断与异常

1.顺序执行:每执行一条ARM指令,程序计数器寄存器的值加4个字节;每执行一条Thumb指令,程序计数器寄存器的值加两个字节。

2.跳转:通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。

3.异常:当异常或中断发生时,系统执行完当前指令后,将跳转到相应的异常处理程序处执行。异常是指处理器正常的程序执行流程发生暂时的停止。

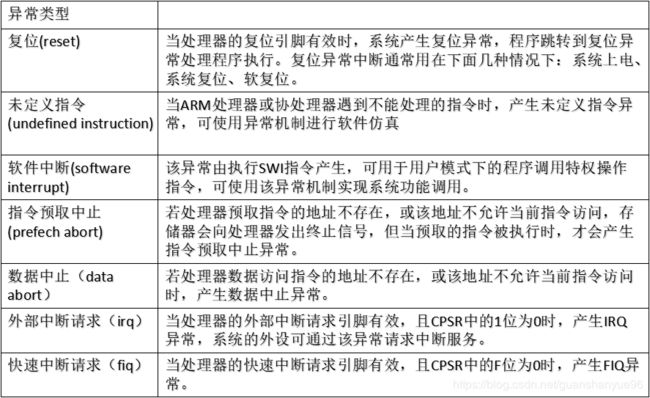

1 .ARM中断与异常类型

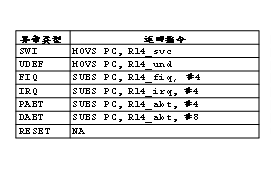

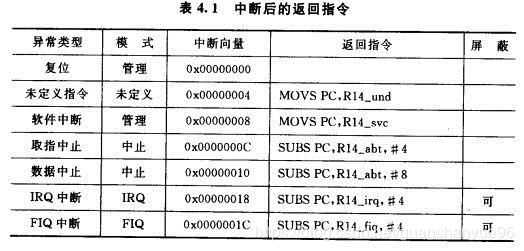

2.异常的响应及返回类型

当一个异常出现以后,ARM微处理器会执行以下几步操作:

(1)保存处理器当前状态、中断屏蔽位以及各条件标志位。将下一条指令的地址存入相应连接寄存器,以便程序在处理异常返回时能从正确的位置重新开始执行。

(2)根据异常类型,设置CPSR中相应的位 包括设置CPSR中的位,使处理器进入相应的执行模式;设置CPSR中的位,禁止IRQ中断,当进入FIQ模式时,禁止FIQ中断。

(3)将程序计数器设置为该异常中断的中断向量地址,之后跳转到相应的异常中断处理程序处执行。

(4)还可以设置中断禁止位,以禁止中断发生。如果异常发生时,处理器处于Thumb状态,则当异常向量地址加载PC时,处理器自动切换到ARM状态。

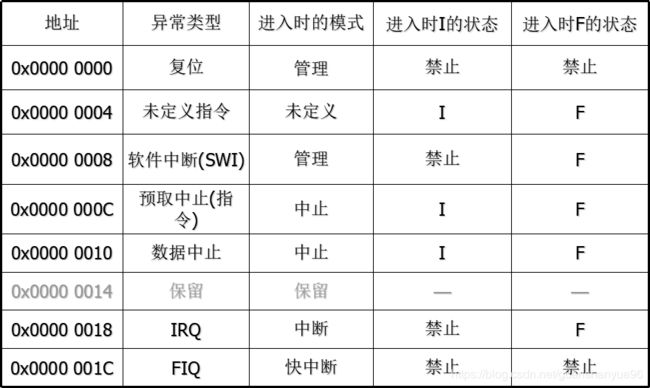

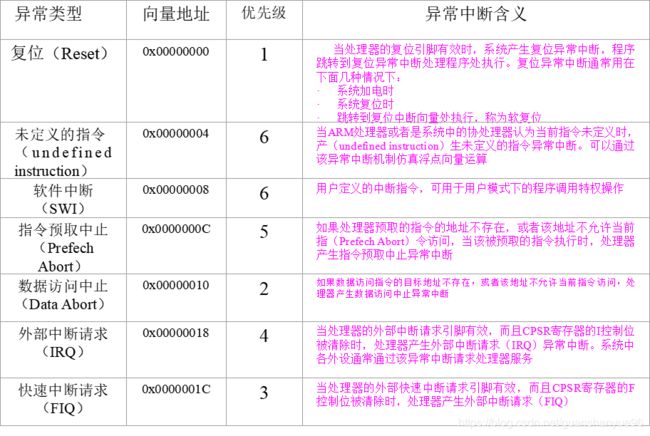

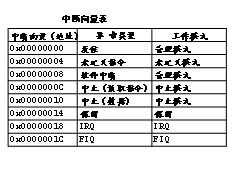

3. 中断与异常入口向量

7. ARM的异常中断

ARM用3种方式执行程序流程:

正常执行。ARM状态,PC+4;Thumb状态,PC+2

指令跳转。B(跳转到标号执行),BL(跳、返回地址保存),BX(跳、状态切换),BXL(跳、切、存)

异常中断。异常中断发生时,系统将跳转到预先设定的异常中断向量处执行,待异常中断处理完成后再返回到被中断处继续执行

ARM中的异常中断类型

异常中断响应

异常中断返回

异常中断服务程序结构

异常中断向量表

异常中断的优先级

异常中断类型

复位中断(Reset)

未定义指令异常(Undefined Instruction)

软件中断(Software interrupt)

预取指令中止异常(Prefetch Abort)

取数据中止异常(Data Abort)

普通中断 (Interrupt ReQuest-IRQ)

快速中断FIQ

复位中断(Reset)

当处理器的复位引脚有效时(nRESET signal goes LOW) ,系统产生复位中断,程序跳转到复位中断处理程序处(地址0x00000000)执行。复位中断通常用发生在下面3种情况下:

系统加电时

系统复位时

跳转到复位中断向量处执行,称为软复位

未定义指令异常(undefined instruction) 当处理器/协处理器认为当前指令未定义时,产生未定义指令异常。可以通过该异常机制仿真浮点向量运算

软件中断(Software Interrupt-SWI)

一个由用户定义的中断指令,可用于用户模式下的程序调用特权操作。

指令预取指中止异常(Prefetch Abort)

如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,处理器产生指令预取中止异常

数据访问中止异常(Data Abort)

如果数据访问指令的目标地址不存在,或者该地址不允许当前指令访问,处理器产生数据访问中止异常

普通中断(Interrupt Request-IRQ)中断

当处理器的外部中断请求引脚有效(nIRQ input LOW ),且CPSR寄存器的I控制位被清除时产生普通中断(IRQ)。系统中各外设通常通过该中断请求处理器服务.

快速中断(Fast Interrupt Request-FIQ)

当处理器的外部快速中断请求引脚有效(nFIQ input LOW),且CPSR寄存器的F控制位被清除时产生外部快速中断请求(FIQ)。FIQ用于数据传送和通道处理,有足够的私有寄存器,产生异常时不须对寄存器进行保护,故其是所有异常处理中最快的。

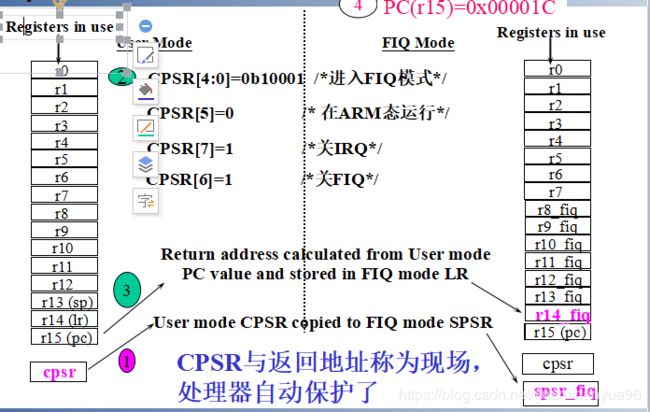

ARM对异常中断的响应过程如下:

将CPSR的内容保存到相应的异常模式的SPSR_

设置当前状态寄存器CPSR中的相应位

设置模式控制位CPSR[4:0]

切换到ARM状态

设置中断标志位CPSR[7],禁止IRQ

若是进入Reset 或FIQ,还需设置中断标志位CPSR[6],禁止FIQ

将产生异常中断指令的下一条指令的地址保存到相应的连接寄存器R14_

给程序计数器(PC)强制赋值(即装入相应的异常中断向量地址)

2) ARM异常中断响应(伪代码)

SPSR_

CPSR[4:0]=Exception Mode Number

CPSR[5]=0 ; 运行于ARM状态

CPSR[7]=1 ;禁止IRQ中断

IF

CPSR[6]=1 ; 禁止新的FIQ异常

R14_

PC=Exception Vector Address

2) ARM异常中断响应

2) ARM异常中断响应

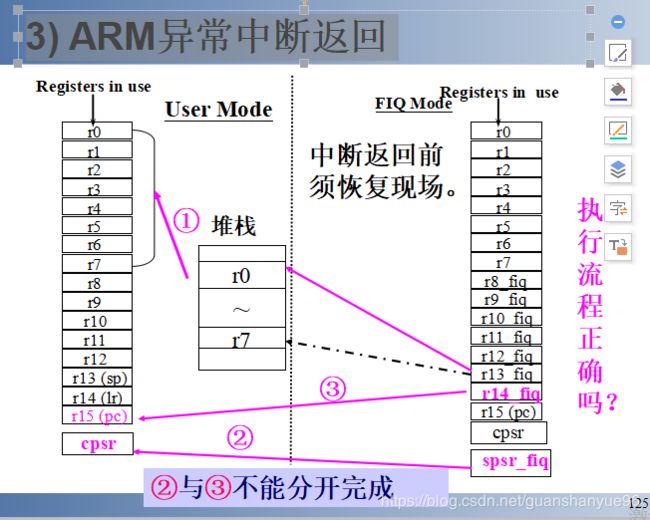

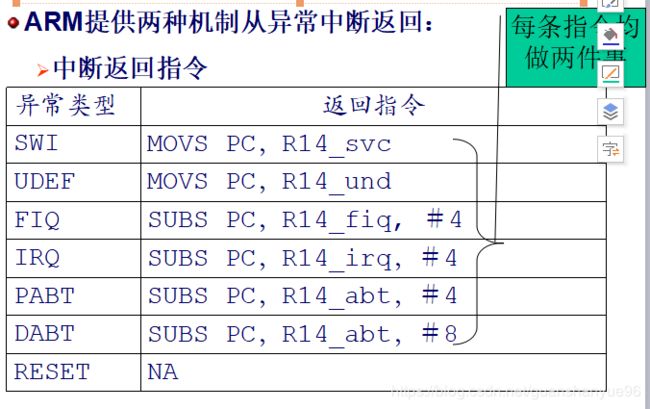

3) ARM异常中断返回

3) ARM异常中断返回

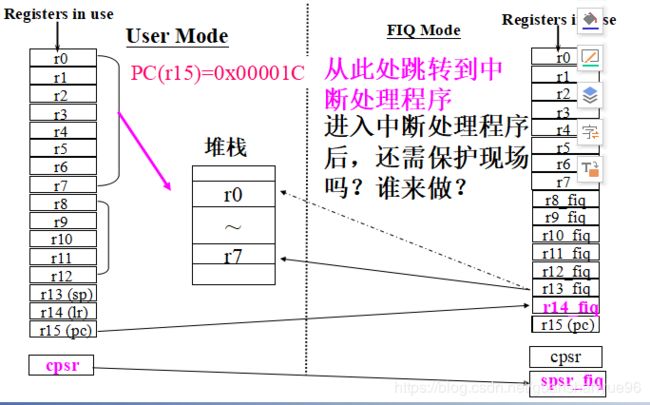

4)ARM异常中断服务程序结构

中断服务(处理)程序是处理中断事务的程序。中断事务不同,其处理程序亦不同,但中断处理程序的结构是相同的,在程序的开始处保护现场,在程序的结束处恢复现场并进行中断返回。

下面分别给出用中断返回指令与多字节传送指令实现的FIQ中断处理程序的结构。

(1)用中断返回指令实现的FIQ中断处理程序FIQ_ISR:

stmfd sp!, {r0-r7 }; r0-r7进栈,保护现场

………..

ldmfd sp!, {r0-r7 };r0-r7出栈,恢复现场

subs pc, r14, #4 ;中断返回

中断服务(处理)程序是处理中断事务的程序。中断事务不同,其处理程序亦不同,但中断处理程序的结构是相同的,在程序的开始处保护现场,在程序的结束处恢复现场并进行中断返回。

下面分别给出用中断返回指令与多字节传送指令实现的FIQ中断处理程序的结构。

(1)用中断返回指令实现的FIQ中断处理程序FIQ_ISR:

stmfd sp!, {r0-r7 }; r0-r7进栈,保护现场

………..

ldmfd sp!, {r0-r7 };r0-r7出栈,恢复现场

subs pc, r14, #4 ;中断返回

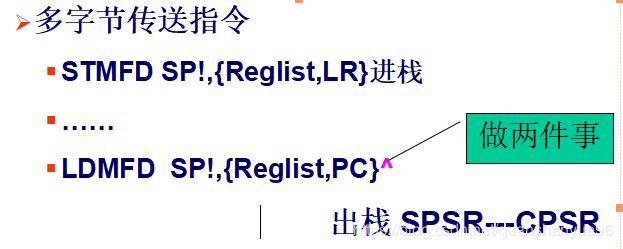

(2)用多字节传送指令实现的FIQ中断处理程序

FIQ_ISR:

stmfd sp!,{r0-r7,lr} ; r0-r7及lr进栈,保护现场

……

ldmfd sp!,{r0-r7,pc}^ ; r0-r7及pc出栈,恢复现场,中断返回

5) ARM异常中断向量表

中断向量?

中断向量是一个地址,每个异常中断均对应一个地址,当异常中断发生时,与其对应的地址会被强制赋给PC ,ARM的中断向量占4字节。

中断向量表?

中断向量按序排列(List)得到的表。

![]()

6) ARM异常中断的优先级

当几个异常中断同时发生时,在ARM中通过给各异常中断赋予一定的优先级来决定中断的处理顺序 :

复位(最高优先级);

取数据中止异常;

FIQ;

IRQ;

预取指中止异常;

SWI、,未定义指令(包括缺协处理器)。

ARM异常中断类型、矢量地址与优先级总结

ARM的异常中断复习

ARM中的异常中断有几种类型?

异常中断与处理器工作模式的关系

如何响应异常中断?

如何从异常中断返回?

异常中断处理程序结构什么样?

何为异常中断向量表?

哪种异常中断的优先级最高?

ARM中有5种异常模式,有7种中断源。这7种中断源中有些中断是我们希望发生的,但有些中断是我们不希望发生的。

我们希望发生的中断:

软中断:属于svc模式,通过SWI指令便可以产生软中断,进入到svc模式。

irq中断:属于irq模式,当产生普通的外部中断时,处理器便进入到IRQ模式。

fiq中断:属于fiq模式,当产生高优先级外部中断时,处理器便进入到FIQ模式。

我们不希望发生的中断:

复位:属于svc模式,当系统上电时便会产生复位中断,系统进入到svc模式。复位中断不需要中断返回。

取指中止中断:属于abt模式,当预取指发生错误时,便产生取指中止中断,进入到abt模式。

数据中止中断:属于abt模式,当访问数据存储器时,便产生数据中止中断,进入到abt模式。

未定义指令中断:属于und模式,当执行到一条未定义指令时,便产生未定义指令中断,系统进入到und模式。

中断的优先级:

ARM中有6个优先级。各个中断的优先级顺序如下:(1 6 6s 5 2 4 3)

复位: 1数据中止中断:2fiq中断:3irq中断:4预取址中止中断:5未定义指令中断和软中断:6

关于各种中断在中断返回时还需要给LR减去一个不同的偏移量的问题我觉得没必要深入研究了,这还要涉及到ARM指令的流水线技术,平时写中断代码都是用C写的,没必要知道这个。用到时再去查表即可。

处理器在进入异常和退出异常时所做的工作:

进入异常时:

1、将要返回处的地址保存在对应异常模式的LR中。(复位不需要保存返回地址)2、将cpsr的内容复制到对应异常模式的spsr中。3、强制修改cpsr的内容,进入到相应异常模式以及根据需要修改某些位。4、强制PC从相应的中断向量地址处进行取址。

注:以上这些步骤都是有cpu自动完成的,也就是当有中断产生时,硬件就会自动完成上述步骤。

退出异常时:

1、将LR中保存的地址赋给PC。2、将spsr的内容恢复给cpsr。3、将irq中断禁止位清零。

注:只需要在异常处理程序中写一句返回指令(如上面的表4.1所示)即可全部实现上述的步骤。

嵌入式中 ARM的几种工作模式 以及异常模式的优先级

一、Arm工作模式:

Arm微处理器支持7种工作模式,分别为:

1. 用户模式(Usr) 用于正常执行程序

2. 快速中断模式(FIQ) 用于高速数据传输

3. 外部中断模式(IRQ) 用于通常的中断处理

4. 管理模式(SVC) 操作系统使用的保护模式(高权限),复位和软件中断进入

5. 数据访问终止模式(abt) 当数据或指令预取终止时进入该模式,可用于虚拟内存及存储保护

6. 系统模式(sys) 运行均有特权的操作系统任务

7. 未定义指令终止模式(und) 用于支持硬件协处理器的软件仿真(浮点、微量运算)

其中除了用户模式以外,其余所有6种模式称之为非用户模式(特权模式,权限比用户模式高),

其中特权模式中除去系统模式外的5种模式称之为异常模式(在用户模式和系统模式看来这些都属于异常),常用于处理中断或异常,以及需要访问受保护的系统资源等情况。

异常模式优先级如下:

1(最高) SVC 复位

2 数据中止

3 FIQ(快速中断请求)

4 IRQ(外部中断请求)

5 abt 预取指令中止

6(最低) und 未定义指令,SWI

从编程的角度看,arm微处理器的工作状态有两种,并可在两种状态之间切换:

(1) arm状态,此时处理器执行32位的字对齐的arm指令

(2) thumb状态,此时处理器执行16位的,半字对齐的thumb指令

(为了兼容老芯片)在程序运行的过程中,可以在两种状态之间进行相应的转换。

处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。

二、存储器格式(字对齐):

Arm体系结构将存储器看做是从零地址开始的字节的线性组合。

从 0~3 字节放置第一个存储的字(32位)数据,

从 4~7 字节放置第二个存储的字数据,一次排列。作为32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。

存储器格式:

Arm体系结构可以用两种方法存储字数据,称之为大端格式和小端格式(如上上章所讲)。

大端格式:字数据的高字节存储在低地址中,而字数据的低地址存放在高地址中。 比较直观

小端格式:与大段格式相反。 易计算机存储

如:int ox12345678

大端:12 34 56 78

小羰:78 56 34 12

三、指令长度:

Arm微处理器的指令长度是32位的,也可以为16位(thumb状态下)。Arm微处理器中支持字节(8位),半字(16位),字(32位)三种数据类型,其中,字需要4字节对齐,半字需要2字节对齐。

注:所谓的指令长度是一条完整的指令的长度,而不是单纯的mov这3个字母长度

四、Arm的工作模式切换

有两种方法:

被动切换:在arm运行的时候产生一些异常或者中断来进行模式切换

主动切换:通过软件改变,即软件设置寄存器来经行arm的模式切换,因为arm的工作模式都是可以通过相应寄存器的赋值来切换的。

注:当处理器运行在用户模式下,某些被保护的系统资源是不能被访问的。

---------------------

原文:https://blog.csdn.net/firefly_2002/article/details/8034078

1)流水线概括

汽车生产流水线…

计算机指令的执行是分阶段进行的,各个阶段相对独立,因此可将CPU内部的指令执行部件(逻辑电路)设计成分级的处理部件,实行流水处理,如汽车的生产。

流水线技术大大加快了处理器的指令执行速度,因此现代CPU设计方案中几乎都采用了流水线技术。

ARM处理器设计也不例外。所有的ARM处理器核都使用了流水线设计。

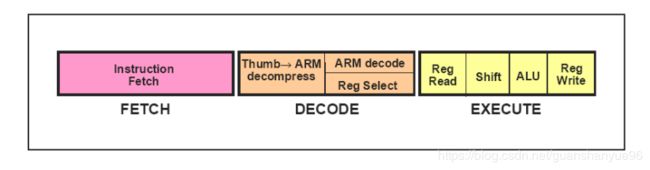

2) ARM7TDMI流水线

ARM7TDMI核3级指令流水线

<1>取指。把指令从内存中取出,放入指令流水线。由取指部件处理。

<2>译码。进行指令译码。在这一级指令占有译码逻辑;

<3>执行。执行流水线中已经被译码的指令。在这一级,指令占有数据通路,移位器,寄存器bank、读数据寄存器,ALU,写数据寄存器。

2) ARM7TDMI流水线例—最佳流水线

F-取指 D-译码 E-执行

该例用6个时钟周期执行了6条指令

所有操作都在寄存器中(单周期执行)

指令周期数(CPI)=1

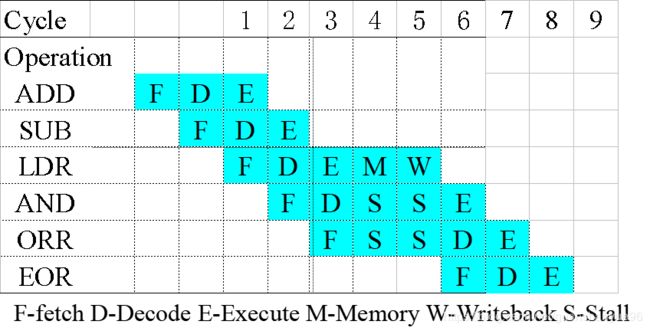

2) ARM7TDMI流水线例—LDR 流水线

F-fetch D-Decode E-Execute M-Memory W-Writeback S-Stall

该例用6个时钟周期执行了4条指令

指令周期数(CPI)=1.5

LDR R0,[R5]

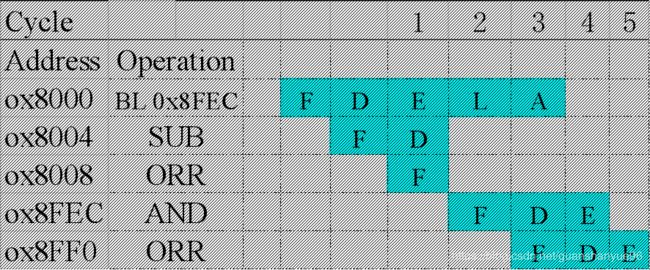

2) ARM7TDMI流水线例—分支流水线

F-fetch D-Decode E-Execute L-Linkret A-Adjust

流水线被阻断

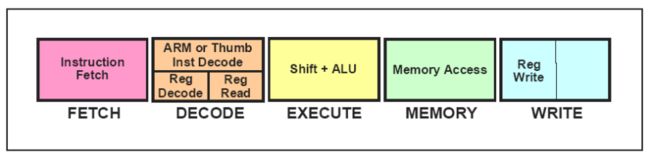

3)ARM9流水线

ARM9TDMI采用了5级流水线。这5个指令执行阶段的功能如下:

<1>取指。从指令存储器中读取指令,放入指令流水线。

<2>译码。对指令进行译码,从通用寄存器组中读取操作数。由于寄存器组有3个读端口,大多数ARM指令能在一个时钟周期内读取其操作数。

<3>执行。将其中的一个操作数移位,并在ALU中产生结果。如果指令是Load或Store指令,则在ALU中计算存储器的地址。

<4>存储器访问。如果需要,则访问数据存储器;否则,ALU只是简单地缓冲一个时钟周期,以便使所有指令具有同样的流水线流程。

<5>写回。将指令的结果写回到寄存器组。包括任何从存储器读取的数据。

3)ARM9流水线(续)

为什么用5级流水线。一给定程序的执行时间

Ninst为程序中的指令数,CPI为每条指令的平均时钟周期数, fclk为处理器的时钟频率。

提高处理器性能的两种方式:

提高时钟频率

简化流水线每一级的逻辑任务 增加级数

减少指令的平均时钟周期数CPI

将指令与数据存储器分开(Harvard)、减少阻塞

3)ARM9流水线(续)

5级流水线与3级流水线的比较

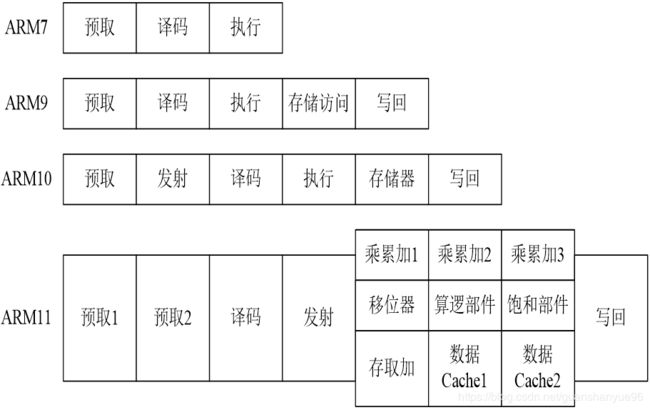

4)ARM10和ARM11流水线

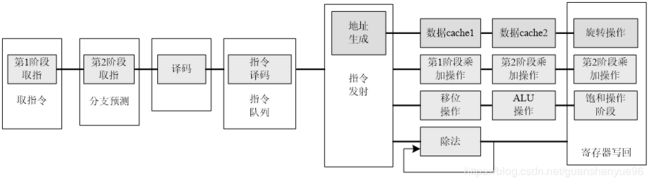

5)Cortex-R4流水线

Cortex-R4处理器的流水线为8级。其特点是双发射指令流水线,含动态分支预测,执行速度达到1.6 MIPS/MHz(Dhrystone基准测试程序)。其中前3级是指令预取单元PFU,包括第1阶段取指,第2阶段取指和译码。

9 ARM协处理器

ARM通过增加硬件协处理器来支持对其指令集的通用扩展。简单的ARM核提供板级协处理器接口,协处理器可以作为一个独立的元件接入。

ARM最多可支持16个协处理器(CP0~CP15)

CP15( System Control Coprocessor)为系统控制协处理器,诸如MMU、Cache配置、紧耦合处理器、写缓存配置之类的存储系统管理工作由协处理器CP15完成。

CP15可以包含16个32位寄存器

编号为C0~C15。

用户只能够在特权模式下使用MRC和MCR指令来访问CP15中的寄存器。

CP15主要用作MMU (Memory Management Unit)与MMP( Memory Protection Unit)

MMU的两个主要功能是:

1. 将虚地址转换成物理地址

2. 控制内存的访问权限

MMP 的主要功能是划分内存保护区、设置访问权限

读/写、只读和不可访问等

第二章测试

1、ARM有几种工作状态?

2、ARM有哪些工作模式?哪些模式享有特权等级?哪些模式属于异常模式?模式由CPSR中的哪些位决定?

3、ARM在ARM状态下的寄存器有哪些?其中,R13、R14与R15分别是用于什么目的?在Thumb状态下的寄存器又有哪些?

4、标出当前程序状态寄存器CPSR中各位的功能。

5、写出ARM处理器异常中断的类型,对应的工作模式及其对应的中断向量。

6、发生异常中断时ARM处理器如何响应?

7、简述ARM三级流水流线中每一级所做的工作及占用的资源

第3章ARM 指令系统

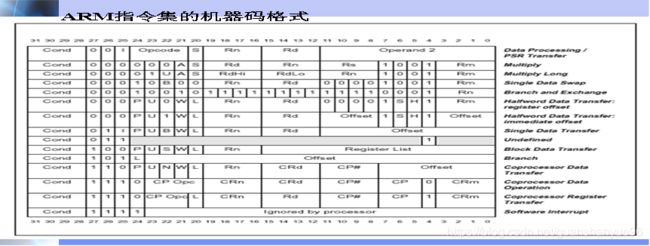

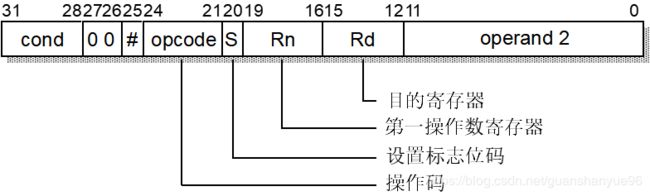

ARM指令的机器码格式 指令的机器码格式是指汇编指令的二进制数编码表示。汇编指令由助记符、目标寄存器、第一操作数寄存器、第二操作数、条件、标志位等部份组成。机器码格式规定如何用二进制数来表示这些部份。

ARM指令的机器码格式按指令类别制定,不同类别的指令机器码格式不同

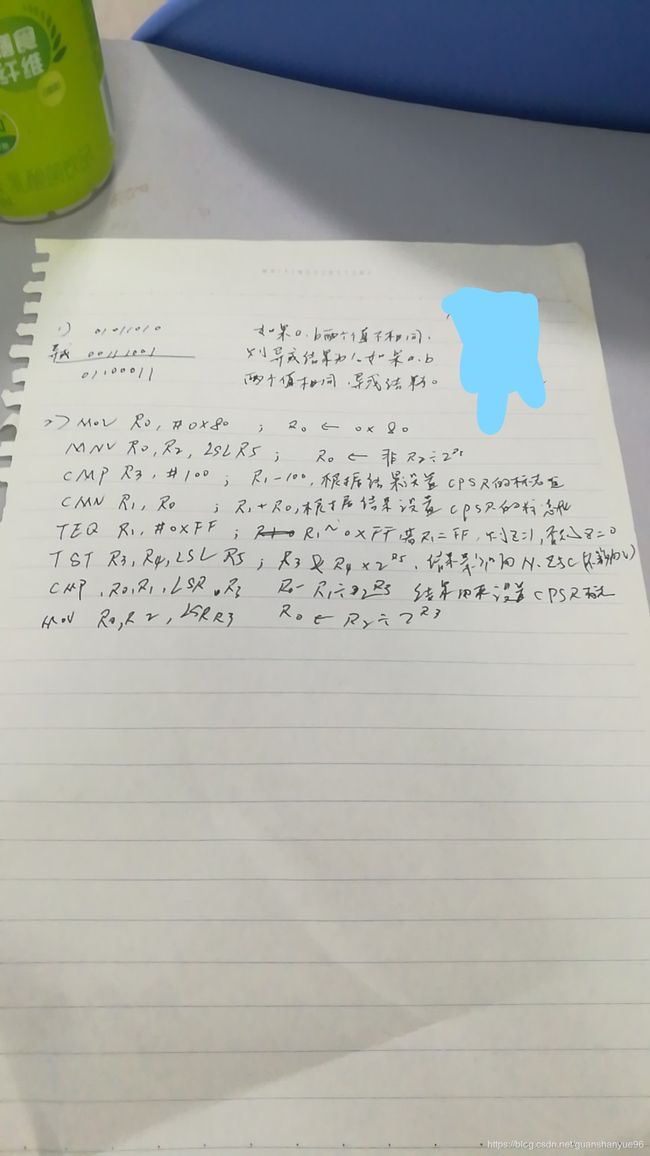

条件码表1

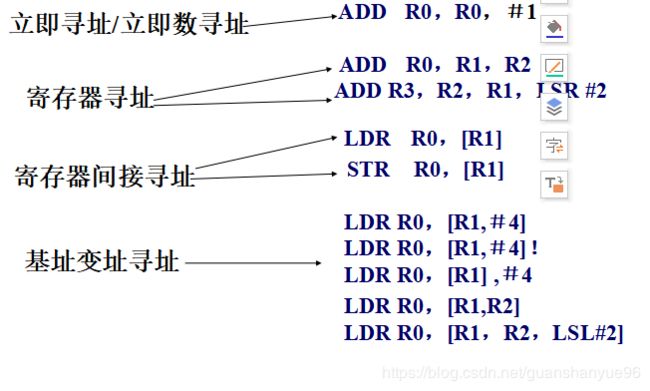

2 ARM指令的寻址方式

什么是寻址方式

寻找操作数地址的方式或寻找操作数的方式称为寻址方式。 如在计算2+3=?时,需先找到2和3的地址,才能把它们取出来进行加法操作,寻找2和3的地址的方式即寻址方式。

ARM有哪些寻址方式?

2 ARM指令的寻址方式

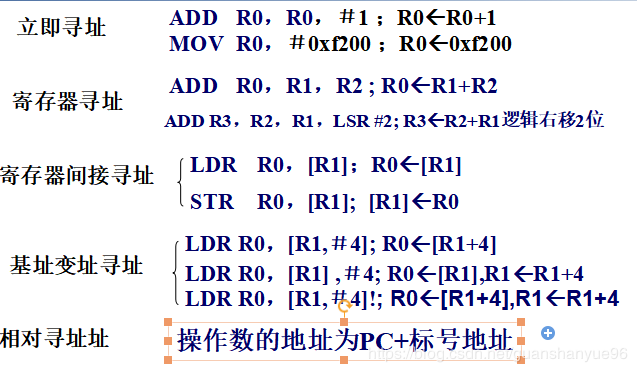

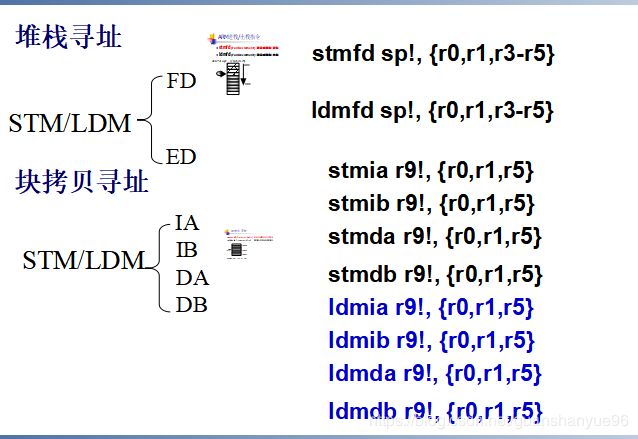

ARM的寻址方式

1)立即寻址

2)寄存器寻址

3)寄存器间接寻址

4)基址加偏址寻址

5)堆栈寻址

6)块拷贝寻址

7)相对寻址

1)立即寻址

立即寻址/立即数寻址:操作数直接包含在指令中,只要取出指令也就取到了操作数,这个操作数被称为立即数。

例如:

ADD R0,R0,#1 /*R0←R0+1*/

ADD R0,R0,#0x3f /*R0←R0+0x3f*/

第二个操作数即为立即数,以“#”为前缀,

1)立即寻址

立即数表示 十进制另加“0d”或省略。 十六进制立即数另加“0x”或“&”, 二进制另加“0b”或“2_”;

立即寻址特点 速度快。为什么?

能使用的立即数有限。为什么?

1)立即寻址

立即寻址中立即数范围有多大?

32位指令码中只能用12位表示立即数,最大为212=4096

如何才能使这12bits能够表示更大范围的数?

将12位分成两部份,低8位表示一个立即数,高4位表示循环右移的位数,最终得到的立即数为:

这种表示方式虽然复杂,但写汇编时程序员只需写出需要使用的立即数即可,后面的事情编译器自会去做。

2)寄存器寻址

寄存器寻址:操作数在寄存器中,指令中的地址码为寄存器编号,寄存器的内容即为操作数。执行效率较高的寻址方式。例

![]()

寄存器寻址是各类微处器经常采用的寻址方式,是执行效率较高的寻址方式。。

2)寄存器寻址

寄存器寻址中,第二寄存器操作数在与第一操作数结合前可先进行移位操作,移位位数可以是一5位立即数或一寄存器R值。例 ADD R3,R2,R1,LSR #2 ;R3<-R2+R1÷4

ADD R3,R2,R1,LSR R4 ;R3<-R2+R1÷2R4

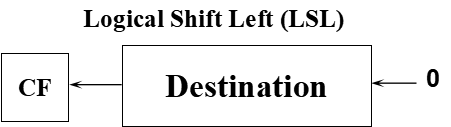

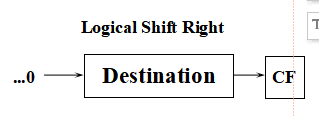

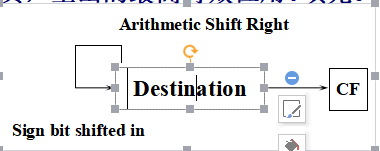

移位类型

LSL(Logical Shift Left)逻辑左移:向左移,最后移出的进CF,空出的最低有效位用零填充

LSR(Logical Shift Right)逻辑右移:向右移,最后移出的进CF,空出的最高有效位用零填充

ASL(Arithmetic Shift Left)算术左移:向左移,同LSL

ASR(Arithmetic Shift Right)算术右移:向右移,最后移出的进CF,空出的位用符号位填。源操作数为正,空出的最高有效位用零填充;源操作数为负,空出的最高有效位用1填充。

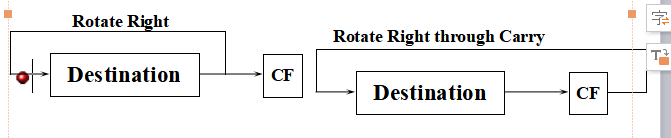

ROR(Rotate Right)循环右移:移出的最低位依次填入空出的最高位,最后移出的进C标志位。

RRX(Rotate Right Extended by 1 Place)带扩展循环右移:寄存器的内容循环右移1位进入C标志位,空出的位用原来的C标志位填充。

3)寄存器间接寻址

寄存器间接寻址:寄存器中的值作为操作数的地址,而操作数本身存放在该地址所指向的存储器区中。

例

LDR R0,[R1] ;R0←[R1]

STR R0,[R1] ;[R1]←R0

第一条指令将R1的值为地址的存储器中的数据传送到R0中。第二条指令将R0的值传送到R1的值为地址的存储器中。

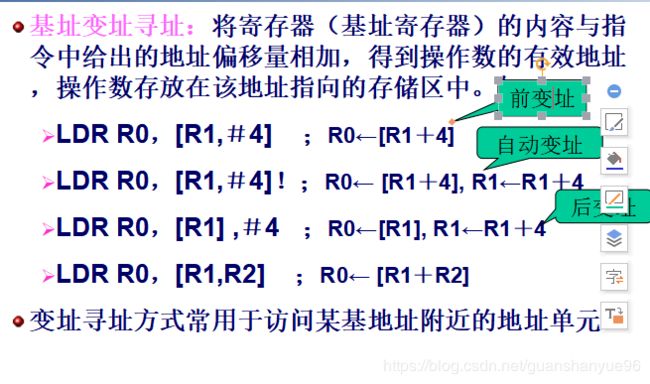

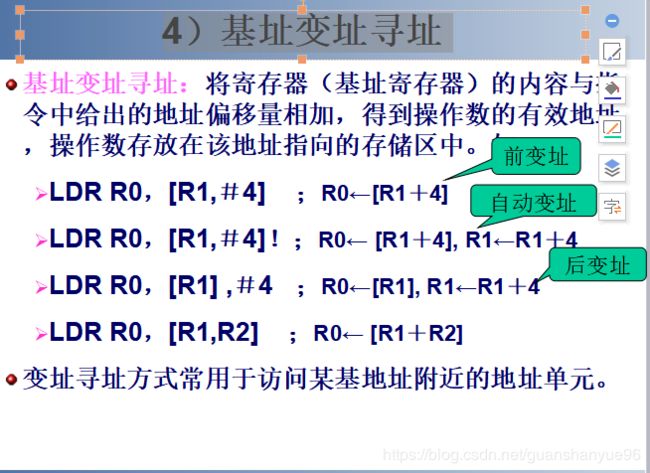

4)基址变址寻址

4)基址变址寻址

用线将下列寻址方式与对应的指令连起来

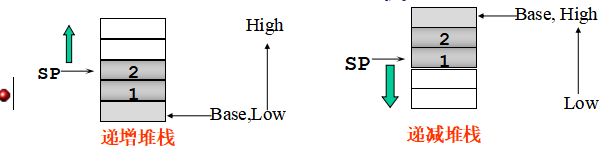

5)堆栈寻址

操作数在堆栈中,堆栈是一块用于保存数据的连续内存区,按先进后出FILO(First In Last Out)的顺序进行存取操作,使用一个称作堆栈指针的专用寄存器指示当前的操作位置。根据堆栈指针指向位置的方式可分为如下两种堆栈:

满堆栈(Full Stack):当堆栈指针指向最后压入堆栈或第一个要读出的数据时。

空堆栈(Empty Stack):当堆栈指针指向最后压入堆栈的数据的上/下一个空位或第一个要读出的数据上/下一个空位时。

根据堆栈指针变化的方式可分为如下两种堆栈

递增堆栈(Ascending Stack) :当堆栈由低地址向高地址生成时,称为递增堆栈

递减堆栈(Decending Stack):当堆栈由高地址向低地址生成时,称为递减堆栈

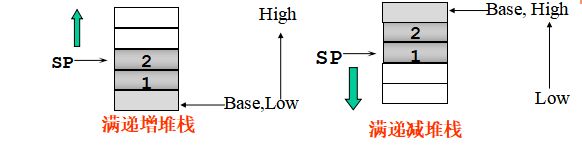

堆栈的四种工作方式

满递增堆栈:堆栈指针指向最后压入或第一个要读出的数据,且由低地址向高地址生长。

满递减堆栈:堆栈指针指向最后压入或第一个要读出的数据,且由高地址向低地址生长。

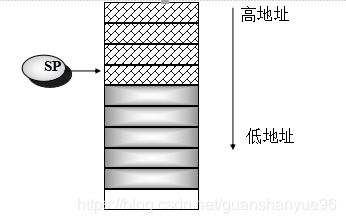

5)堆栈寻址

堆栈的工作方式一般在处理器设计时就定好了的,用户不能更改。

ARM堆栈的工作方式为满递减堆栈

例

ARM

STMFD SP! {r0,r1,r3-r5} ; r0,r1,r3-r5入栈

LDMFD SP! {r0,r1,r3-r5} ; r0,r1,r3-r5出栈

Thumb

PUSH {r0,r1,r3-r5} ; r0,r1,r3-r5入栈

POP {r0,r1,r3-r5} ; r0,r1,r3-r5出栈

stmfd (Full Decrement) 满递减堆栈-进栈

stmfd sp!, {r0,r1,r3-r5}

stmfd (Full Decrement) 满递减堆栈-进栈

stmfd sp!, {r0,r1,r3-r5}

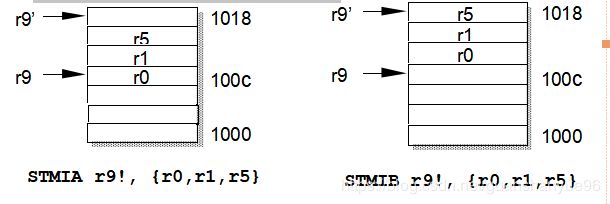

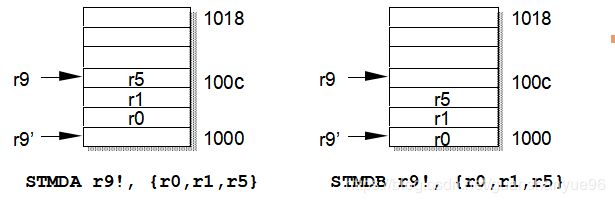

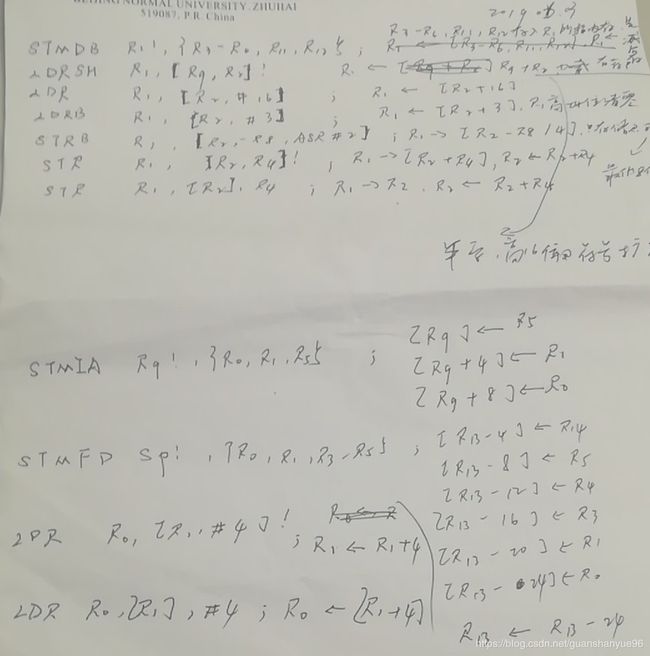

6)块拷贝寻址/多寄存器寻址

多寄存器寻址中,用一条指令把存储器中的一块数据加载到多个寄存器,或把多个寄存器中的内容保存到存储器中。寻址操作中的寄存器可以是R0~R15或其子集。

LDM/STM加下列后缀即成为多寄存器寻址指令

IA(Increment After) : 操作完成后地址增

IB(Increment Before) :操作完成前地址增

DA(Decrement After) :操作完成后地址减

DB(Decrement Before) :操作完成前地址减

STMIA r9!, {r0,r1,r5} ;r0/1/5存入r9所指内存,先存后加 STMIB r9!, {r0,r1,r5} ; r0/1/5存入r9所指内存,先加后存

STMDA r9!, {r0,r1,r5} ;r0/1/5存入r9所指内存,先存后减

STMDB r9!, {r0,r1,r5} ;r0/1/5存入r9所指内存,先减后存

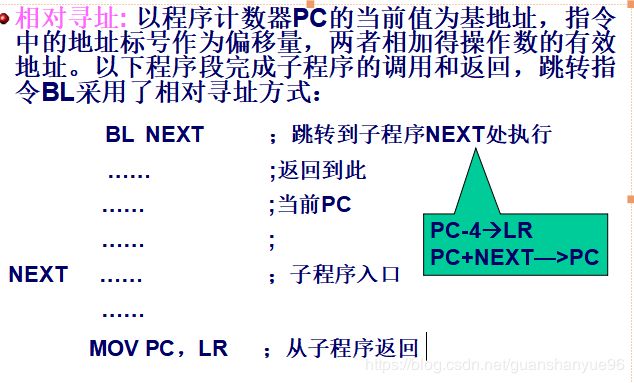

7)相对寻址

ARM的寻址方式复习

ARM的寻址方式(复习续)

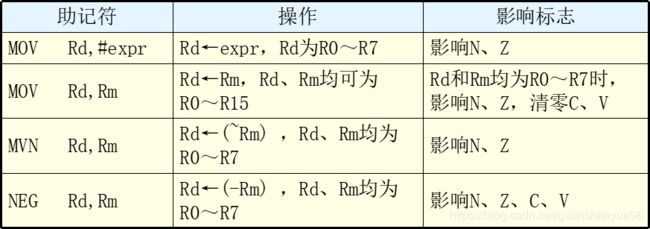

数据传送指令

数据传送是指数据在寄存器与存储器之间的传送。其中,从存储器到寄存器的传送称为加载(Load),从寄存器到存储器的传送称为存储(Store),故数据传送指令也称为加载/存储(Load/Store)指令或存储器访问指令。

ARM处理器采取统一编址方式进行编址,即所有I/O都和存储单元一样,同属ARM的地址空间,与存储器一起统一编址,数据在I/O与寄存器间的传送也使用(Load/Store)指令完成。

ARM采用Load/Store结构,即除Load/Store指令能在存储器与寄存器间进行数据传送外,其它指令均无此功能,也就是说除Load/Store外的指令均无访存功能。。

数据传送指令可分为字与无符号字节传送指令、半字与有符号字节传送指令、块数据传送指令及交换指令几类,下面分别加以介绍。

5)异常产生指令

执行SWI指令时,将产生软中断,ARM处理器硬件会执行下列操作:

(1)把CPSR拷贝到管理模式下的SPSR中

(2)修改状态寄存器中相应位:

①模式控制位修改为:10011(SVC模式)

②禁止IRQ中断,使CPSR[7]=1

(3)把返回地址拷贝到SVC下的R14中

(4)把中断向量0x8赋给PC

随后,程序执行0x8处的指令,通常是一个跳转指令或PC赋值指令

将软中断处理程序设计为总处理程序与子处理程序的两层结构

由总处理程序提取软中断指令中的立即数,并根据立即数(功能号)的不同跳转到不同的子处理程序处

由子处理程序进行具体的软中断事务处理

可用如下两种方式将软中断指令中的立即数提取出来

用寄存器传递立即数

直接提取SWI指令中的立即数

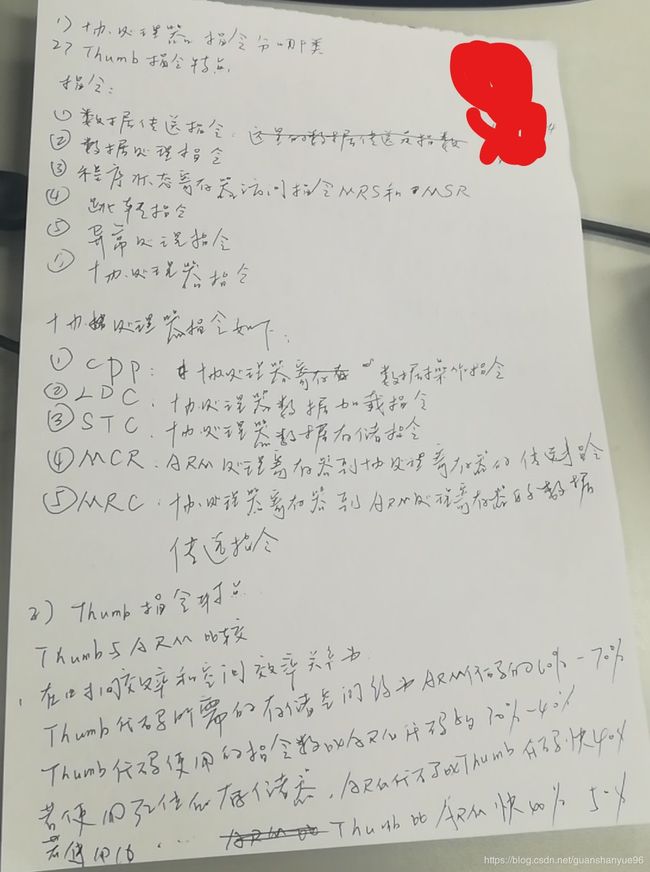

3 ARM指令集

数据传送指令

数据处理指令

状态寄存器访问指令

跳转移指令

异常产生指令

伪指令

伪指令( pseudo-instruction)不是真正的ARM指令或Thumb指令,这些伪指令在编译器对源程序进行汇编处理时被替换成相应的ARM指令或Thumb指令序列.ARM伪指令有如下四条:

ADR:小范围地址读取伪指令

ADRL:中等范围地址读取伪指令

LDR:大范围地址读取伪指令

NOP:空操作伪指令

6)ARM汇编语言的伪指令

Thumb指令集概述

Thumb 是16-bit 指令集

代码密度高 (总代码大小约为ARM指令的65%)

使用窄总线存储器时可以大大提高性能。

是 ARM 指令集的一个子集,不是一个完整的指令集(Thumb-2除外)

ARM和Thumb之间可通BX 指令进行切换

没有条件后缀(B除外)

源、目的寄存器必须相同

没有S后缀(均可影响标志位)

仅能使用低寄存器(少数指令除外)

常数大小有限制

不能使用在线移位器(有单独的移位指令)

Thumb指令可分为如下几类:

1)数据传送指令

2)数据处理指令

3)分支指令

4)杂项指令

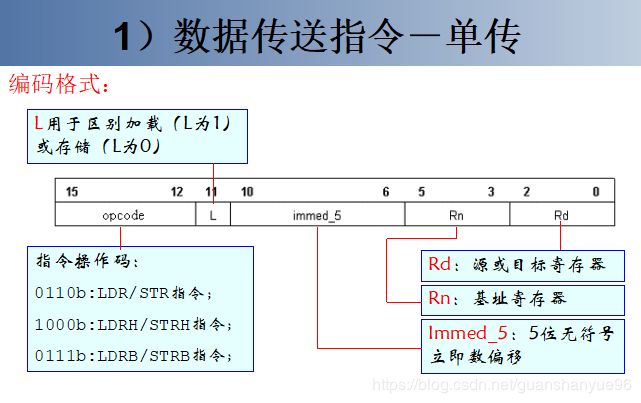

1)数据传送指令-单传

一次传送一个字节、一个半字或一个字,用LDR/STR完成

1)数据传送指令-单传

汇编格式一:

LDR Rd,[Rn,#immed_5×4]

STR Rd,[Rn,#immed_5×4]

LDRH Rd,[Rn,#immed_5×2]

STRH Rd,[Rn,#immed_5×2]

LDRB Rd,[Rn,#immed_5×1]

STRB Rd,[Rn,#immed_5×1]

Rd 表示加载或存储的寄存器,必须为R0~R7。

Rn 表示基址寄存器,必须为R0~R7。

immed_5×N 表示立即数偏移量,其取值范围为(0~31)×N

应用示例:

LDR R0,[R1,#0x4]

STR R3,[R4]

LDRH R5,[R0,#0x02]

STRH R1,[R0,#0x08]

LDRB R3,[R6,#20]

STRB R1,[R0,#31]

注意:进行字数据访问时,必须保证传送地址为32位对齐(字对齐)。进行半字数据访问时,必须保证传送地址为16位对齐(半字对齐)。

汇编格式二:

LDR Rd,[Rn,Rm] ;加载一个字数据

STR Rd,[Rn,Rm] ;存储一个字数据

LDRH Rd,[Rn,Rm] ;加载一个无符号半字数据

STRH Rd,[Rn,Rm] ;存储一个无符号半字数据

LDRB Rd,[Rn,Rm] ;加载一个无符号字节数据

STRB Rd,[Rn,Rm] ;存储一个无符号字节数据

LDRSH Rd,[Rn,Rm] ;加载一个有符号半字数据

LDRSB Rd,[Rn,Rm] ;存储一个有符号半字数据

其中:Rd 表示加载或存储的寄存器。必须为R0~R7。

Rn 表示基址寄存器。必须为R0~R7。

Rm 表示内含数偏移量的寄存器,必须为R0~R7 。

注意:以PC作为基地址的相对偏移寻址指令只有LDR,而没有STR指令。

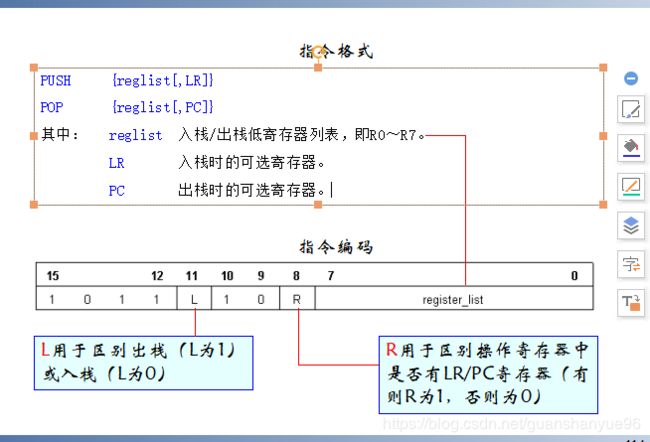

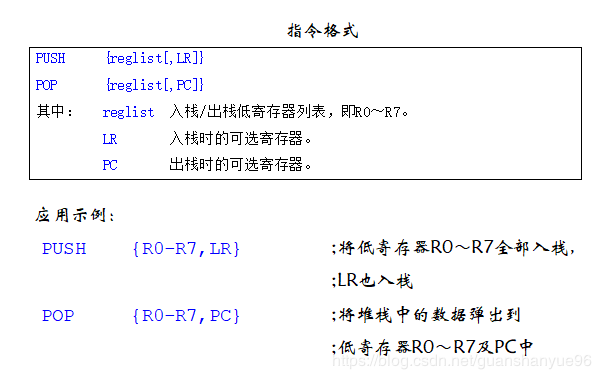

1)数据传送指令-入栈及出栈

2) 数据处理指令

Thumb数据处理指令涵盖了编译器需要的大多数操作。大部分的Thumb数据处理指令采用2地址格式,不能在单指令中同时完成一个操作数的移位及一个ALU操作。所以数据处理操作比ARM状态的更少,并且访问寄存器R8~R15受到限制。数据处理指令分为两类:

数据移动指令

算术逻辑运算指令

Thumb数据处理指令——数据移动指令

Thumb数据处理指令——算术逻辑运算指令

20190311

(1)嵌入式系统的定义

(2)嵌入式与PC的区别

(3)嵌入式系统与单片机的区别

(4)嵌入式系统的特征

(5)嵌入式系统的应用

20190326

(1)ARM支持模式

(2)如何变换模式

20190401

(1)R14作用

(2)用户->快中断

(3)R8-R12是否需要保存

20190408

(1)R14、R15、R13

(2)CPSR

20190415

(1)异常中断的类型?发生条件?

(2)为什么发生中断时,它的PC要放在R14_类型中,而不是放在普遍的PC中?

20190506

(1)ARM有几种状态

(2)ARM有哪些工作模式,哪些模式具有特权等级

(3)ARM在ARM状态下的寄存器有哪些?

(4)写出ARM处理器异常中断的类型,对应的工作模式,及对应的中断向量

(5)发生异常中断时ARM的处理器有什么异常

20190507

(1)

LSL #3

LSR #5

ASL #4

ASR #2

(2)修改当前寄存器CPSR的对应位

(3)写出ARM异常中断的类型,对应的工作模式,及其对应的中断向量

(4)简述ARM三级流水线每一级所做的工作,占用的资源

(5)发生异常中断时ARM处理器如何响应

20190521

(1)ARM寻址方式

20190603

20190610

20190617

20190625

1、P14 经简指令集和复杂指令集的区别是什么?

ARM架构属RISC体系架构,即精简指令集计算机体系架构。ARM架构是世界上首个商用RISC架构,在此之前,计算机的体系架构为复杂指令集计算机架构,即CISC架构。故要理解RISC,还得从CISC说起。

2、什么是嵌入式系统?

嵌入式系统是嵌入到对象体系中的专用计算机。

3、CISC(复杂)与RISC(简单)的区别?

(1)RISC指令格式和长度固定,类型少,功能简单,寻址简单方式少;CISC指令长度不等,类型多,功能复杂。

(2)RISC使用硬连线指令译码逻辑,易于流水线实现;CISC采用微码ROM译码。

(3)RISC大多数指令单周期完成;CISC指令多为多周期完成。

(4)RISC除Load/Store指令外,所有指令只对寄存器操作;大多数CISC指令皆可对主存及寄存器操作。

4、怎么改变ARM处理器核的工作模式。

(1)通过CRSR复位来改变工作模式。

(2)还可通过软中断来改变。

5、什么是特权模式,什么是异常模式。

(1)用户模式外的其他6种模式称为特权模式。

(2)特权模式中除系统模式外的其他5种模式称为异常模式。

6、ARM处理器核的工作模式有哪几种。

(1)User - 正常用户模式,程序正常执行模式。

(2)FIQ - 处理快速中断,支持告诉数据传送或通道处理。

(3)IRQ - 处理普通中断。

(4)SVC - 操作系统保护模式,处理软件中断SWI。

(5)中止 - 处理存储器故障,实现虚拟存储器和存储器保护。

(6)未定义 - 处理未定义的指令陷阱、支持硬件协处理器的软件仿真。

(7)系统 - 运行特权操作操作系统任务。

7、寄存器分组。

(1)R0-R7 - 不分组寄存器。是所有处理器模式下共用的寄存器,在模式切换时必须压入堆栈保护。

(2)R8-R14 - 发生中断时,分组寄存器。不需入栈保护。

(3)R13,R14

R13 - 通用寄存器,常当作:堆栈指针寄存器,用SP表示,R13和SP皆指同一个寄存器。保存堆栈当前入口

R14 - 通用寄存器,常当作:链接寄存器,用LR表示,故R14与LR均指同一个寄存器。保存下一条指令的地址

8、CPSR中各位的含义。

[31:28]为条件标志位。其中

[31]为N标志位,即正负标志位。N=1为正,N=0为负。

[30]为Z标志位,即零标志位。Z=1,则表示运算的结果为零;若Z=0,则表示运算结果非零。

[29]为C标志位,即进/借位标志位。有4种情况:

加法运算(包括比较)