Verilog 多路选择器(MUX)

Verilog 多路选择器(MUX)

一般的遇到的情况都是单独的output 信号,对于inout信号,我们怎么做多路选择器呢?

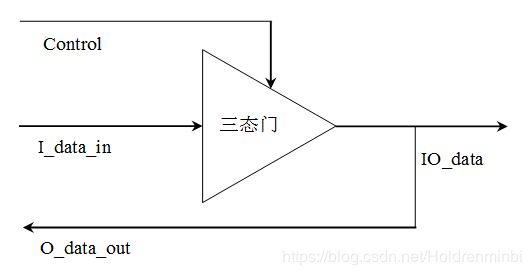

1、 inout、input、output的不同

2、inout电路

3、两路选择器

3.1 inout module

这是一个简单的inout使用模块

`timescale 1ns / 1ps

// Create Date: 2020/03/10 11:39:00

// Design Name:

// Module Name: mux_sub_function

//////////////////////////////////////////////////////////////////////////////////

module mux_sub_function (

input clk,

input reset_n,

input data_en_i,

output reg data_en_o,

inout [7:0] data_bus,

output[7:0] data_bus_in_o

);

parameter add1 = 1;

reg [7:0] data;

reg rev_r;

reg rev;

reg [2:0] count;

always@(posedge clk)

if(!reset_n)

begin

count <= 0;

data_en_o <=0;

rev <= 0;

rev_r <= 0;

end

else if(count ==0)

begin

rev <= ~rev;

count <= count + add1;

end

else if(rev_r != rev && !data_en_i )

begin

rev_r <= rev;

data_en_o <= ~data_en_o;

end

else

begin

count <= count + add1;

rev <= rev;

rev_r <= rev_r;

end

always@(posedge clk)

if (data_en_o )

data <= data + add1;

else if (data_en_i )

data <= data_bus ;

assign data_bus_in_o = data_bus;

assign data_bus = data_en_o&&!data_en_i ? data : 8'bz;

endmodule

3.2 两路inout mux切换

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Create Date: 2020/03/10 11:27:37

// Design Name:

// Module Name: mux_inout_1_2

//////////////////////////////////////////////////////////////////////////////////

module mux_inout_1_2(

input clk,

input reset_n,

input [3:0] mux_ctrl,

output f_bus_en_o,

input f_bus_en_i,

inout [7:0] f_bus,

output [7:0] f_bus_i,//data

output [7:0] f_bus_o,//data

input temp

);

wire f1_data_en_i;

wire f1_data_en_o;

wire [7:0] f1_data_bus;

wire [7:0] f1_data_bus_o;

wire f2_data_en_i;

wire f2_data_en_o;

wire [7:0] f2_data_bus;

wire [7:0] f2_data_bus_o;

// To top monitor

assign f_bus_i = f_bus ;

assign f_bus_o = mux_ctrl ? f1_data_bus_o : f2_data_bus_o ;

// in

assign f1_data_en_i = mux_ctrl ? f_bus_en_i : 8'bz ;

assign f2_data_en_i = mux_ctrl ? 8'bz : f_bus_en_i;

assign f1_data_bus = f1_data_en_i ? f_bus : 8'bz ;

assign f2_data_bus = f2_data_en_i ? f_bus : 8'bz ;

//out

assign f_bus = mux_ctrl ? ( f1_data_en_o ? f1_data_bus :8'bz):( f2_data_en_o ? f2_data_bus : 8'bz);

assign f_bus_en_o = mux_ctrl ? f1_data_en_o : f2_data_en_o ;

mux_sub_function #(.add1(2)) mux_sub_f1(

.clk (clk) , // input clk,

.reset_n (reset_n) , // input reset_n,

.data_en_i (f1_data_en_i ) , // input data_en_i,

.data_en_o (f1_data_en_o ) , // output data_en_o,

.data_bus (f1_data_bus ) , // inout [7:0] data_bus,

.data_bus_in_o (f1_data_bus_o) // output [7:0] data_bus_in_o

);

mux_sub_function #(.add1(3)) mux_sub_f2(

.clk (clk) , // input clk,

.reset_n (reset_n) , // input reset_n,

.data_en_i (f2_data_en_i ) , // input data_en_i,

.data_en_o (f2_data_en_o ) , // output data_en_o,

.data_bus (f2_data_bus ) , // inout [7:0] data_bus,

.data_bus_in_o (f2_data_bus_o) // output [7:0] data_bus_in_o

);

endmodule

3.3 Mux testbench

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Create Date: 2020/03/10 14:35:18

// Design Name:

// Module Name: mux_inout_1_2_tb

//////////////////////////////////////////////////////////////////////////////////

module mux_inout_1_2_tb();

reg clk ;

reg reset_n ;

reg [3:0] mux_ctrl ;

reg f_bus_en_i ;

wire [7:0] f_bus ;

wire [7:0] f_bus_i ;

wire [7:0] f_bus_o ;

mux_inout_1_2 mux_inout(

.clk (clk ) ,

.reset_n (reset_n ) ,

.mux_ctrl (mux_ctrl ) ,

.f_bus_en_o (f_bus_en_o ) ,

.f_bus_en_i (f_bus_en_i ) ,

.f_bus (f_bus ) ,

.f_bus_i (f_bus_i ) ,

.f_bus_o (f_bus_o ) ,

.temp ( )

);

initial clk = 1;

always #1 clk = ~clk;

wire [7:0] f_bus2tb;

reg [7:0] data;

assign f_bus2tb = f_bus;

assign f_bus = (f_bus_en_o==0) ? data : 8'bz ;

initial begin

#4;reset_n = 1;

f_bus_en_i = 0;

mux_ctrl =0;

#2;reset_n = 0;

#2;reset_n = 1;

f_bus_en_i = 1;

mux_ctrl =1;

data = 0;

#2; data = 1;

#2; data = 2;

#2; data = 3;

#2; data = 4;

#2; data = 5;

#2; data = 6;

#2;f_bus_en_i = 0;

#16;

#2; mux_ctrl = 0;

f_bus_en_i = 1;

#2; data = 1;

#2; data = 2;

#2; data = 3;

#2; data = 4;

#2; data = 5;

#2; data = 6;

#2;

#2;f_bus_en_i = 0;

#40;

$stop;

$finish;

end

endmodule