ARM架构学习

ARM架构

- ARM架构

- ARM处理器简介

- RISC指令集特点

- ARM历史

- 简单的内核工作方法分类

- ARM 的big.LITTLE

- ARM V8架构

- ARMv8 -a架构

- ARMv8-A架构模块

- AArch64 Exception level

- ARM A8架构

- 引用

ARM架构

具体可以在arm开源设计进行了解。http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0407e/BABFAHID.html

ARM处理器简介

ARM架构过去称作进阶精简指令集机器(AdvancedRISCMachine,更早称作:AcornRISCMachine),是一个32位精简指令集(RISC)处理器架构,其广泛地使用在许多嵌入式系统设计。由于节能的特点,ARM处理器非常适用于移动通讯领域,符合其主要设计目标为低耗电的特性。

在今日,ARM家族占了所有32位嵌入式处理器75%的比例,使它成为占全世界最多数的32位架构之一。ARM处理器可以在很多消费性电子产品上看到,从可携式装置(PDA、移动电话、多媒体播放器、掌上型电子游戏,和计算机)到电脑外设(硬盘、桌上型路由器)甚至在导弹的弹载计算机等军用设施中都有他的存在。在此还有一些基于ARM设计的派生产品,重要产品还包括Marvell的XScale架构和德州仪器的OMAP系列。

RISC指令集特点

(1)指令集——RISC减少了指令集的种类,通常一个周期一条指令,采用固定长度的指令格式,编译器或程序员通过几条指令完成一个复杂的操作。而CISC指令集的指令长度通常不固定;

(2)流水线——RISC采用单周期指令,且指令长度固定,便于流水线操作执行;

(3)寄存器——RISC的处理器拥有更多的通用寄存器,寄存器操作较多。例如ARM处理器具有37个寄存器;

(4)Load/Store结构——使用加载/存储指令批量从内存中读写数据,提高数据的传输效率;

(5)寻址方式简化,指令长度固定,指令格式和寻址方式种类减少。

ARM历史

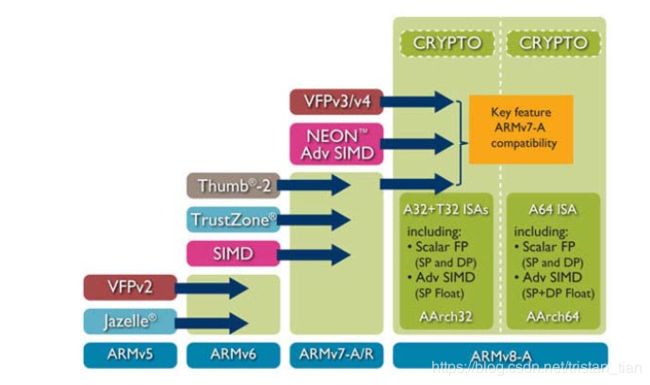

- 从1995年,ARMV4(主要对应ARM7 family)开始到现在ARM RISC体系结构到现在已经演化了20多年。从设计一开始ARM就关注到了低功耗。

- 到2011年,所有的ARM-Cotex family都被设计成使用ARMV7架构。

- ARMV8架构,现在的架构

简单的内核工作方法分类

- 用户模式(user):正常程序执行模式;

- 快速中断模式(FIQ):高优先级的中断产生会进入该种模式,用于高速通道传输;

- 外部中断模式(IRQ):低优先级中断产生会进入该模式,用于普通的中断处理;

- 特权模式(Supervisor):复位和软中断指令会进入该模式;

- 数据访问中止模式(Abort):当存储异常时会进入该模式;

- 未定义指令中止模式(Undefined):执行未定义指令会进入该模式;

- 系统模式(System):用于运行特权级操作系统任务;

- 监控模式(Monitor):可以在安全模式和非安全模式之间切换;

ARM 的big.LITTLE

这个多核处理器的大核和小核。比图基于big.LITTLE技术的八核处理器,并没有将传统内核放在单一的处理器上,而是一分为二,其中一个使用了4个“小核心”,另一个则使用了4个“大核心”,这两个“核心”都有着自己独立的速度和性能。通过两大核心自主运行,搭载Big.little技术的处理器比之前的手机CPU更加高效,毕竟后者只有一个或者两个内核。

ARM V8架构

ARMv8 -a架构

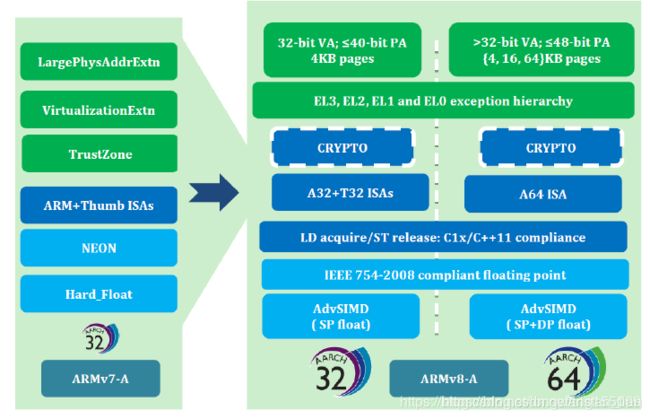

ARMv8(当前只有A系列,即ARMv8-A)架构,是ARM公司为满足新需求而重新设计的一个架构,是近20年来,ARM架构变动最大的一次。它引入的Execution State、Exception Level、Security State等新特性,已经和我们对旧的ARM架构的认知,有很大差距了。

由于处理器性能越来越强,运行于其上的软件也来越复杂,复杂到单一应用对内存的需求可能超出32-bit架构所能支持的最大内存(4G),这就是Large memory需求的起因。不过,后来的Cortex-A15(ARMv7架构)通过Large Physical Address Extensions (LPAE) 技术,可以支持高达40bits的物理地址空间。但受限于32-bit的指令集,虚拟地址空间依旧只有32bits(4G),如果有应用需要更大的虚拟内存,怎么办?只能定义一个新的架构,使用64-bit的指令集(也即我们常说的ARM64)。

当然,ARMv8并不仅仅是为了解决虚拟地址的问题,它也要解决现有架构的一些问题。不过,新的问题又来了:一个新的架构?用户为什么要使用新的架构?因此,ARMv8的定义,必须先满足如下前提条件:

1)对上兼容。

2)能解决现存架构的已知问题。

3)相比现存架构,必须具备优势明显的新特性,哪怕软件从来不使用这些新特性

基于上面的前提条件,ARMv8-a架构的主要特性包括:

- 新增一套64-bit的指令集,称作A64。

- 由于需要向前兼容ARMv7,所以同时支持现存的32-bit指令集,称作A32和T32(也即我们熟悉的ARM和Thumb指令集)。

- 定义AArch64和AArch32两套运行环境(称作Execution state),分别执行64-bit和32-bit指令集。软件可以在需要的时候,切换Execution state。

- AArch64最大的改动,使用新的概念(exception level),重新解释了processor mode、privilege level等概念。

- 在ARMv7 security extension的基础上,新增security model,支持安全相关的应用需求。

- 在ARMv7 virtualization extension的基础上,提供完整的virtualization框架,从硬件上支持虚拟化。

ARMv8-A架构模块

- ARM CoreSight 技术,用于debug使用 Generic

- Interrupt Controller(GIC)中断控制器

- Memory Protection Unit(MMU)MMU用于将虚拟地址转化为物理地址 每个Core中都有一个L1

- 指令和数据Cache,一般每四个core会在一个Cluster中的 存在一个L2 cache

- SCU(Snoop Control Unit )维护多CPU核之间的数据缓存的一致性,主要作用是CPU控制缓存的操作。

- ACP(加速器一致性接口)

- 多个core可能通过Coherent,Bus通信

AArch64 Exception level

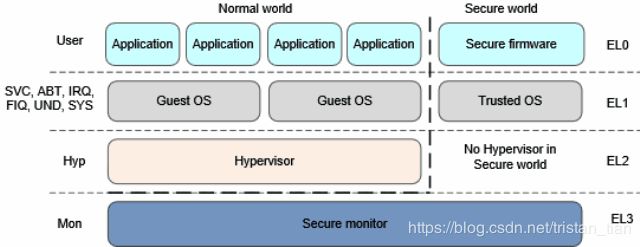

Exception level,是ARMv8-a引入的一个新概念,用于整合之前架构中processor mode和privilege level相关的功能。

在ARMV7-a架构中,处理器可以工作在多种模式。不同模式有不同的硬件访问权限(privilege level),也和各类异常一一对应,有自己独有的寄存器。ARMv7-a增加了两个模式:Monitor和Supervisor,分别用于security扩展和virtualization扩展。

ARMv8-a就把processor mode的概念去掉了,取而代之的是4个固定的Exception level,简称EL0-EL3。同时,也淡化了privilege level的概念。Exception level本身就已经包好了privilege的信息,即ELn的privilege随着n的增大而增大。

ARMv8-a就把processor mode的概念去掉了,取而代之的是4个固定的Exception level,简称EL0-EL3。同时,也淡化了privilege level的概念。Exception level本身就已经包好了privilege的信息,即ELn的privilege随着n的增大而增大。

ARMv8-a Exception level有关的说明如下:

1)首先需要注意的是,AArch64中,已经没有User、SVC、ABT等处理器模式的概念,但ARMv8需要向前兼容,在AArch32中,就把这些处理器模式map到了4个Exception level。

2)Application位于特权等级最低的EL0,Guest OS(Linux kernel、window等)位于EL1,提供虚拟化支持的Hypervisor位于EL2(可以不实现),提供Security支持的Seurity Monitor位于EL3(可以不实现)。

3)只有在异常发生时(或者异常处理返回时),才能切换Exception level(这也是Exception level的命名原因,为了处理异常)。当异常发生时,有两种选择,停留在当前的EL,或者跳转到更高的EL,EL不能降级。同样,异常处理返回时,也有两种选择,停留在当前EL,或者调到更低的EL。

- 在ARMv7架构下只能访问最大4GB的地址空间,而在ARMv8-A可以访问更大的地址空间。

- ARMv7只支持4KB的page,在ARMv8-A下可以支持多种页类型(4K,16K, 64K),地址范围【32, 48】最大48位,所以ARMv8-A架构下下应用程序可以访问更大的虚拟地址空间

- ARMv8-A首次引入了Exception Level的概念,在ARMv7下使用的是PL0, PL1, PL2。 而在ARMv8-A下使用的是EL0-EL3

- ARMv8-A增加了通用寄存器的数量,可以减少函数栈的大小。ARMv8-A下使用了30个通用寄存器,ARMv7下只有15个通用寄存器

- ARMv8-A增加了TLB的大小,减少TLB MISS的概率

- ARMv8-A架构完全支持ARMv7架构下的应用程序

ARM A8架构

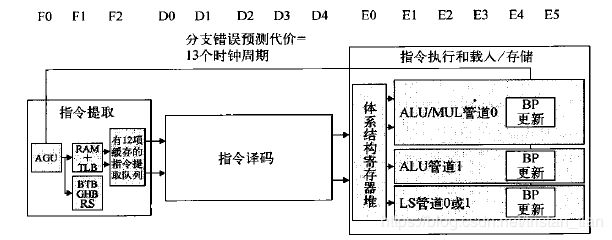

ARM A8是一种双发射、静态调度超标量处理器们具有动态发射检测功能。具有13级流水。

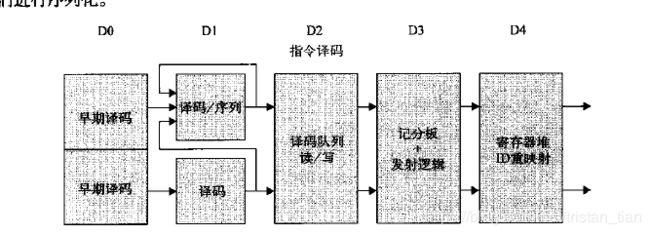

A8使用一种动态分支预测器,具有512项2路组相连分支目标缓冲区和一个4K项全局历史缓冲区。下图是指令译码流水线,利用循环发射机制,每个周期最多发射2条指令。

A8使用一种动态分支预测器,具有512项2路组相连分支目标缓冲区和一个4K项全局历史缓冲区。下图是指令译码流水线,利用循环发射机制,每个周期最多发射2条指令。

引用

ARMv8-A architecture overview

scu(snoop control unit)

关于ARM的内核架构