CMOS 工艺

CMOS工艺流程

CMOS有P阱与N阱两种,N阱的比P阱的CMOS性能好,下面介绍的首先就是制作N阱CMOS电路版图的8步工艺流程。因每一步要用到一块掩膜版进行光刻,所以也叫8版工艺流程。在实际生产中,每一步要牵涉光刻以外的一些工艺,但对设计者而言,任务仅仅是制作用于光刻制版的掩膜。

以上就是N阱CMOS工艺流程,共8步

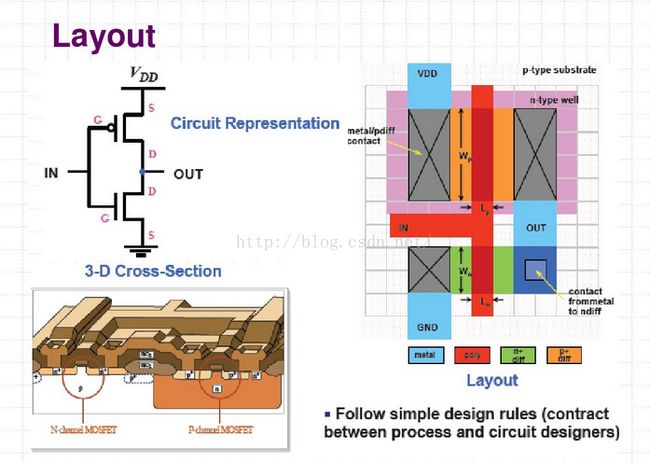

以下分别是N阱CMOS反相器的电路表示(circuit representation)图, (左上)、制作此反相器所设计的版图(Layout,右),以及工艺全部完成后所得产品的3D剖面示意图(3D cross section, 左下)

【对以上右边的Layout图的说明】

画着灰色方格的底图可代表p型衬底,在其上需要用各种掩膜依次作8次光刻:

1:紫色最大块:N阱(n-type well),用来光刻右上3D剖面图中最下面的一块区域;

2:橘色+绿色:p+和n+扩散(diff),用于制作两种晶体管的有源区(Wp、Wn为阱宽度),

3:红色横条连最长竖条:多晶硅(poly),连接到反相器输入端IN和两晶体管栅极(Lp、Ln为多晶硅长度),

4:蓝色:金属(metal),制作PMOS晶体管源栅漏(?),

5:蓝色:同上,制作NMOS晶体管源栅漏,连接到输出端OUT、漏VDD及地GND

6:灰色打x和画有口的为接触点(contact)分别使金属与p或n扩散相连

7:作金属掩膜,并刻出要外联的点到引线脚(pin)

8:钝化层掩膜,在其上刻测试孔,但无需引出。

以上只能了解一个大概,如想亲自动手设计,就应清楚画出每一步的掩膜形状,这时就要你讲清其”设计规则“才行,即各块掩膜的大小尺寸及相互间距!

以下介绍:

p肼CMOS工艺

【参考web资源】

1. http://wenku.baidu.com/link?url=0FysVwdSBqLgR18aNYCmL59oMERM2RxSBoChsGYmaOiGtefKXEyxz6KR_UbCKZY0lSjeeM9Vqdq7PfdcV60CQnk5IUPZxO3VHxyHMjw4Ibu

2.http://amuseum.cdstm.cn/AMuseum/ic/index_04_05_01_02.html

3.http://www.doc88.com/p-3002264366238.html