FPGA设计之首——Altera FPGA 选型及官网文档阅读

FPGA设计之首——选型及官网文档阅读

本文讲述FPGA设计开始的地方,即芯片选型及官网文档阅读。芯片选型当然是首要的,这个涉及到资源的分配及成本问题,如何选择合适的芯片做开发,在不同场合下使用时很有讲究的。官网文档阅读则贯穿整个开发阶段,像我这样对于FPGA不懂的小白,就需要花很多时间在阅读官网文档上,这些文档会帮助你一步步脱坑。

FPGA选型

网上有大量关于FPGA选型的帖子,每一篇都讲的头头是道,看完之后会感觉其内博大精深,也确实如此,需要考虑的方面太多。本人对选型没有很深的理解,所以这里贴上外链。

外部链接

FPGA 主流芯片选型指导和命名规则(一) ;

FPGA 主流芯片选型指导和命名规则(二) ;

FPGA基础知识4(FPGA设计经验和选型) ;

选型归纳

看完了别人的文章,当然要记住该记住的,这里做一下归纳:

- 首先最重要的是逻辑资源的考量,可以根据自己写过的某些程序占用的资源对将要写的程序占用逻辑资源进行估算;

- 其次是内存,但因为大多数设计都会外挂存储芯片,所以一般不建议直接使用芯片内部存储;

- 接下来是芯片支持的特殊功能,如PLL,DSP,乘法器位数及个数等;

- 如果需要使用差分,就需要考虑支持差分的接口Vcom及Vod是否能满足需求;

- 在批量设计之前,最好选用相对资源较多配置的芯片,后期导量可以再进行移植;

- 选用芯片一定是大陆常用的,如果是台湾的或国外的,就需要考虑打件厂商的能力及采购时程问题;

罗列了这么多,最终选型的每一步,都应该有报告产生,在报告(PPT)中需要对每一个抉择进行阐述都要有充分的理由,反复进行确认,而且需要及时的与同事沟通,以免考虑不周到。

官网文档

虽然说不出是哪里好,可是官网的文档还是忘不了。

官网给出了一本FPGA入门级的书籍PDF版本的,书名叫:FPGA for DUMMIES,但是需要注册,文档才会被发到指定邮箱,这里贴出来CSDN下载的链接,如果没有积分留言即可,对于初学者非常友好。

官网入口

我选用的是Altera FPGA 也就是现在的Inter FPGA,所以官网在这Intel FPGAs and Programmable Devices.

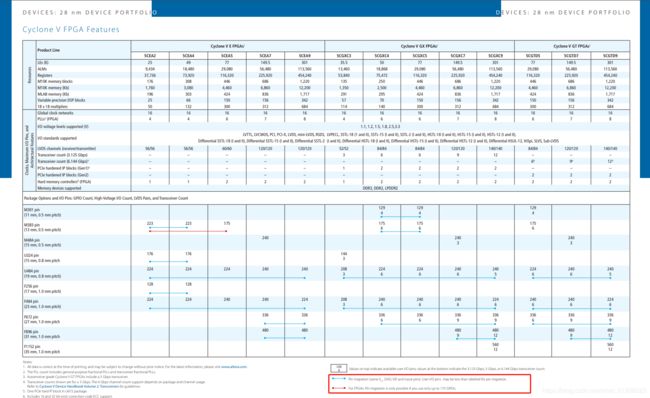

这里还有Inter Cyclone FPGA的主界面 ,在这里可以选择需要的 Cyclone 的类型,包括每一代的使用时间以及目前是否依然支持;点进去还能看到每一代 FAMILY VARIANTS 的概况;可以通过点击芯片的 View overview table 看到每一个成员的概况叙述,如Cyclone V FPGA E ,这个文档是 pdf 档,通过这一个文档,就能为我们选型提供极大的方便。

最重要的,可以看出来,哪些 Device 型号实可以 Pin to Pin 兼容的,这就允许我们在一开始做设计的时候使用相对资源较大的器件,然后实际使用的时候转为资源相对少的,详情见上图。

文档入口

基本上所有期间的文档都会在这里 ,还是那句话,根本性的了解,必须要阅读完每一个有价值的文档,但是不看也不知道哪些有价值,所以就得一个个看;但是可以分主次,感觉需要的就可以看的慢一点,多了解一些信息,;感觉没多大相关性的, 就可以少花点时间看。

依然从上图看出,有红框标记的就是在硬件设计阶段的重点,这里做一下简单的介绍:

Devices

可以选择相应的器件型号如cyclone V,就会出来对应的 support ,这里面的文档跟后面的介绍可能有交叉,但都是同样重要的,比如:

| Cyclone V I/O Timing Spreadsheet | Cyclone V Device Family Pin Connection Guidelines (PDF) |

|---|---|

| Cyclone V Device Design Guidelines (PDF) | Cyclone V differential pad placement rule and pad mapping files |

| Cyclone V Errata (PDF) | Device Pin-Outs |

| Known Cyclone V Issues | BSDL Files |

| All Packaging Specifications and Dimensions | Board Design Guidelines |

以上每一个都是超链接,可以连接到对应的PDF,如果觉得对表面理解不清楚,可以链接过去看一下里面是什么内容,可以说这些内容就是对该设备进行了设计之初的全方位描述。

Pin-Outs

可以查找出对应器件的输出Pin的相关情况,包含三种格式,pdf, txt, xls ,以下引用官网的详细介绍:

Documentation: Pin-Out Files for Intel FPGA Devices

The following tables contain downloadable files listing Intel FPGA device pin-out descriptions. There are up to three types of files for each device: Portable Document Format Files (.pdf), Text Files (.txt), and Microsoft Excel Files (.xls).

You can view PDF files in Adobe Acrobat. The text files are tab delimited, and are most easily viewed using a spreadsheet program, such as Microsoft Excel. Use the following steps to open the text files in Microsoft Excel on a Windows operating system.

- Open the Microsoft Excel program.

- Choose Open (File menu).

- Locate the text file and choose the Open button.

- In the first page of the Text Import Wizard, choose the Delimited radio button in the Original data type box. Click the Next button.

- In the second page of the Text Import Wizard, check Tab in the Delimiters box. Click the Next button.

- In the third page of the Text Import Wizard, choose the Generalradio button in the Column data format box. Click the Finish button.

You can open both the PDF and text files on Unix, Windows, and Macintosh operating systems.

User Guides

不用多说,这里的文档都是重中之重。这里最有用的就是各个IP的使用手册,如 PLL,FIFO, Embedded Memory,LVDS I/O Buffer ,DDIO Buffer 等;

但是也是比较坑的是,这里的搜索功能感觉像是个智障一样,大多数情况下是搜索不到相关信息了。需要自己反复的搜索关键词,一点点的筛选,才能找到想要的结果,比如搜索Display:

Data Sheets

形式与上面类似,这里存放的是器件的数据表,内部包含了器件属性的相关信息,比如I/O支持多少速率, 该设备PLL的使用详情等;这个也是必须要了解,且需要反复看的内容。

比较有用的,器件支持差分I/O电平规格,对应外围电路的设计实例,JTAG外围电路,EPCQ外围电路都会有详细介绍。

Pin Connection Guidelines

这个Guidelines 可有用了,找到对应的器件,这里表格会列出来所有Pin的连接及使用建议。

如果是初学者,可以从每一个Pin出发,了解每一个Pin的功能,能够有效的在最短的时间内学习到FPGA的硬件设计,外围电路该怎么搭起来。这个绝对是外围电路设计的基础,依照这个Guidelines,再加上具体的使用方式,能够Cover住百分之八九十的FPGA外围硬件设计。

Package and Thermal Resistance

这里主要会给出封装,Schematic的库,而且还是分离式的,印象中是支持好几种格式的,可以确定的是支持 .olb ,而且这里会提供相应的footprint 的 datasheet ,此外还有 EPCS 的相关信息,以下为引用:

Package and Thermal Resistance

Package information includes the ordering code reference, package acronym, leadframe material, lead finish (plating), JEDEC® outline reference, lead coplanarity, weight, moisture sensitivity level, and other special information. The thermal resistance information includes device pin count, package name, and resistance values.

原理图封装在这

纠正一下,刚才说的有问题,以上均为Layout 封装,原理图封装的地址在这,现在已经找到了,链接可直达,格式为 Cadence Capture CIS 。这里还可以放一下原理图检查工作表的地址 ,这个可以帮助我们检查设计好的原理图,但是感觉有点高大上:

Device Schematic Review Worksheets

Intel® FPGA provides schematic review worksheets intended to help you review your schematic and adhere to Intel’s guidelines. These worksheets are based on the respective device Pin Connection Guidelines and other referenced Intel FPGA documentation applicable to board-level pin connections that need to be considered when you finalize your schematic. Table 1 lists the available schematic review worksheets that you can download in Microsoft* Office Word document format.

以上为官网文档的阅读指导,全面的阅读官方文档,可以避免很多设计失误,前期准备及原理图,Layout设计阶段都必须严格按照官方指定的规则来。

After

罗里吧嗦的,可能有点逻辑混乱,如果有关键的地方遗漏,我回头想起来的时候再来补充吧。

Drafter : LJacki

Date : 2019-04-10