- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (121)DAC接口--->(006)基于FPGA实现DAC8811接口

FPGA系统设计指南针

FPGA接口开发(项目实战)fpga开发FPGAIC

1目录(a)FPGA简介(b)IC简介(c)Verilog简介(d)基于FPGA实现DAC8811接口(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电

- FPGA复位专题---(3)上电复位?

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发

(3)上电复位?1目录(a)FPGA简介(b)Verilog简介(c)复位简介(d)上电复位?(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 使用FPGA接收MIPI CSI RX信号并进行去抖动、RGB转YUV处理:FX3014 USB3.0 UVC传输与帧率控制源代码,FPGA实现MIPI CSI RX接收,去Debayer, RGB转

kVfINoSzdrt

fpga开发程序人生

fpgamipicsirx接收去debayer,rgb转yuv,fx3014usb3.0uvc传输与帧率控制源代码,具体架构看图,除dphy物理层外,mipi均为源码sensorimx219mipi源码mipi4lanecsirxraw10fpgamachXO3lf-690usb3.0fx301432bityuvdatawithframesync测试模式3280*246415fps1920*108

- FPGA_mipi

哈呀_fpga

fpga开发逻辑高速接口系统架构高速传输

1mipi接口mipi(移动行业处理器接口,是为高速数据传输量身定做的,旨在解决日益增长的高清图像(视频)传输的高带宽要求与传统接口低速率之间的矛盾。采用差分信号传输,在设计时需要按照差分设计的一般规则进行严格的设计。mipi协议提出之际,主要有2个应用,csi(摄像头串行接口),旨在为高清摄像头和应用处理器之间提供一个高速串行接口,和dsi(显示串行接口),旨在为应用处理器和显示设备之间提供一个

- Xilinx 7系列FPGA架构之器件配置(二)

FPGA技术实战

FPGA器件架构XinxFPGA硬件设计fpga开发

引言:本文我们介绍下7系列FPGA的配置接口,在进行硬件电路图设计时,这也是我们非常关心的内容,本文主要介绍配置模式的选择、配置管脚定义以及如何选择CFGBVS管脚电压及Bank14/15电压。1.概述Xilinx®7系列设备有五个配置接口。每个配置接口对应一个或多个配置模式和总线宽度,如表1所示。有关接口详细的时序信息,可以参阅相应的7系列FPGA数据手册。配置时序主要与FPGA配置时钟管脚CC

- Xilinx 7系列FPGA架构之器件配置(一)

FPGA技术实战

FPGA器件架构XinxFPGA硬件设计fpga开发

引言:本系列博文描述7系列FPGA配置的技术参考。作为开篇,简要概述了7系列FPGA的配置方法和功能。随后的博文将对每种配置方法和功能进行更详细的描述。本文描述的配置方法和功能适用于所有7系列家族器件,只有少数例外。1.概述Xilinx®7系列FPGA通过将特定于应用程序的配置数据(位流)加载到内存中进行配置。7系列FPGA可以主动从外部非易失性存储设备加载,也可以通过外部智能源(如微处理器、DS

- FPGA器件在线配置方法概述

fpga和matlab

FPGA其他fpga开发FPGA在线配置

目录1.配置电路结构和原理2.ICR控制电路软件3.几种常见的FPGA在线配置方法3.1动态部分重配置(PartialReconfiguration,PR)3.2在系统编程(In-SystemProgramming,ISP)3.3多比特流配置(Multi-BitstreamConfiguration)3.4远程更新与配置3.5使用OpenCL或HLS工具FPGA(Field-Programmabl

- quartus频率计 时钟设置_FPGA021 基于QuartusⅡ数字频率计的设计与仿真

weixin_39876739

quartus频率计时钟设置

摘要随着科技电子领域的发展,可编程逻辑器件,例如CPLD和FPGA的在设计中得到了广泛的应用和普及,FPGA/CPLD的发展使数字设计更加的灵活。这些芯片可以通过软件编程的方式对内部结构进行重构,使它达到相应的功能。这种设计思想改变了传统的数字系统设计理念,促进了EDA技术的迅速发展。数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,

- quartus pin 分配(三)

落雨无风

IC设计fpgafpga开发

quartuspin分配如有需要,可查看quartusUI界面sdc配置(二)上次文章中,说了自己写sdc需要配置的分类点,这次将介绍管脚分配。已打开Quartus软件,导入设计,写好约束下一步,在Quartus软件的菜单栏打开Assignments中的二级菜单PinPlanner打开改界面即可看到选中的fpga型号,管脚图,封装类型等信息。在打开的界面中,大致可分为上下两个部分。上半部分,可分为

- FPGA随记——赛灵思OOC功能

一口一口吃成大V

FPGA随记fpga开发

在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下的全局(Global)综合方式,将顶层之下的所有逻辑模块都进行综合,但是设置为OOC方式的模块除外,它们独立于顶层设计而单独综合。通常,在整个设计周期中,顶层设计会被多次修改并综合。但有些子模块在创建完毕之后不会因为顶层设计的修改而被修改,如IP,它们被设置为OOC综合方式

- 如何设计实现完成一个FPGA项目

芯作者

D1:verilog设计D1:VHDL设计fpga开发

设计并完成一个FPGA项目是一个复杂但非常有价值的工程任务。以下是一个详细的步骤指南,帮助你从零开始完成一个FPGA项目。1.项目定义与需求分析确定项目目标:明确项目要实现的功能和性能指标。需求分析:列出所有功能需求、性能需求、接口需求等。可行性分析:评估技术可行性、成本和时间预算。2.硬件选择FPGA芯片选择:根据项目需求选择合适的FPGA芯片(如Xilinx、Intel/Altera、Latt

- 零配置初始化流程就一直过不去_ZYNQ UltraScale+ MPSoc FPGA自学笔记-启动加载配置...

weixin_40009026

零配置初始化流程就一直过不去

前言听说最近秋天的第一杯奶茶挺火的,我得赶紧奋发图强写点东西,好赚点赏钱给妹子买奶茶,各位大佬出手大方点,我怕秋天过去了妹子还没喝上奶茶!言归正传,ZYNQUltraScale+MPSoc的配置过程还是挺复杂的,决定写一篇文章来讲一讲,当然我也是初学,如有错讹请轻轻打左脸。一、配置过程Zynq®UltraScale+™MPSoC同时有PS端和PL端,PS又有两种不同的多核处理器可以运行底层代码或者

- FPGA编程指南: CSU DMA传输

行者..................

fpga开发FPGA

1.将安全流开关配置设置为从DMA源接收,即设置csu.csu_sss_cfg[pcap_sss]为0x5。2.配置并设置CSU_DMA以建立通道和传输,具体编程方法可参考CSUDMA编程部分。-通道类型为DMA_SRC。-设置源地址为位流的地址。-设置大小为以字表示的位流大小。3.等待CSUDMA操作完成,确保源频道的传输已完成。4.清除CSU_DMA中断并确认传输完成,这需要设置csudma.

- FPGA案例小程序

BABA8891

fpga开发小程序

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)的应用广泛,因此存在许多不同领域的案例小程序。以下是一些FPGA案例小程序的示例,涵盖了不同的应用场景:1.串口闭环收发小程序应用场景:工业自动化、通信设备、仪器仪表等。功能描述:该小程序通过FPGA芯片的编程实现串口数据的接收和发送功能,支持9600和115200两种速率。在接收数据时,FPGA通过串行接口接收外

- 电源管理芯片4644关键指标及测试方法

国科安芯

产品fpga开发嵌入式硬件硬件工程

以国科安芯(ANSILIC)推出四通道输出降压微型模块稳压器ASP4644为例,该器件支持多路级联输出最高16A。工程师可以快速设计出满足FPGA、ASIC和微处理器等多种电压和负载电流要求驱动,ASP4644模块稳压器包括DC/DC控制器、电源开关、电感器和补偿组件,采用BGA封装。仅需8个外部陶瓷电容器和4个反馈电阻器就能调节4个可独立地调整并介于0.6V至5.5V的输出。单独的输入引脚使4个

- FPGA(Field-Programmable Gate Array,现场可编程门阵列)开发入门

MAMA6681

fpga开发

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)开发入门是一个系统且深入的过程,涉及到硬件设计、编程语言、开发工具等多个方面。以下是一个简要的FPGA开发入门指南:一、基础知识准备数字电路与逻辑设计:了解数字电路的基本概念,如二进制、逻辑门电路、组合逻辑电路、时序逻辑电路等。熟悉布尔代数和逻辑门的功能及其实现方法。计算机体系架构:掌握CPU、内存、外设、总线等计

- FPGA 编程基础, 赋值操作符, 运算符使用, 条件表达式, 信号操作方法

行者..................

fpga开发

1.**赋值符号**:-**"="**:阻塞赋值,即在`always`模块中该语句会被立即执行。-**""**:大于,如果A>B则结果为TRUE,否则为FALSE。-**">="**:大于等于,如果A>=B则结果为TRUE,否则为FALSE。-**"=="**:等于,如果A==B则结果为TRUE,否则为FALSE。-**"!="**:不等于,如果A!=B则结果为TRUE,否则为FALSE。4.**

- zobovision随谈H.265/HEVC编码FPGA实现(一)

zobovision

视频图像编解码FPGAIPfpga开发视频编解码

zobovision随谈H.265/HEVC编码FPGA实现(一)H.265/HEVC出来已有10年,但市场应用难言巅峰,正如古董级的H.264现在仍然大行其道,H.265的全面应用仍有待市场发酵,至少在硬件产品端应用,值得期待。一来H.265相对H.264而言,压缩技术确实要先进不少,不管是理论上还是实际效果方面;二是H.265相对后来者H.266/VVC等而言,实用性更强,性价比更高,产品端的

- (14)时钟专题--->(014)行波时钟

宁静致远dream

FPGA学无止境fpga开发FPGAIC

1.1.1本节目录1)本节目录2)本节引言3)FPGA简介4)行波时钟5)结束语1.1.2本节引言“不积跬步,无以至千里;不积小流,无以成江海。就是说:不积累一步半步的行程,就没有办法达到千里之远;不积累细小的流水,就没有办法汇成江河大海。1.1.3FPGA简介FPGA(FieldProgrammableGateArray)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电

- 【教程】如何使用 MYScrcpy,一行Python代码获取Android设备 屏幕/摄像头 H264/H265 原始视频流

Me2sY

MYScrcpypythonandroid开发语言智能手机扩展屏应用开发开源测试工具

MYScrcpy1.5.8Github/Gitee1.5.8版本新增获取原始视频流(H264/H265)方法,供小伙伴们在需要原生H264/H265串流时使用要求MYScrcpy>1.5.8pipinstall-Umysc安卓设备开启调试模式,安卓版本>5(摄像头需>11)H265需安卓设备支持H265编码步骤MYScrcpy从设计之初,就是想为小伙伴们打造一款好用易上手的工具包,所以使用起来也非

- 在Xilinx FPGA上快速实现 JESD204B

长弓的坚持

总线接口协议存储

简介JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的B修订版支持高达12.5Gbps串行数据速率,并可确保JESD204链路具有可重复的确定性延迟。随着转换器的速度和分辨率不断提升,JESD204B接口在ADI高速转换器和集成RF收发器中也变得更为常见。此外,FPGA和ASIC中灵活的串行器/解串器(SERDES)设计正逐步取代连接转换器的传统并行LVDS/C

- 【【通信协议之MDIO读写的FPGA实现】】

ZxsLoves

FPGA学习fpga开发

通信协议之MDIO读写的FPGA实现介绍MAC与PHY之间的通信通过了MDIO的接口与PHY芯片的通信则通过MAC(MediaAccessControl)控制器来实现。MAC控制器与PHY芯片之间的通信通常包括两部分:1.数据传输接口:比如MII(MediaIndependentInterface)、RMII(ReducedMediaIndependentInterface)、GMII(Gigab

- 8B10B编解码及FPGA实现

weixin_34309435

概述在使用ALTERA的高速串行接口时,GXB模块里硬件实现了8B10B编码,用户只是“傻瓜”式的使用,笔者也一直没有弄清楚。网上搜索了一些学习资料,结合参考文献希望能够对其进行消化。另外,ALTERA现在已经提供8B10BIP,用户可以直接使用,不过有时候为了代码可移植性需要自己写代码实现8B10B编解码,笔者希望在这方面也做些实践。8B10B编码概念基本概念网上可以轻易找到答案,简单的说就是将

- java工厂模式

3213213333332132

java抽象工厂

工厂模式有

1、工厂方法

2、抽象工厂方法。

下面我的实现是抽象工厂方法,

给所有具体的产品类定一个通用的接口。

package 工厂模式;

/**

* 航天飞行接口

*

* @Description

* @author FuJianyong

* 2015-7-14下午02:42:05

*/

public interface SpaceF

- nginx频率限制+python测试

ronin47

nginx 频率 python

部分内容参考:http://www.abc3210.com/2013/web_04/82.shtml

首先说一下遇到这个问题是因为网站被攻击,阿里云报警,想到要限制一下访问频率,而不是限制ip(限制ip的方案稍后给出)。nginx连接资源被吃空返回状态码是502,添加本方案限制后返回599,与正常状态码区别开。步骤如下:

- java线程和线程池的使用

dyy_gusi

ThreadPoolthreadRunnabletimer

java线程和线程池

一、创建多线程的方式

java多线程很常见,如何使用多线程,如何创建线程,java中有两种方式,第一种是让自己的类实现Runnable接口,第二种是让自己的类继承Thread类。其实Thread类自己也是实现了Runnable接口。具体使用实例如下:

1、通过实现Runnable接口方式 1 2

- Linux

171815164

linux

ubuntu kernel

http://kernel.ubuntu.com/~kernel-ppa/mainline/v4.1.2-unstable/

安卓sdk代理

mirrors.neusoft.edu.cn 80

输入法和jdk

sudo apt-get install fcitx

su

- Tomcat JDBC Connection Pool

g21121

Connection

Tomcat7 抛弃了以往的DBCP 采用了新的Tomcat Jdbc Pool 作为数据库连接组件,事实上DBCP已经被Hibernate 所抛弃,因为他存在很多问题,诸如:更新缓慢,bug较多,编译问题,代码复杂等等。

Tomcat Jdbc P

- 敲代码的一点想法

永夜-极光

java随笔感想

入门学习java编程已经半年了,一路敲代码下来,现在也才1w+行代码量,也就菜鸟水准吧,但是在整个学习过程中,我一直在想,为什么很多培训老师,网上的文章都是要我们背一些代码?比如学习Arraylist的时候,教师就让我们先参考源代码写一遍,然

- jvm指令集

程序员是怎么炼成的

jvm 指令集

转自:http://blog.csdn.net/hudashi/article/details/7062675#comments

将值推送至栈顶时 const ldc push load指令

const系列

该系列命令主要负责把简单的数值类型送到栈顶。(从常量池或者局部变量push到栈顶时均使用)

0x02 &nbs

- Oracle字符集的查看查询和Oracle字符集的设置修改

aijuans

oracle

本文主要讨论以下几个部分:如何查看查询oracle字符集、 修改设置字符集以及常见的oracle utf8字符集和oracle exp 字符集问题。

一、什么是Oracle字符集

Oracle字符集是一个字节数据的解释的符号集合,有大小之分,有相互的包容关系。ORACLE 支持国家语言的体系结构允许你使用本地化语言来存储,处理,检索数据。它使数据库工具,错误消息,排序次序,日期,时间,货

- png在Ie6下透明度处理方法

antonyup_2006

css浏览器FirebugIE

由于之前到深圳现场支撑上线,当时为了解决个控件下载,我机器上的IE8老报个错,不得以把ie8卸载掉,换个Ie6,问题解决了,今天出差回来,用ie6登入另一个正在开发的系统,遇到了Png图片的问题,当然升级到ie8(ie8自带的开发人员工具调试前端页面JS之类的还是比较方便的,和FireBug一样,呵呵),这个问题就解决了,但稍微做了下这个问题的处理。

我们知道PNG是图像文件存储格式,查询资

- 表查询常用命令高级查询方法(二)

百合不是茶

oracle分页查询分组查询联合查询

----------------------------------------------------分组查询 group by having --平均工资和最高工资 select avg(sal)平均工资,max(sal) from emp ; --每个部门的平均工资和最高工资

- uploadify3.1版本参数使用详解

bijian1013

JavaScriptuploadify3.1

使用:

绑定的界面元素<input id='gallery'type='file'/>$("#gallery").uploadify({设置参数,参数如下});

设置的属性:

id: jQuery(this).attr('id'),//绑定的input的ID

langFile: 'http://ww

- 精通Oracle10编程SQL(17)使用ORACLE系统包

bijian1013

oracle数据库plsql

/*

*使用ORACLE系统包

*/

--1.DBMS_OUTPUT

--ENABLE:用于激活过程PUT,PUT_LINE,NEW_LINE,GET_LINE和GET_LINES的调用

--语法:DBMS_OUTPUT.enable(buffer_size in integer default 20000);

--DISABLE:用于禁止对过程PUT,PUT_LINE,NEW

- 【JVM一】JVM垃圾回收日志

bit1129

垃圾回收

将JVM垃圾回收的日志记录下来,对于分析垃圾回收的运行状态,进而调整内存分配(年轻代,老年代,永久代的内存分配)等是很有意义的。JVM与垃圾回收日志相关的参数包括:

-XX:+PrintGC

-XX:+PrintGCDetails

-XX:+PrintGCTimeStamps

-XX:+PrintGCDateStamps

-Xloggc

-XX:+PrintGC

通

- Toast使用

白糖_

toast

Android中的Toast是一种简易的消息提示框,toast提示框不能被用户点击,toast会根据用户设置的显示时间后自动消失。

创建Toast

两个方法创建Toast

makeText(Context context, int resId, int duration)

参数:context是toast显示在

- angular.identity

boyitech

AngularJSAngularJS API

angular.identiy 描述: 返回它第一参数的函数. 此函数多用于函数是编程. 使用方法: angular.identity(value); 参数详解: Param Type Details value

*

to be returned. 返回值: 传入的value 实例代码:

<!DOCTYPE HTML>

- java-两整数相除,求循环节

bylijinnan

java

import java.util.ArrayList;

import java.util.List;

public class CircleDigitsInDivision {

/**

* 题目:求循环节,若整除则返回NULL,否则返回char*指向循环节。先写思路。函数原型:char*get_circle_digits(unsigned k,unsigned j)

- Java 日期 周 年

Chen.H

javaC++cC#

/**

* java日期操作(月末、周末等的日期操作)

*

* @author

*

*/

public class DateUtil {

/** */

/**

* 取得某天相加(减)後的那一天

*

* @param date

* @param num

*

- [高考与专业]欢迎广大高中毕业生加入自动控制与计算机应用专业

comsci

计算机

不知道现在的高校还设置这个宽口径专业没有,自动控制与计算机应用专业,我就是这个专业毕业的,这个专业的课程非常多,既要学习自动控制方面的课程,也要学习计算机专业的课程,对数学也要求比较高.....如果有这个专业,欢迎大家报考...毕业出来之后,就业的途径非常广.....

以后

- 分层查询(Hierarchical Queries)

daizj

oracle递归查询层次查询

Hierarchical Queries

If a table contains hierarchical data, then you can select rows in a hierarchical order using the hierarchical query clause:

hierarchical_query_clause::=

start with condi

- 数据迁移

daysinsun

数据迁移

最近公司在重构一个医疗系统,原来的系统是两个.Net系统,现需要重构到java中。数据库分别为SQL Server和Mysql,现需要将数据库统一为Hana数据库,发现了几个问题,但最后通过努力都解决了。

1、原本通过Hana的数据迁移工具把数据是可以迁移过去的,在MySQl里面的字段为TEXT类型的到Hana里面就存储不了了,最后不得不更改为clob。

2、在数据插入的时候有些字段特别长

- C语言学习二进制的表示示例

dcj3sjt126com

cbasic

进制的表示示例

# include <stdio.h>

int main(void)

{

int i = 0x32C;

printf("i = %d\n", i);

/*

printf的用法

%d表示以十进制输出

%x或%X表示以十六进制的输出

%o表示以八进制输出

*/

return 0;

}

- NsTimer 和 UITableViewCell 之间的控制

dcj3sjt126com

ios

情况是这样的:

一个UITableView, 每个Cell的内容是我自定义的 viewA viewA上面有很多的动画, 我需要添加NSTimer来做动画, 由于TableView的复用机制, 我添加的动画会不断开启, 没有停止, 动画会执行越来越多.

解决办法:

在配置cell的时候开始动画, 然后在cell结束显示的时候停止动画

查找cell结束显示的代理

- MySql中case when then 的使用

fanxiaolong

casewhenthenend

select "主键", "项目编号", "项目名称","项目创建时间", "项目状态","部门名称","创建人"

union

(select

pp.id as "主键",

pp.project_number as &

- Ehcache(01)——简介、基本操作

234390216

cacheehcache简介CacheManagercrud

Ehcache简介

目录

1 CacheManager

1.1 构造方法构建

1.2 静态方法构建

2 Cache

2.1&

- 最容易懂的javascript闭包学习入门

jackyrong

JavaScript

http://www.ruanyifeng.com/blog/2009/08/learning_javascript_closures.html

闭包(closure)是Javascript语言的一个难点,也是它的特色,很多高级应用都要依靠闭包实现。

下面就是我的学习笔记,对于Javascript初学者应该是很有用的。

一、变量的作用域

要理解闭包,首先必须理解Javascript特殊

- 提升网站转化率的四步优化方案

php教程分享

数据结构PHP数据挖掘Google活动

网站开发完成后,我们在进行网站优化最关键的问题就是如何提高整体的转化率,这也是营销策略里最最重要的方面之一,并且也是网站综合运营实例的结果。文中分享了四大优化策略:调查、研究、优化、评估,这四大策略可以很好地帮助用户设计出高效的优化方案。

PHP开发的网站优化一个网站最关键和棘手的是,如何提高整体的转化率,这是任何营销策略里最重要的方面之一,而提升网站转化率是网站综合运营实力的结果。今天,我就分

- web开发里什么是HTML5的WebSocket?

naruto1990

Webhtml5浏览器socket

当前火起来的HTML5语言里面,很多学者们都还没有完全了解这语言的效果情况,我最喜欢的Web开发技术就是正迅速变得流行的 WebSocket API。WebSocket 提供了一个受欢迎的技术,以替代我们过去几年一直在用的Ajax技术。这个新的API提供了一个方法,从客户端使用简单的语法有效地推动消息到服务器。让我们看一看6个HTML5教程介绍里 的 WebSocket API:它可用于客户端、服

- Socket初步编程——简单实现群聊

Everyday都不同

socket网络编程初步认识

初次接触到socket网络编程,也参考了网络上众前辈的文章。尝试自己也写了一下,记录下过程吧:

服务端:(接收客户端消息并把它们打印出来)

public class SocketServer {

private List<Socket> socketList = new ArrayList<Socket>();

public s

- 面试:Hashtable与HashMap的区别(结合线程)

toknowme

昨天去了某钱公司面试,面试过程中被问道

Hashtable与HashMap的区别?当时就是回答了一点,Hashtable是线程安全的,HashMap是线程不安全的,说白了,就是Hashtable是的同步的,HashMap不是同步的,需要额外的处理一下。

今天就动手写了一个例子,直接看代码吧

package com.learn.lesson001;

import java

- MVC设计模式的总结

xp9802

设计模式mvc框架IOC

随着Web应用的商业逻辑包含逐渐复杂的公式分析计算、决策支持等,使客户机越

来越不堪重负,因此将系统的商业分离出来。单独形成一部分,这样三层结构产生了。

其中‘层’是逻辑上的划分。

三层体系结构是将整个系统划分为如图2.1所示的结构[3]

(1)表现层(Presentation layer):包含表示代码、用户交互GUI、数据验证。

该层用于向客户端用户提供GUI交互,它允许用户

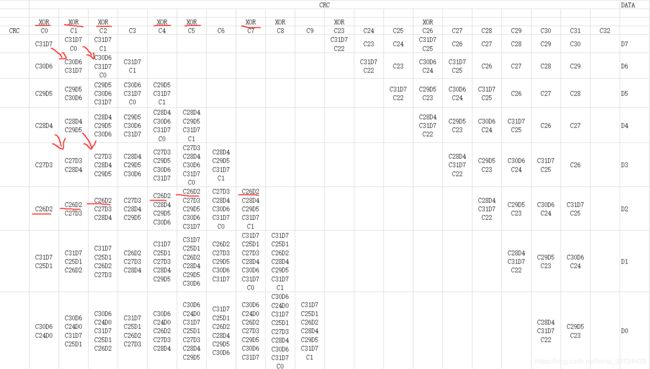

4、数据由高位依次输入,当输入最后1bit数据时,CRC寄存器中即为校验值,同时如果将D0时刻的表达式表示出来,则为并行CRC的计算公式。

4、数据由高位依次输入,当输入最后1bit数据时,CRC寄存器中即为校验值,同时如果将D0时刻的表达式表示出来,则为并行CRC的计算公式。