Serdes 原理及调试学习

Serdes原理与设计实践之一:Serdes简介

1. Serdes简介

为了提高接口传输带宽,设计中经常采用并行总线设计。并行总线通过提高时钟速率和数据位宽来提高传输带宽。限制接口传输带宽主要有2个方面:

a. 时钟速率。它决定了发送和接收端的采样速率。

随着时钟速率的提高,由于传输通路的非理想性,会带来严重的信号完整性问题,导致接收端无法正确解析接收到的信号。较高的时钟速率对应的采样窗口缩小,对芯片设计也提出了较高要求。

b. 数据位宽。它决定了每次传输的数据量。

提高数据位宽,需要占用较多的芯片IO。同时,不同IO之间的Skew也会导致采样困难。

因此,在实际设计中,不可能无限制的提高时钟频率和数据位宽。SerDes技术在一定程度上帮助解决了这一问题。

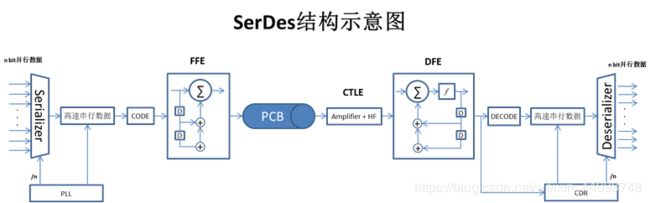

Serializer:串行器。将n bit并行数据串化为1 lane的高速串行数据。

CODE:编码器。对高速串行数据进行编码,例如:8b/10b,128b/130b等。主要有两个方面的作用:一是平衡传输中0和1的个数,防止共模点偏离零点;二是保证信号线有一定的翻转,使CDR能够从数据流中获得时钟;三是保证数据复杂度,使接收端可以对CTLE、DFE等模块正确进行training。接收端接收数据后CTLE和DFE要做training,以获得对恢复数据最有效的参数。如果数据码型过于简单,则接收端training后得到的参数无法适应复杂码型的恢复。

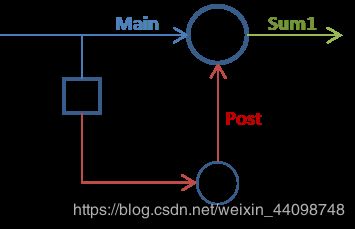

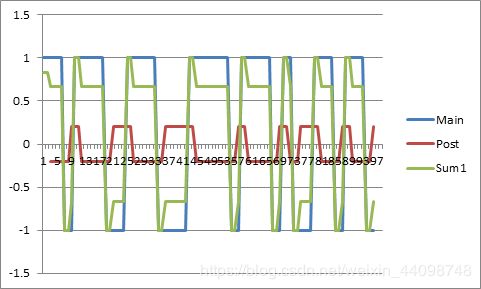

FFE:Feed Forward Equalization前馈均衡器,即预加重均衡器。非理想信道的传输对高频分量有较大的衰减。为了补偿传输过程中的衰减,在将信号发送到传输信道上之前,对编码后的传输数据进行高频分量补偿,这就是预加重均衡。FFE由延迟电路(D)、乘法器和加法器组成,延迟电路的时间延迟正好是1 bit时间。以一阶延迟电路为例:输出bit电压=n bit电压+c1*(n-1) bit电压+c2*(n-2) bit电压+…。其中,c1/c2为乘法器系数,n-1代表前1 bit,下同。下图为一阶抽头电路的图例,其中c1=-0.2:

PCB:物理传输通道。由于是非理想通道,信号在传输过程中会衰减,高频分量的衰减大于低频分量的衰减。

CTLE:Continuous-time Linear Equalization连续时间线性均衡器。它是一个模拟均衡器,作用等效于放大器+高通滤波器。接收到信道上传输的信号后,先将整个信号等比放大,然后通过高通滤波器,低频分量衰减的多,高频分量只有少量衰减。目的也是加大高频分量与低频分量的能量比。

DFE:Decision Feedback Equalizer判决反馈均衡器。它是一个数字均衡器,由FIR滤波器、加法器和用于符号判决的判决器组成。FIR滤波器由n阶乘法器和延迟电路组成,延迟电路将输入延迟1 bit时间。判决器将模拟信号数字化。以三阶延迟电路为例:n bit输出=n bit值+c1*(n-1) bit值+c2*(n-2) bit值+c3*(n-3) bit值。其结果也是增强高频分量,加大了高频分量与低频分量的能量比。在实际应用中,DFE会根据接收到的数字眼图,经过training,对乘法器系数进行调整,以达到最优结果。正是因为DFE的training功能,发送端更需要对传输的数据进行编码,使DFE能够获得更多的码型进行处理。

Decode:解码器。对高速串行数据进行解码,恢复出来源码。

De-serializer:解串器。将高速串行数据恢复成n bit并行数据。

在整个数据通路中,信号通过PCB会造成较大的高频衰减,FFE、CTLE、DFE则通过各种方式解决高频衰减的问题。

Serdes的基本原理就介绍到这里,后续将继续介绍Serdes的设计和调试。

————————————————

版权声明:本文为CSDN博主「轻漂漂」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_44098748/article/details/85002027

Serdes原理与设计实践之二:Serdes设计流程

2. Serdes设计流程

确定系统的传输能力(仿真、测试)

有的芯片厂商在芯片spec中已经提供了设计指导,一般是链路衰减限制或在某种板材、层叠下PCB上走线最长限制。如果没有设计指导,就需要设计者进行前仿真,以确定传输能力极限。可按照下面几个步骤实现:

1)获取TX、RX的仿真模型。

2)搭建仿真链路。

3)进行仿真,看仿真结果是否满足接收端要求。通常是观察接收端信号是否满足眼图要求。

4)根据仿真结果,调整传输通道的参数,使其达到接收端极限值。此时得到的传输通道参数即为系统传输能力极限。

如果应用环境接近仿真的极限结果,还需要通过测试进行实际验证。因为实际应用环境比仿真环境要复杂的多。

实际应用测试可按照下面几步去实现:

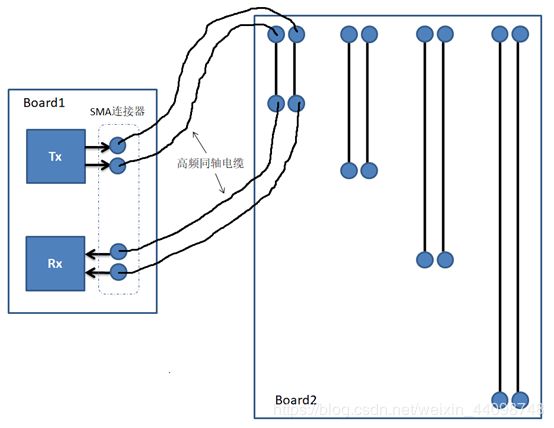

1)收发芯片不直接相连,两端都预留出连接器。

2)设计带有不同长度传输线的PCB,两端预留与带有收发芯片的板子对接的连接器。根据仿真和实际应用确定传输线长度。例如,传输线有5inch、10inch、20inch、30inch等等。

3)通过高频电缆将2)中的传输线与收发芯片板相连,测试出在哪种长度下,接收端误码不再满足要求。

最后,对比仿真和实测结果是否吻合。

在确定了系统的传输能力的情况下,我们就可以在设计中去具体实现了。

根据系统的传输能力及项目其它需求,确定传输通道设计方案。初步设计完成后,需进行后仿真,验证接收端是否满足要求,同时也要留有足够的裕量。

具体PCB设计时,主要考虑两方面:

1)降低传输通道损耗

使用低损耗板材。

走线长度应尽量短。

差分对要等长,过孔位置要一致,减少P/N之间的skew。

走线不要太细。特定情况下可以通过隔层参考增加线宽。

减少换层,保证通路上最多只有两端有换层孔。

过孔设计。如果采用通孔设计,最好是使用背钻。过孔旁边要有伴地孔。

如果收发之间有连接器,尽量选用低损耗、有阻抗控制的连接器。

2)控制收发之间的串扰及周围信号对收发信号的串扰。

收发最好不同层。

由于条件限制,收发必须同层的话,要保证收发之间有足够的隔离。

如果收发连接使用了连接器,进行pin分配时,要确保收发pin之间有足够的隔离。同时信号pin要邻地。

根据具体实现,确定各补偿模块补偿值

传输通道确定后,通过后仿真确定传输损耗。根据仿真得到的和传输通道损耗值,合理分配发送端和接收端各补偿模块的补偿值。最后进行整个链路的时域仿真,确定接收端眼图是否满足要求。

后续将继续介绍Serdes如何调试。

————————————————

版权声明:本文为CSDN博主「轻漂漂」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_44098748/article/details/85109634

Serdes原理与设计实践之三:Serdes调试过程

3. Serdes调试过程

1. 确定可配置参数及可获得的参数

Serdes可配置参数一般包括发送端的预加重、接收端的CTLE和DFE。具体有哪些参数可配置,需要查发送端和接收端芯片的spec来确定。

预加重:通常可配置前一阶和后一阶乘法器的系数。

CTLE:多数情况下是自适应的,某些设计是可配置的。通过查看接收端芯片spec来确定。

DFE:通常可配置的参数有DFE控制和tap数。

数字眼图:中高端芯片通常可以提供数字眼图功能,可以通过读寄存器等方式获得芯片接收机内部经过补偿后的眼图质量。

2. 确定接收端要求

数据速率较低时,接收端芯片一般是有实际眼图的要求。

数据速率较高时,接收端芯片一般是有数字眼图的要求。如果spec里没有,可与接收端芯片厂家沟通,获得数字眼图的要求。在芯片厂家无法提供这一要求的情况下,就需要在确定系统传输能力时,通过测量得出误码率和数字眼图的关系,以此来作为调试标准。

3. 调整可配置参数,使接收端满足spec要求

当数据速率较低时(一般不超过5Gbps),可使用示波器直接测量接收端实际眼图。通过调整预加重参数,实时测量,并与spec提供的眼图模板进行比较,看是否满足接收端要求。

当数据速率较高时,直接测试误差较大,需要使用数字眼图功能评估链路质量。需先确定CTLE和DFE的参数,然后调整Tx端预加重参数。每调整一次预加重参数,可以得到一个数字眼图,将其与spec里数字眼图要求进行比较,确定是否满足要求。

4. 进行压力测试

压力测试在高低温环境下进行。一般情况下,只调整预加重参数。测试通常分为两部分:

1)测试现有配置参数是否能够通过压力测试。如果不能通过测试,证明现有配置参数不太合理,需要进行调整。

2)将已配置好的参数向两端适当调整,看是否能够通过压力测试。如果不能通过测试,则说明现有配置参数可能处在配置范围的边缘,需根具情况将配置参数向中间调整,以保证系统有足够的裕量。

————————————————

版权声明:本文为CSDN博主「轻漂漂」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_44098748/article/details/85240083