基于FPGA的电子计算器设计(中)

今天给大侠带来基于FPGA的电子计算器设计,由于篇幅较长,分三篇。今天带来第二篇,中篇,话不多说,上货。

导读

本篇介绍了一个简单计算器的设计,基于 FPGA 硬件描述语言 Verilog HDL,系统设计由计算部分、显示部分和输入部分四个部分组成,计算以及存储主要用状态机来实现。显示部分由六个七段译码管组成,分别来显示输入数字,输入部分采用4*4矩阵键盘,由0-9一共十个数字按键,加减乘除四个运算符按键,一个等号按键组成的。通过外部的按键可以完成加、减、乘、除四种功能运算,其结构简单,易于实现。本篇为本人毕业设计部分整理,各位大侠可依据自己的需要进行阅读,参考学习。

第二篇内容摘要:计算器设计的电路部分,包括FPGA的最小系统、数码管电路、按键输入电路、电源电路设计等相关内容;还会介绍总体代码设计,包括计算机输入部分、运算及存储部分、显示部分等相关内容。

![]()

四、计算器设计的电路部分

![]()

4.1 FPGA的最小系统

FPGA最小系统是可以使FPGA正常工作的最简单的系统。它的外围电路尽量最少,只包括FPGA必要的控制电路。一般我们所说的FPGA的最小系统主要包括:FPGA芯片,下载电路,外部时钟,复位电路和电源。

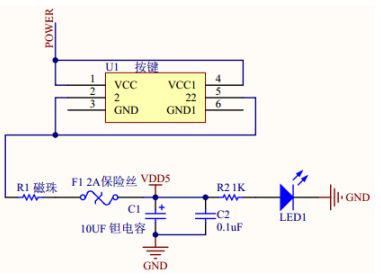

4.1.1 电源时钟复位

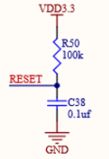

我们采用了低电平复位电路,电路图如下

图4-1 复位电路

Figure 4-1 reset circuit

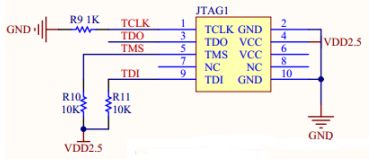

4.1.2 JTAG接口

JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。如今,JTAG接口还常用于实现ISP(In——System Programmer,在系统编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程然后再装到板上,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对DSP芯片内部的所有部件进行编程。

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。如今JTAG接口的连接有两种标准,即14针接口和20针接口。

支持边界扫描的逻辑元器件与测试相关的所有外部通信都采用串行通信方式,允许测试指令及相关的测试数据串行送给元器件,然后允许把测试指令的执行结果从元器件中串行读出。为了完成这样的功能,边界扫描技术包含了一个与元器件的每个引脚相接,包含在边界扫描寄存器单元中的寄存器链,这样元器件的边界信号可以用扫描测试原理进行控制和观察,这也是边界扫描的含义。

图4-2 JTAG配置接口电路

Figure 4-2 the JTAG configuration interface circuit

4.1.3 FLASH

闪存存储器是一类非易失性存储器,即使在供电电源关闭后仍能保持片内信息。数字电路中经常需要使用大容量存储器,串行Flash存储速度快,体积小,功耗低,在FPGA中设计中发挥的作用也越来越大,广泛应用于实现系统及功能验证。FPGA的灵活性和串行Flash的体积小的特点相结合,具有灵活性强实用性强等特点。我们的Flash程序存储电路如图4-3所示。

图4-3 Flash程序存储电路

Figure 4-3 Flash program memory circuit

![]()

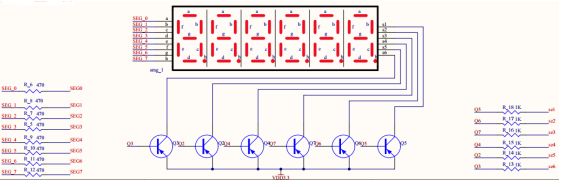

4.2 数码管电路

我们应用的LED数码管段数为7段,就是7个发光二极管,任意一个阿拉伯数字0-9都是可以通过亮灭组合来实现的。LED数码管根据LED的接法不同分为共阴和共阳两类,共阴极数码管公共端接地,共阳极数码管公共端接电源,另一个非公共端的引脚留给用户的I/O直接控制了,在这里我们采用共阳极数码管。我们在这个应用中,把公共端连接到了FPGA的I/O引脚上,这就是我们数码管的片选信号。如果我们FPGA的I/O引脚输出低电平0,那么这个数码管就是可以显示数字的,如果我们这个I/O输出高电平1。那么即使不管数码管的段选端输出0还是1,都没有办法将这7个发光二极管的任意一个点亮,这也达到了关闭数码管显示的效果。一旦这样,这个数码管的公共端被当作数码管片选引脚使用了,虽然不是名副其实的“片选”,也是可以达到我们想要的效果。了解LED的这些特性,对编程是很重要的,不同类型的数码管,除了它们的硬件电路有差异外,方法也是不同的。

图4-4 数码管电路图

Figure 4-4 digital tube circuit diagram

![]()

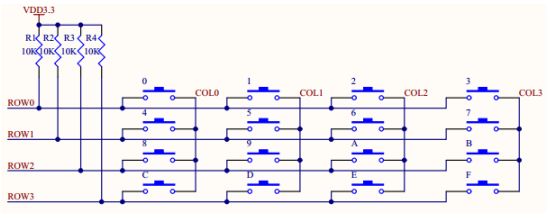

4.3 按键输入电路

我们要实现一个计算器,首先需要有计算器的输入信号,通常是使用连接在FPGA的GPIO接口上的pushbutton作为输入信号。简易计算器的输入信号比较少,只需要数字和运算符号。我们可以将其各自使用一个按键来表示,然后都连接在FPGA的通用接口上。此时,我们便引入了矩阵键盘构造计算器的输入。

我们采用的是4*4矩阵键盘电路,矩阵键盘又称行列式键盘,它是用4条I/O线作为行线,4条I/O线作为列线组成的键盘。在行线和列线的每一个交叉点上,设置一个按键。这样键盘中的按键的个数就是4*4=16个。这种行列式键盘结构能够有效地提高单片机系统中I/O口的利用率。其中的ROW0,ROW1,ROW2,ROW3,以及COL0,COL1,COL2,COL3信号分别连接到了FPGA上,使用一种独特的方法,这8个信号能够表示出16个按键各自按下的状态。即这16个按键只占用了FPGA的8个管脚,而使用每个按键都连接到了FPGA的输入管脚需要占用16个管脚。

行列矩阵采用了扫描的形式,其8个连接到FPGA上的信号是4个输入4个输出的。我们一般使用的其他按键方法都是将按键产生的信号作为输入。在这里,ROW0-ROW3为FPGA的输入信号,COL0-COL3是FPGA的输出信号;电路上,ROW0-ROW3还要连接一个上拉电阻。

如果左上方第一个按键被按下,ROW0和COL0连接在一起;如果不按下,两个信号则没有连接。16个按键表示16种连接的关系,在没有按键按下的时候,输出的COL信号就悬空了,输入的4个ROW信号收到上拉电阻的影响都是高电平1。如果说连接COL3与ROW2的按键被按下,那么FPGA的输入信号ROL2就等于输出信号COL3的值,其他的ROW输入信号则全部为1。

我们在FPGA内部使输出的COL0信号为0而其他的COL是1,那么不管其他的列上对应的按键都怎么按下,都有输入的FPGA的ROW为全1;仅仅当第一列的4个按键中有一个按下时,对应的行值为0,其余3个的行值为1,这样的话第一列所对应的按键就唯一确定下来了。在这样的输出状态下(COL[3:0]=1110),4个输入只能确定出来第一列的4个按键。要是按下的不是第一行的4个按键,那么输入值ROW[3:0]为1111,表示第一列没有按键被按下。于是我们开始扫描第二列,就是令COL[3:0]输出1101,然后查看ROW上是否有值为0。如果此列上仍然没有扫描到,就继续扫描下一列。

对于一组数码管动态扫描显示需要由两组信号来控制:一组是输出口输出的字形代码,用来控制显示的字形,称为段码;另一组是位输出口输出的控制信号,用来选择第几位数码管的工作,称为位码。

由于各位数码管的段线并联,段码的输出对各位数码管来说都是相同的。因此,同一时刻如果各位数码管的位选线都处于选通状态的话,位数码管将显示相同的字符。若要各位数码管能够显示出与本位相应的字符,就必须采用扫描显示方式。即在某一时刻,只让某一位的选线处于导通状态,而其他各位的位选线处于关闭状态。同时,段线上输出相应位要显示字符的字形码。这样同一时刻,只有选通的那一位显示出字符,而其它各位则是熄灭的,如此循环下去,就可以使各位数码管显示出将要显示的字符。

虽然这些字符是在不同时刻出现的,而且同一时刻只有一位显示,其它各位熄灭,但是由于数码管具有余辉特性和人眼有视觉暂留现象,只要每位数码管显示间隔足够短,给人眼的视觉印象就会是连续稳定地显示。

图4-5键盘电路

Figure 4-5 The keyboard circuit

![]()

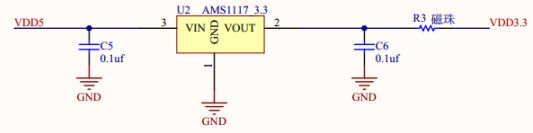

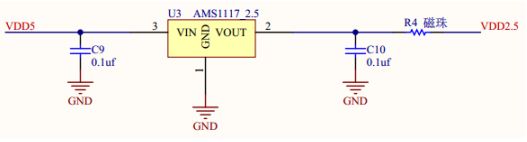

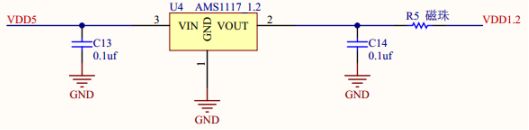

4.4 电源电路设计

我们使用的是LM1117,LM1117是一个低压差电压调节器系列。其压差在1.2V输出,负载电流为800mA时为1.2V。它与国家半导体的工业标准器件LM317有相同的管脚排列。LM1117有可调电压的版本,通过2个外部电阻可实现1.25~13.8V输出电压范围。另外还有5个固定电压输出(1.8V、2.5V、2.85V、3.3V和5V)的型号。

LM1117提供电流限制和热保护。电路包含1个齐纳调节的带隙参考电压以确保输出电压的精度在±1%以内。LM1117系列具有LLP、TO-263、SOT-223、TO-220和TO-252 D-PAK封装。输出端需要一个至少10µF的钽电容来改善瞬态响应和稳定性。

图4-6 5V转数字3.3V电路

Figure 4-6 5V to 3.3V circuit

图4-7 5V转数字2.5V电路

Figure 4-7 5V to 2.5V circuit

图4-8 5V转数字1.2V电路

Figure 4-8 5V to 1.2V circuit

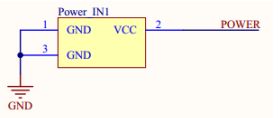

图4-9 电源插座电路

Figure 4-9 power socket circuit

图4-10 电源开关电路

Figure 4-10 power switch circuit

![]()

五、总体代码设计

![]()

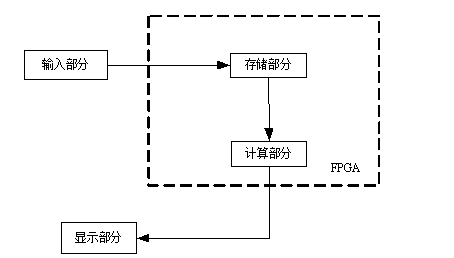

系统总体设计框图如图5-1所示。此设计由计算部分、存储部分、显示部分和输入部分组成。

图5-1 计算器的系统组成框图

Figure 5-1 calculator system composition block diagram

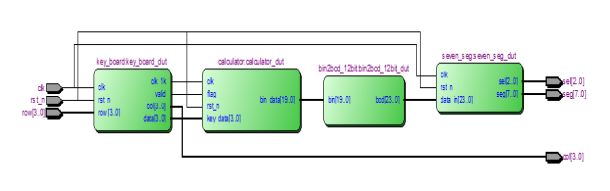

图5-2 RTL视图

Figure 5-2 RTL view

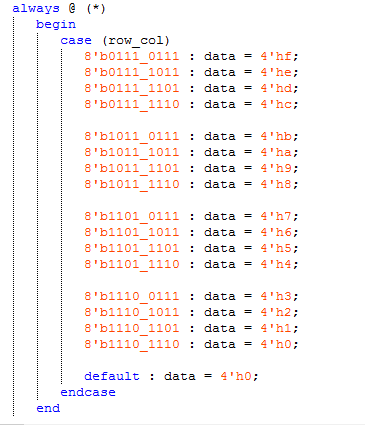

5.1 计算器的输入部分

计算器输入部分的设计最主要的是按键译码电路的设计和实现。计算器的输入部分是由0—9十个数字按键、加减乘除四则运算的运算符按键、一个等号按键和一个清零按键组成的,设计所要做的是对按键信息进行译码,使其在计算器内部可以使用。这里使用的是4*4键盘矩阵作为输入。数字按键译码电路的主体部分Verilog语言描述如下。

图5-3 数字电路译码部分代码

Figure 5-3 digital tube display program code

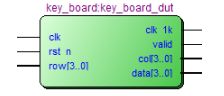

设计的键盘矩阵输入模块如图:

图5-4 键盘矩阵驱动模块

Figure 5-4 matrix keyboard driver module

在输入键盘矩阵驱动模块中,我们有三个输入,四个输出,其中clk为主时钟输入,rst_n为复位信号,row为4*4键盘的行输入信号,输出col列信号,data为键入的数字(0-15),valid为数字的脉冲信号,clk_1k为给计算模块输出的时钟。

![]()

5.2 计算器的运算和存储部分

存储部分用状态机和寄存器来实现,我们输入的数字应用了移位拼接的原理,若第一个输入的是数字键,则保存下来,第二次输入还是输入的是数字键时,第一个数值左移变为十位,第二次的为个位,第三次若还是数字键,那么第一个数值将变为百位,第二个为十位,第三个为个位,以此类推,直到有符号键输入。

当进行第一次计算时,第一个数字存放在num1里面。按下运算符以后,第二个数字放在bin_data里面。当再按下运算符号或者等号时,第一次计算的结果将存放在ans里面,同时reg清零,等待下一个数字的输入。进行第二次运算时,将num1里面的结果与reg里面新输入的数字进行运算,再将运算结果存放在num1里面,直到最后按下等号按键的时候,显示最终的运算结果。

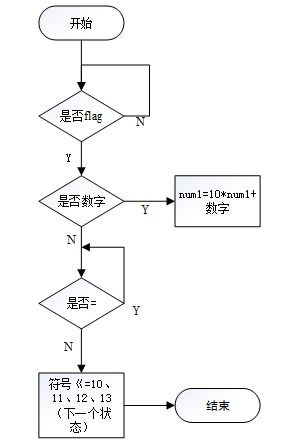

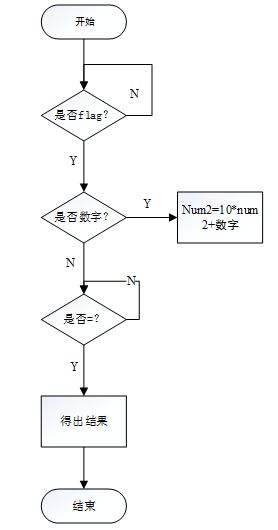

程序框图如下:

图5-5 状态1程序框图

Figure 5-5 state 1 program block diagram

图5-6 状态2程序框图

Figure 5-6 state 2 program block diagram

计算部分驱动模块如图5-7所示,共有4个输入部分,一个输出。其中clk为时钟,flag为数字脉冲信号,rst_n为复位,key_data为按键数据输入,bin_data为二进制中间数据输出。

图5-7 计算部分驱动模块

Figure 5-7 calculation part of the driver module

![]()

5.3 计算器的显示部分

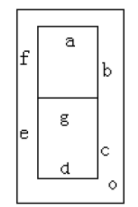

显示部分是系统的输出部分,用于显示按键值及计算结果,由于数字系统的数据运算都是二进制的,而输出表达式都是BCD码,为了满足BCD码的译码显示,最方便的方法就是利用译码程序在FPGA中实现。本文采用的是共阳极7段数码管,显示数字时需要将对应管脚置为低电平,输出时,从左到右,按从高到低位的顺序依次接g、f、e、d、c、b、a,小数点为h,为最高位。七段译码器的基本结构如图5-8所示。

图5-8 七段译码器的结构

Figure5-8 The structure of the seven-segment decoder

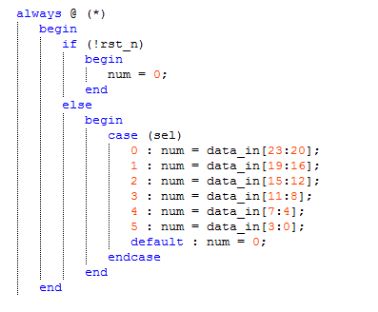

Verilog硬件位选信号描述性语言描述如下图5-9所示:

图5-9 数码管显示位选程序代码

Figure 5-9 digital tube display program code

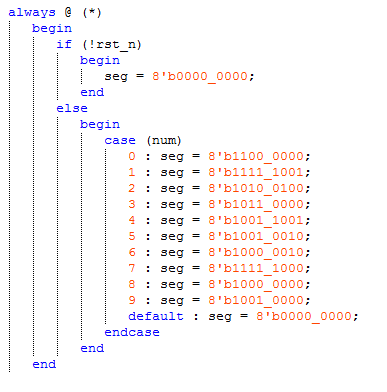

Verilog硬件段选信号描述性语言描述如下图5-10所示:

图5-10 数码管显示段选程序代码

Figure 5-10 digital tube display program code segment

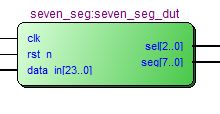

图5-11 数码管显示驱动模块

Figure 5-11 digital tube display driver module

图5-11为数码管显示驱动模块,一共三个输入,两个输出,其中clk为时钟,rst_n为复位,data_in数据输入,sel为位选信号,seg为段选信号。

![]()

本篇到此结束,下一篇带来基于FPGA的电子计算器设计(下),介绍仿真验证设计等相关内容,附录代码。

END

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

![]()

精彩推荐

毕设:基于FPGA的FIR数字滤波器设计

基于FPGA的千兆以太网设计

在word文档中添加“原汁原味”代码

“FPGA产品设计与研发 ” 零基础入门及就业