1 Overview

与传统的并行实现方法相比,基于串行I/O的设计具有很多优势,包括:器件引脚数较少、降低了板空间要求、印刷电路板(PCB)层数较少、可以轻松实现PCB设计、连接器较小、电磁干扰降低并具有较好的抗噪能力。

2 高速串行通信中用到的技术

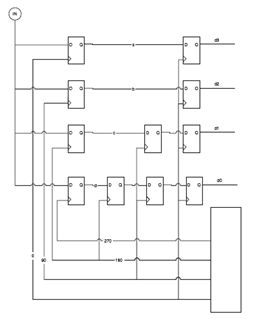

2.1多重相位

高速的秘密在于多重相位技术。所谓多重相位,就是在一个时钟的不同相位提取数据,例如,由锁相环产生多个不同相位的同源时钟,相位分别为 0°、90°、180°、270°,使用这几个时钟分别对串行数据流进行采样,再经零相位时钟同步,最后转换为并行数据输出,从而实现低速时钟处理高速时钟数据。若输入的串行数据流比特率为x,则并行数据流的比特率变为x/4。

2.2线路编码

2.21 8b/10b编码

- 将发送的8bits数据分为两部分:高3位(记为HGF)、低5位(记为EDCBA),记为D.X.Y(X代表EDCBA,Y代表HGF);高3位进行3b/4b编码(记为fghj),低5位进行5b/6b编码(记为abcdei)。

HGFEDCBA => abcdeifghj

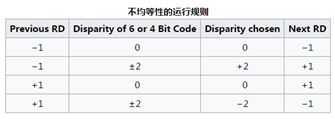

- 定义一:在abcdeifghj中,1比0多一个记为+2;0比1多一个记为-2;1和0一样多记为0。使用+2、-2、0三个值表示了该数据0和1个数的不均等性(Disparity)。

- 定义二:该次传输的1比0多记RD = +1,0比1多记RD = -1;其中,RD为运行不均等性(Running Disparity)。

- 初始发送状态的Previous RD定义为-1,那么根据表格1中的规则即可根据前一次的RD从编码表中挑选出当前应该发送数据的Disparity。

- 除了需要编码的256个D.X.Y数据外,其余数据中的12个作为K码:K.X.Y,例如:K.28.1, K.28.5, and K.28.7 称为"comma symbols"。

8b/10b(64b/66b、128b / 132b)编码技术保证了发送数据通道中的直流平衡,减小了差分信号中的直流分量,易于接收端恢复时钟。

2.3发送预加重

由于传输线具有低通滤波器的性质,在电路板传输的高速信号会出现明显衰减,特别是趋肤效应和电介质损耗的影响。传输线上的信号边沿斜率变缓,码元变宽,幅度下降,抖动增加,导致眼图闭合,误码率上升。

预加重电路将信号进行一定量的过驱动,增加信号的高频分量,经传输线后仍能保持标准信号的特征,提升眼图质量,降低误码率。

2.4接收均衡

除了在发送端采用预加重或去加重技术外,在接收端一般采用接收均衡技术提高系统性能。

接收均衡器频率特性正好与传输线相反,通过放大信号的高频信号,保持低频信号,来补偿传输线对信号的衰减,改善眼图性能,保证传输质量。

3 Xilinx FPGA Transceivers

3.1系统架构

The 7 series FPGAs GTX and GTH transceivers are power-efficient transceivers, supporting line rates from 500 Mb/s to 12.5 Gb/s for GTX transceivers and 13.1 Gb/s for GTH transceivers. Four GTXE2_CHANNEL primitives and one GTXE2_COMMON primitive to be a Quad.

GTX收发器的TX RX相互独立,但都是由PMA(Physical Media Attachment,物理媒介适配层)和PCS(Physical Coding Sublayer,物理编码子层)组成。PMA内部集成了高速串并转换(Serdes)、预加重、接收均衡、时钟发生器和时钟恢复等;PCS内部集成了8b/10b编解码、弹性缓冲区、通道绑定和时钟修正等。

3.2 TX

OOB:Out-Of-Band/边带信号;

PISO:Parallel In Serial Out/并进串出;

3.21 8b/10b Encoder/8b/10b编码器

8B/10B is an industry standard encoding scheme that trades two bits overhead per byte for achieved DC-balance and bounded disparity to allow reasonable clock recovery. 高速收发器的发送端一般都带有8b/10b编码器。目的是保证数据有足够的切换提供给时钟恢复电路,编码器还提供一种将数据对齐到字的方法,同时线路可以保持良好的直流平衡。在GTX应用中,如果发送的是D码,则需要将TXCHARISK拉低,如果是K码,则将相应的TXCHARISK拉高。

3.22 Pattem Generator/ PRBS产生器

Pseudo-random bit sequences (PRBS) are commonly used to test the signal integrity of high-speed links.GTX拥有伪随机数列产生电路,伪随机数列是之中看似随机,但是是有规律的周期性二进制数列,有良好的随机性和接近白噪声的相关函数,所以伪随机数列可以用来做误码率测量、时延测量、噪声发生器、通信加密和扩频通信等等领域,在GTX中可以用来测试高速串行通道传输的误码率。

3.23 TX Phase Adjust FIFO/相位调整FIFO

我们都知道FIFO具有隔离时钟域的功能,在这里也不例外,我们从图中可以知道,TX Buffer连接着两个不同的时钟域XCLK和TXUSRCLK,在发送端的PCS子层内部包含两个时钟域,XCLK(PMA并行时钟域)TXUSRCLK时钟域,为了数据发送的稳定,XCLK和TXUSRCLK必须是速率匹配,相位差可以消除的,TX Buffer主要用于匹配两时钟域的速率和消除两时钟域之间的相位差。

3.24 TX Polarity Control/发送极性控制

TX发送端支持对TX发送的数据进行极性控制,从PCS子层输出的编码数据在进入PISO串行化之前进行极性翻转,这部分功能主要是用来弥补PCB的设计错误,如果PCB设计时不慎将TXP和TXN交叉连接的话,可以通过设置TXPOLARITY为“1”来翻转信号的极性。

3.3 RX

EQ:Equalizer/均衡器;

OOB:Out-Of-Band/边带信号;

CDR:Clock and Data Recovery/时钟恢复;

SIPO:Serial In Parallel Out/串进并出;

3.31 RX Equalizer (DFE and LPM)/均衡器

RX信号从模拟前端进来之后,首先经过RX均衡器,均衡器的主要作用是用于补偿信号在信道传输过程中的高频损失,因为信道是带宽受限的,所以信号经过它必将造成衰减甚至遭到破坏。RX接收端的均衡器有两种,分别是LPM和DFE,两者功耗和性能有所不同,其中LPM功耗较低,DFE能提供更精确的滤波器参数,从而可以更好的补偿传输信道损失,因此性能更好。

3.32 RX CDR/时钟恢复

因为GTX传输不带随路时钟,因此在接收端必须自己做时钟恢复和数据恢复,首先外部数据进来之后经过均衡器,紧接着均衡器出来的数据就进入时钟数据恢复电路。GTX使用相位旋转CDR结构,从DFE进来的数据分别被边缘采样器和数据采样器捕获,然后CDR状态机根据两者决定数据流的相位并反馈控制相位内插器(PI),当数据采样器的位置位于眼图中央的时候边缘采样器锁定到数据流的传输域。其中CPLL或者QPLL为相位内插器提供基础时钟,使CDR状态机能很好进行相位控制。

3.33 RX Polarity Control/接收极性控制

和TX发送端一样,RX接收端也拥有极性控制功能,可用于实现数据翻转,在PCB设计时RXP和RXN接反时使用这个功能。

3.34 RX Comma Detect and Align/K码检测与对齐

串行数据在被并行化之前,需要找到一个合适的特征边界,这个特征边界或者字符边界是由TX发送端发送的一个可识别序列,通常称为标识符(comma)或者K码,接收端在到来的数据中搜索这个标识符,当找到这个标识符之后,后面接收的数据都已这个标识符为边界进行并行化,其工作原理如图所示。

3.35 RX PRBS Checker/PRBS检查器

GTX包含一个内嵌的PRBS检查器,如图4所示,有四种不同的伪随机序列生成器可以选择,检查器是自同步的,且工作在边界对齐和解码之前,这个功能可以用来测试信号的完整性。

3.36 RX Elastic Buffer/接收弹性缓冲

RX接收端弹性缓冲器是一个重要的功能,和TX接收端缓冲相比,RX多出了一个“弹性”属性,意味着和TX发送端相比,RX弹性缓冲器有更多的功能(RX时钟纠正和RX通道绑定)。

3.37 RX Clock Correction/时钟校正

RX弹性缓冲器的“弹性”反映在可以通过时钟纠正来调整XCLK和RXUSRCLK的频率差。对于RX接收端来说,即便XCLK和RXUSRCLK运行在同一个时钟频率,但往往存在一定的差异,这种差异很容易导致RX弹性缓冲器写满或者读空,时钟纠正功能应运而生。

通俗的讲,在TX发送端的时候,我们会定期的发送K码用于保证接收端边界对齐,在RX弹性缓冲器里面数据不足的时候,接收到的K码数据将被复制写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。当RX弹性缓冲器数据过多的时候,接收到的K码数据将被舍弃不写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。

3.38 RX Channel Bonding/通道绑定

通道绑定功能同样体现RX弹性缓冲器的“弹性”之处,对于像PCIE和SRIO等协议,可以支持多lane传输来提高传输总带宽。因为传输信道的原因,TX发送端同一时刻发送的数据在RX接收端不能被所有的lane同一时刻接收,每一个lane接收存在时间差,那么在恢复数据的时候就要重新对齐,因此需要在RX接收端执行通道绑定功能。

为了实现这个功能,TX发送端在发送的数据流中加入一个同样的通道绑定序列,RX接收端根据每一个lane检测到的通道绑定序列在各自的RX弹性缓冲器做相应的调整和延迟,最终使得各个lane的数据不存在偏移,在FPGA RX Interface的输出能和TX发送端发送的数据一样,功能如图所示,左边是未对齐数据,右边是对齐的数据。

4 实例

4.1 GTX配置(Xilinx ZC706)

The ZC706 board provides access to 16 GTX transceivers:

• Four of the GTX transceivers are wired to the PCI Express x4 endpoint edge connector (P4) fingers

• Eight of the GTX transceivers are wired to the FMC HPC connector (J37)

• One GTX transceiver is wired to the FMC LPC connector (J5)

• One GTX transceiver is wired to SMA connectors (RX: J32, J33 TX: J35, J34)

• One GTX transceiver is wired to the SFP/SFP+ Module connector (P2)

• One GTX transceiver is unused and is wired in a capacitively coupled TX-to-RX loopback configuration

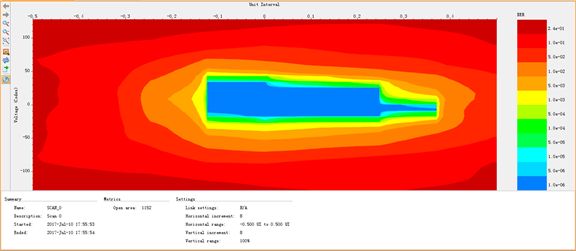

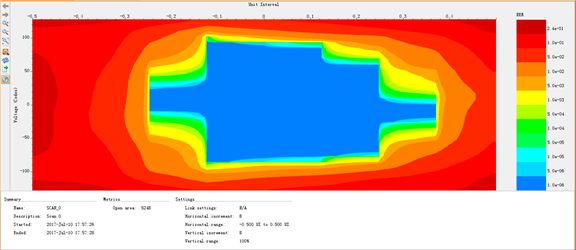

4.2 IBERT眼图

使用Xilinx IBERT(Integrated Bit Error Ratio Tester) IP测试GTX传输信道质量。

图 1 引脚直连

图 2 SMA引脚回环(未拧紧)

图 3 SMA引脚回环(拧紧)

6 参考

- http://xilinx.eetrend.com/blog/10730;

- http://xilinx.eetrend.com/blog/10745;

- Xilinx 7 Series FPGAs GTX/GTH Transceivers User Guide UG476 (v1.12) December 19, 2016;

- Xilinx Integrated Bit Error Ratio Tester 7 Series GTX Transceivers v3.0 LogiCORE IP Product Guide Vivado Design Suite PG132 June 8, 2016。