将正确的ADC与应用程序匹配

这是一个由数字计算机控制的模拟世界。因此,物联网设备的设计者需要有效地将模拟值转换为采样数字表示。而简单的答案似乎是把一个模数转换器(ADC)的前面,并不是所有的ADCs都是一样的。因此,设计者需要理解各种拓扑结构以及它们如何映射到应用程序。

例如,ADCs已优化设计如采样率、功耗和精度特性。本文将在一些常见的ADC架构的背景下讨论设计需求。然后将介绍使用这些体系结构的应用程序,并展示它们是如何实现的。

模数转换器的作用

ADC是一种常用的电子集成电路或模块化装置,它将模拟信号(通常是电压)转换成一系列采样离散数字表示或数字。ADC执行三种不同的操作:采样,量化,编码。他们形成了许多共同的数字仪器仪表,如电压表、示波器和频谱分析仪的心。它们也被集成到数字电路的前端,它处理来自麦克风、加速计、光传感器和其他传感器的模拟信号,这些信号需要将其输出转换到数字域,这样微处理器就可以处理数据。

已经有许多ADC体系结构或拓扑结构已经被开发来对模拟信号进行采样和数字化。ADC的每种形式都有自己的特点、优点和缺点。给定应用程序的特定类型ADC的选择通常是由速度、分辨率、精度、功耗和物理尺寸的测量要求来定义的。

模数转换器的关键特性

ADC必须执行的第一个操作是对模拟信号进行采样。采样由采样保持或跟踪保持电路执行。采样或奈奎斯特定理要求采样率必须大于信号带宽的两倍,以便能够从数字化样品中重建模拟信号。因此,ADC的第一个显著特征是采样率,它决定了可以被数字化的最大信号频率分量。

ADC必须量化每一个样本,打破采样电压为有限数量的离散值。这个特性通常被描述为分辨率的位数。例如,如果一个信号被分解为8位,就意味着有28个或256个离散级别。16位ADC将把电压范围分解为65536个量化级。

分辨率和最大采样率由ADC硬件决定。一般来说,ADC分辨率越高,最大采样率越有限。

ADC的精度取决于分辨率和采样率。分辨率影响振幅精度和精度。影响振幅精度的其他因素是量化过程的线性性和垂直噪声的影响。采样率决定了定时精度和准确度。

物理尺寸和功耗是依赖于电路拓扑结构的其他属性。它们主要关注体积有限或可用电源的应用,如物联网设备或电池供电的便携式仪器。物理尺寸和功耗非常依赖于ADC拓扑。

闪光,直接,还是平行?

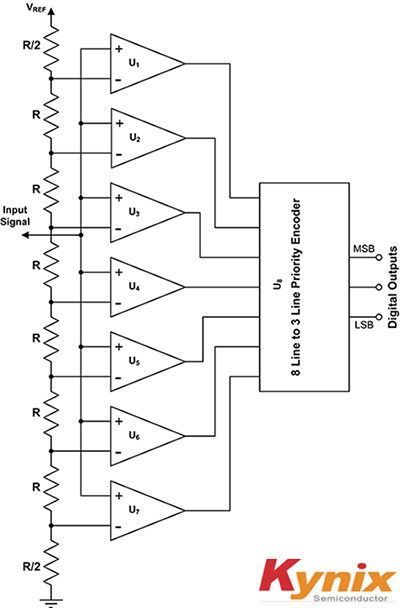

在概念上最简单的数字转换器是闪存ADC。这也可以称为直接或并行ADC(图1)。

flash ADC的图表使用多个比较器

图1:闪存ADC使用多个比较器,具有均匀递增的阈值电压,以将模拟电压转换为数字电压。这个例子显示了一个具有8位的分辨率水平3位ADC。(图片来源:凯利讯半导体电子)

闪存ADC的输入通常来自于采样和保持或跟踪保持电路,其中模拟输入被采样,并且在转换期间保持恒定。采样信号被应用到模拟比较器阵列,其阈值电压在ADC的输入电压范围内均匀地间隔在一个等于最小有效位(LSB)的值上。如果比较器的输入电压超过该比较器设定的阈值,则每个比较器的输出将改变状态。图中的例子显示了一个3位ADC需要7个比较器产生8种可能的状态。

一般来说,一个n位闪存转换器需要(2n-1)比较器。比较器产生所谓的“温度计代码”,输入电压越高,比较器的数量就越大,从底部到顶部就达到了“1”状态。此代码应用于优先级编码器,该编码器将此代码转换为二进制代码。

Flash转换器的主要优点是速度。转换时间只包括比较器和解码器的延迟。最大采样率达到每秒5千兆闪存转换器(GS/s)是市售的。闪光灯转换器分辨率的限制因素是所需比较器的数目。一个8位闪存ADC需要255个比较器。

这个数字增加了一倍,每增加一点分辨率。这意味着ADC的物理尺寸随分辨率呈指数增长。这就导致了另一个限制,即Flash转换器所需的功率。这限制了它对线驱动应用程序的使用。闪存分辨率的实际限制大约是8位。

二进制编码

ADC的二进制输出可以用几种方式编码。如果转换的信号是单极性的,那么它通常被编码成单极性的直二进制码。此代码表示一个零值作为所有0(0000…)和最大输入值作为所有(1111…)。

如果信号是双极性的,那么它通常被表示为偏移二进制或二进制补码二进制,详见4位示例(表1)。

双极性零 - 1 LSB

|

表1:用于双极数字信号的通用二进制编码。二进制补码二进制是微处理器或数学处理器最广泛使用的二进制。(图片来源:凯利讯半导体电子)

二进制补码二进制编码是大多数微处理器或基于数学处理器的系统所使用的编码类型,因为它便于算术运算。

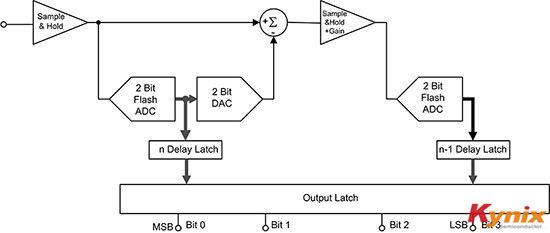

流水线ADC,子范围,和两步

闪速转换器中的比较器可以通过将转换分成两个或多个步骤并将每个步骤转换成较小的比特数来减少。如果闪存ADC被分成两部分,则称为两步或次测距ADC。如果将其分成两个以上的部分,则称为流水线ADC。两步ADC仍然可以在每秒数百兆采样样本(MS / s)(图2)。

4位、两步或次测距模数转换器的功能框图

图2:一个功能位,两步框图,或子范围ADC显示它打破了4位转换为两位转换器降低比较器的数目。(图片来源:凯利讯半导体电子)。

这两步器打破了4位转换器,这就需要15个比较器,两位段。每个部分使用三个比较器,总共有六个比较器。该转换器转换的两个最重要的位(MSB)第一。第一部分的数字输出包括数字-模拟转换器(DAC),以将信号转换为模拟信号,并从输入信号中减去它。

将所得的差异被放大,用来将两位。合并结果被捕获到输出锁存器中。转换过程重复两次,因此最大采样率将低于闪光灯转换器。模拟devicesad9203aruzrl7是一个10位的一个例子,40 MS/s流水线ADC的转换,解决了从模拟到数字的高速度的问题。

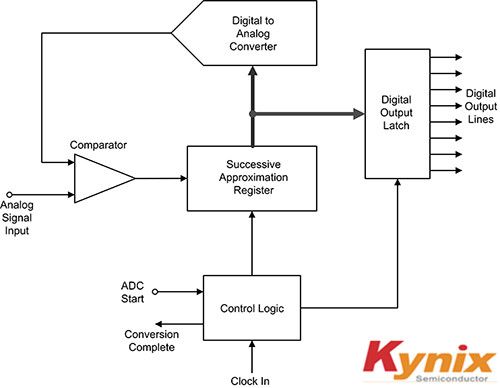

逐次逼近模数转换器(SAR)登记

当应用程序需要更大的分辨率,而不一定是闪存或流水线ADC的速度时,逐次逼近寄存器(SAR)转换器是一个不错的选择(图3)。SAR ADC工作在12到16位,采样率为1到2毫秒/秒高

合成孔径雷达ADC图提供了良好的分辨率。

图3:SAR ADC具有低到中等功率要求的良好分辨率。(图片来源:凯利讯半导体)

与闪存ADC一样,SAR ADC之前有一个采样保持或跟踪保持电路,以维持转换过程期间的采样值。来自采样和保持的信号被应用于比较器。逐次逼近寄存器从中档开始,并用DAC将该值转换为模拟电压。

这个“猜测”电压与比较器的信号输入进行比较。如果比较器输出保持低,寄存器值将增加四分之一的范围。从本质上讲,寄存器值是在两个步骤中降低或增加的,直到比较器指示DAC转换寄存器内容等于输入信号电压为止。当发生这种情况时,转换器发出“转换完成”信号,并将数字值锁存到输出锁存器中。

转换时间与ADC分辨率成正比,ADC分辨率是由寄存器的长度决定的。SAR ADC提供低分辨率好于中等功率的要求。一个低成本的一个例子,SAR是从低功耗集成的max11665aut-t。它是一个12位,500 kilosamples每秒(kS/s)SAR ADC,使它与数字化传感器输出。

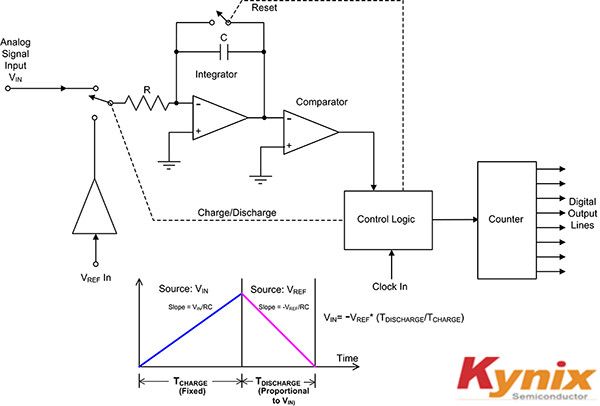

积分双斜率模数转换器

集成的ADC提供高分辨率的同时最大限度地降低噪声的影响。双斜率ADC是最常见的集成ADC(图4)。

双斜率积分模数转换器框图

图4:一个双斜率积分ADC的框图,包括一个图,显示电荷/放电时间是如何用来决定未知输入电压的。(图片来源:凯利讯半导体电子)

最初,输入连接到积分器。电容器C是由输入信号定时充电的。在充电时间完成时,积分器连接到基准电压。这将电容器按比较器决定的电容放电到零。计数器用来测量电容器放电所需的时间。在充电周期中,时间与电容器上的输入电压成正比。一个简单的关系,根据已知的充电时间和测量放电时间允许输入电压的计算。

由于信号输入被应用于积分器,所以通过积分器的平均效应最小化任何噪声信号的影响。双斜率转换器是高精度要求高精度应用的理想选择。12到16位的分辨率是常见的,最大采样率高达100。

双斜率ADC最著名的应用是数字电压表(DVM或表)。该集成模型icl7109cpl + 12位ADC具有三态输出的双斜率转换器用于测量的模拟信号,如压力、速度、流量,以高达每秒30次的速率。

∑ΔADC:高分辨率低频

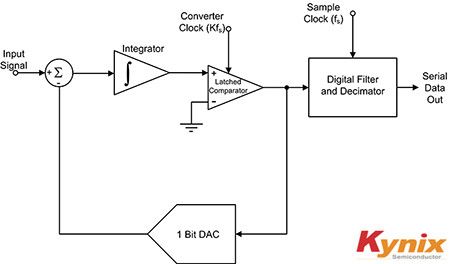

∑ΔADC为低频信号提供最高分辨率(16到24位)。像双斜率ADC一样,它是另一种积分式数字化仪(图5)。输入信号通过一个夏天应用到积分器。积分器的输出被应用于锁存比较器,并将其与零伏(地)信号进行比较。如果集成输出不是零,比较器输出反馈,使积分器输出接近零。这个过程在转换器时钟频率下重复,直到积分器输出达到零。比较器输出形成串行数据流,即转换器的数字输出。

∑-ΔADC的采样率要比设计的采样速率高很多。

在图中,转换器时钟比输出采样时钟快一个因数K。从这个“过度采样”的额外样本被用来提供转换器输出的数字滤波。抽取器的输出采样率恢复到指定的采样时钟速率。

模拟设备的模型ad7734bruz ADC是24位,4通道,用于处理和工业控制应用的∑-Δ数字化仪。

∑-Δ模数转换器图

图5:∑-ΔADC广泛用于音频、过程和工业控制应用的低频信号的高分辨率数字化。(图片来源:凯利讯半导体)

表2提供了所讨论的五种ADC类型的分辨率和最大采样率的摘要。

|

表2:本文讨论的五种ADC类型的ADC工作特性。(图片来源:凯利讯半导体电子)

拓扑结构选择的例子

考虑一个应用程序,从便携式超声波测距仪使用40千赫换能器的信号数字化。目标反射值是发射脉冲幅度的40分贝(1/100)。

信号必须在两倍于40千赫信号频率的最低频率下进行采样。最好是在40千赫或四千赫以上采样,所以所需的采样范围是160千赫或更大。这是一个好主意,设置一个分辨率,至少是预期的40 dBm的十倍,所以这将是60分贝。一般的经验法则是,每6分贝需要1位分辨率,因此需要10位或更多ADC。此外,这是一个便携式仪器,使功耗考虑。咨询表2,逐次逼近转换器是最好的选择。从集成的max11665aut-t,作为SAR ADC的例子,前面提到的,都是这一应用的一个很好的匹配。

结论

由于两者不能同时实现,ADC的选择主要是最大采样率和分辨率之间的折衷。其他考虑因素,如物理大小和功耗,取决于应用程序,应该在选择过程中给予适当的权重。