MIPI D-PHY介绍

术语简写:

Escape mode:是于data lanes 的一个可选模式,在该模式下,低速率的命令和数据可以以非常低的功耗进行传输。

CIL: Control and Interface Logic

LP-CD: Low-Power Contention Detector

LPDT: Low-Power Data Transmission

LPS: Low-Power State(s) 低功耗状态

PPI:PHY-Protocol Interface

APPI: Abstracted PHY-Protocol Interface 抽象物理层协议接口

ULPS:Ultra-Low Power State 超低功耗状态

D-PHY 定义了一种源同步,高速,低功耗以及低成本的PHY,主要是应用于移动手机行业。比如,用来连接显示屏(DSI)和摄像头(CSI)。包括DSI(串行显示)物理层和CSI(串行摄像)物理层定义。

D-PHY有三种不同类型的通道:

(1) 单向时钟通道

(2) 单向数据通道

(3) 双向数据通道

D-PHY有两种传输模式:

(1) HS 高速传输模式,用于传输突发数据,同步传输,信号为差分信号,电平范围为100mv-300mv,传输速度范围是80-1000Mbps,

(2) LP 低功耗模式,用于传输控制指令,异步传输,信号线为单端,电平范围是0-1.2v,没有用时钟线,时钟是通过两个数据线异或而来的,速度只有10Mbps。

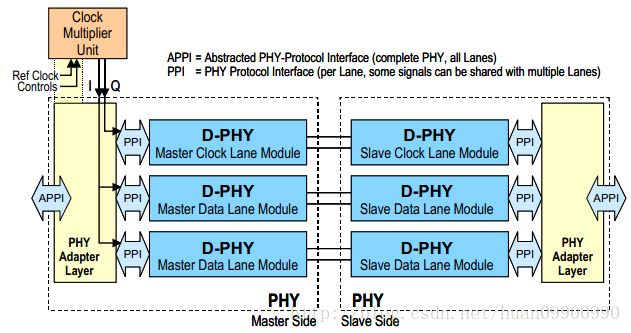

下图是主控制器和外围设备通过MIPI D-PHY连接的示意图:

Lane Module:用来发送或接收lane上的信号

PPI:PHY-Protocol Interface ,PHY协议接口

PHY Adapter Layer:APPI接口与PPI接口的转换

PHY的配置包括一个clock lane和一个或多个data lanes(最多4个data lanes),所有的data lanes都支持高速传输和正向时的escape mode

data lanes 有两种类型:

(1)双向口:能双向传输

(2)单向口:只能单向传输

双向的data lanes 必须包含下面的一个或两个反相通信功能:

(1)High-Speed Reverse Data Communication :高速反相数据传输

(2)Low-Power Reverse Escape Mode (including or excluding LPDT):反向低功耗 Escape Mode模式(包含或只有低功耗数据传输)

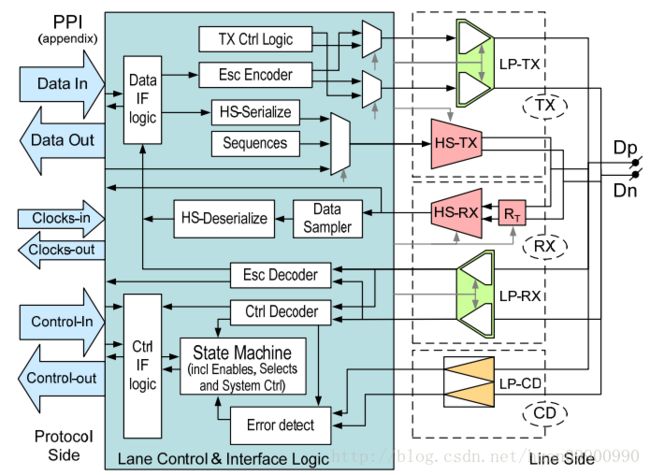

下图是一个通用的Lane Module 内部结构图,一个Lane Module的功能取决于Lane 类型(时钟,数据单向,数据双向)以及lane module是发送端还是接收端。

其主要由一个或多个高速收发模块(HS-TX,HS-RX),一个或多个单端低功耗收发模块(LP-TX,LP-RX)以及lane控制和接口逻辑模块(Lane Control &Interface Logic)组成。

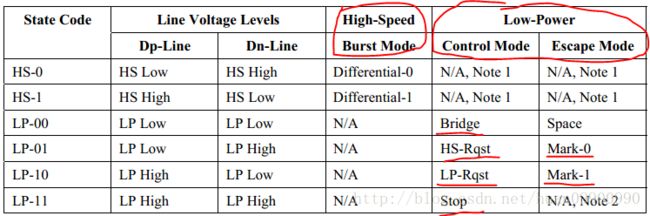

1、Lane State

lane 的不同传输功能通过驱动线上的不同电平来进入不同的lane state,正常操作时是HS-TX模块或LP-TX模块驱动lane。一个HS-TX模块总是差分地驱动一对data lane,两个LP-TX模块独立地驱动一个lane上的两根信号线,这种方式就使得有2种HS Lane 状态,4种Low Power lane状态。6种lane 状态如下表所示:

2、Operating Modes: Control ,High-speed and Escape

在正常操作时,data lane要么在 Control 模式要么在High-speed模式。在进行数据突发传输时,data lane就进入高速数据传输模式,其从 Stop State(LP11)开始高速数据传输,同样结束高速数据传输后又进入Stop State(LP11),Stop State是在Control 模式下定义的一个状态。data lane 只有在进行突发数据传输时才进入High-speed 模式,

3、High-speed Data Transmission 高速数据传输

3.1 Start-of-Transmission

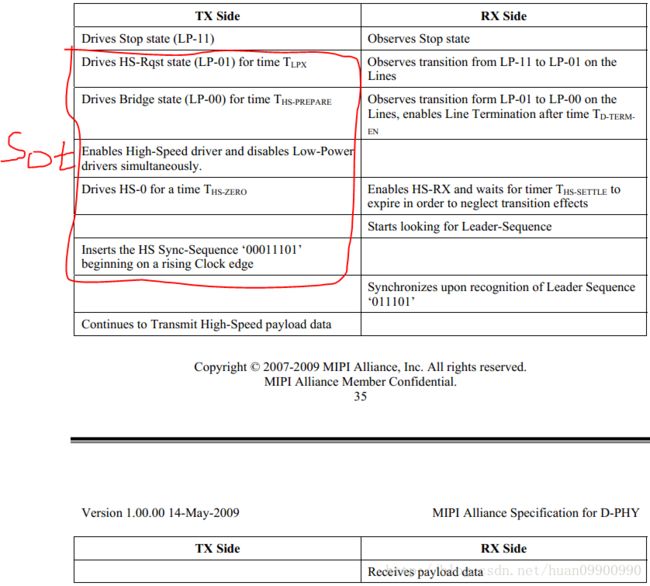

下图介绍了从停止状态开始发送数据的一个启动数据发送流程(Sot),在发送一个传输数据请求后,data lane 离开stop 状态,通过一个启动数据发送流程(Sot)为进入HS Mode 做准备:

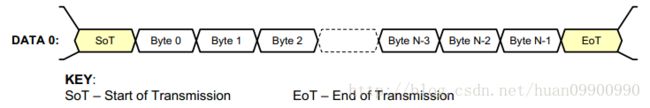

下图是一个lane发送一个transmission,这里的Sot 就是上图里启动数据发送那几个操作流程,同样Eot 对应后面图中的结束高速发送数据流程

3.2 End-of-Transmission

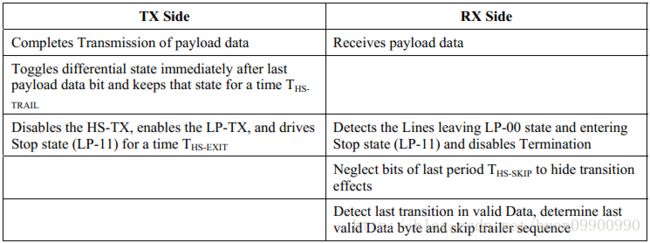

在Data Burst 结束时,Data Lane通过Eot 流程 离开High-Speed Transmission模式进入Stop 状态。Eot流程如下图所示:

3.3 HS Data Transmission Burst

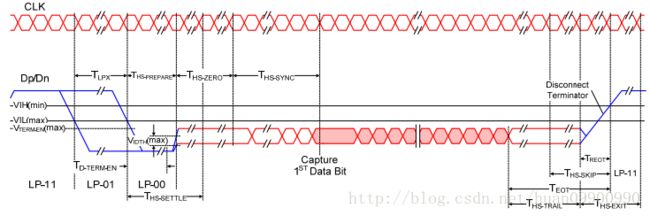

下图是一个Transmission进入高速突发模式传输的完整流程,包括从stop状态(LP11)进入HS流程(Sot),HS发送数据,退出HS流程(Eot) ,回到stop状态。

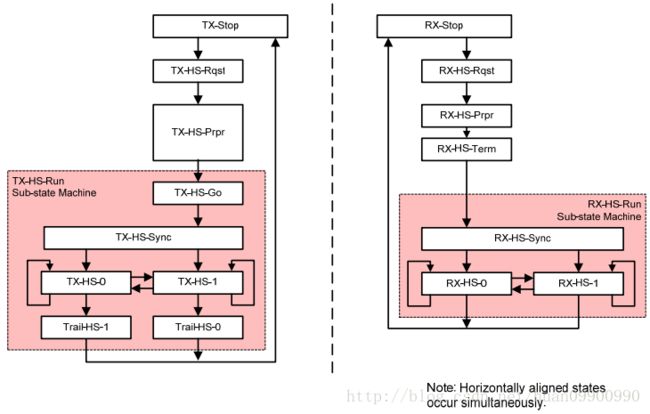

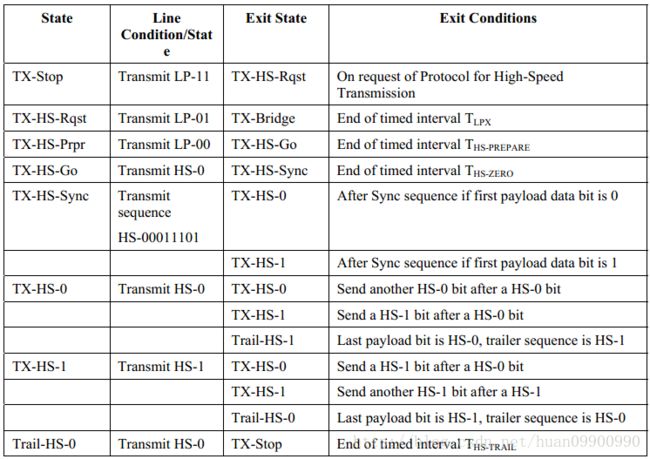

下图是HS Data Transmission 状态机流程图,左边是发送方,右边是接收方。

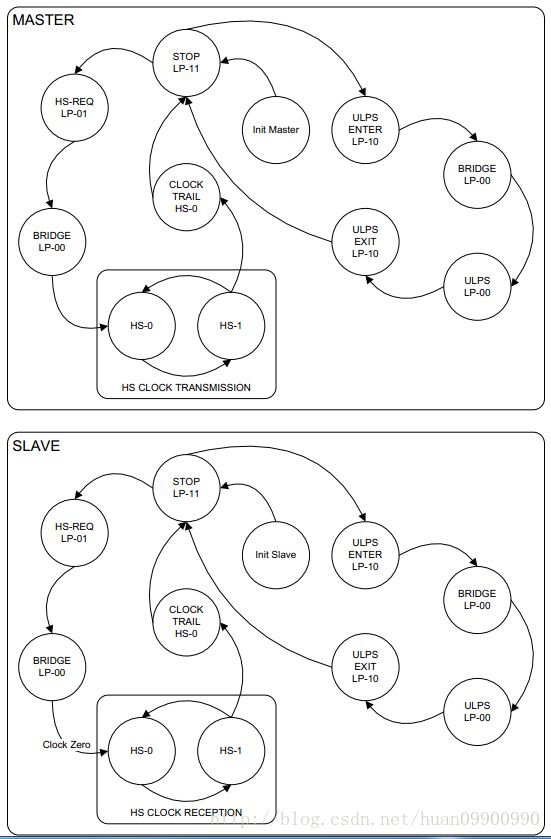

3.4 HS Clock Transmission

在HS 模式下,发送方同时通过时钟lane提供一个低摆幅的差分DDR时钟给接收方,用于高速数据接收,时钟lane模块被PHY 协议通过PPI时钟接口所控制,只有当所有的data lane 都没有进行高速数据传输时,clock lane 才会停止工作。

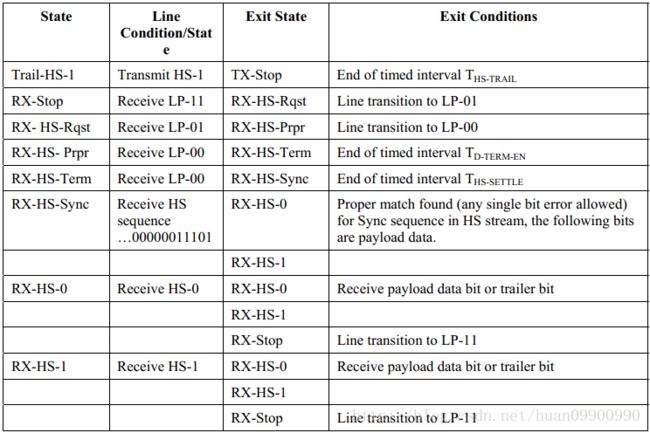

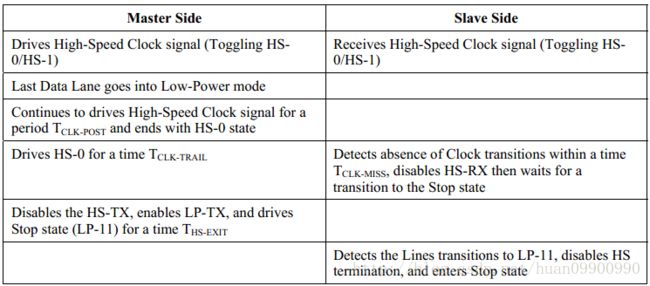

clock lane 跟单向的data lane类似,只是它传输的是差分的时钟信号。在最后一组data lane 进入 Low Power mode后 ,时钟信号会持续运行Tclk-post时间后,以HS-0状态结束。下图是在时钟高速发送模式与Low Power mode间切换的时序图。红线左边表示时钟从高速发送模式到Low Power 模式,红线右边是从Stop state 初始化到高速发送模式。

下面是具体从时钟高速发送状态进入Low Power mode的状态流程图

下面是初始化高速时钟发送的状态流程图

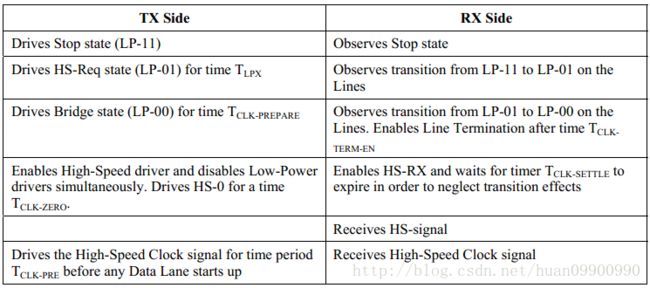

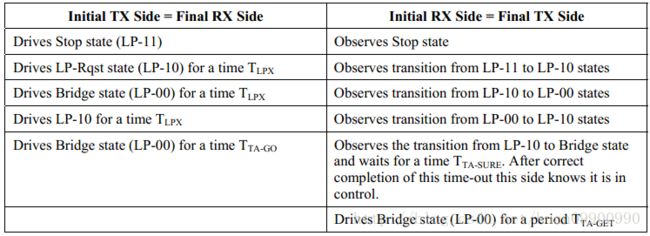

4、Bi-directional Data Lane Turnaround

通过Link Turnaround 流程能 改变具有双向功能的 data lane 的传输方向,比如现在是正向传输 ,通过Link Turnaround流程 就变成了反相传输。Link Turnaround流程只能在Control Mode下才能进行。

下表就记录了一个具有双向功能的data lane 改变传输方向的流程,表中左边一列初始状态是发送端,右边一列是接收端,在经过Turnaround 流程后 左边一列变成了接收端,右边一列变成了发送端。

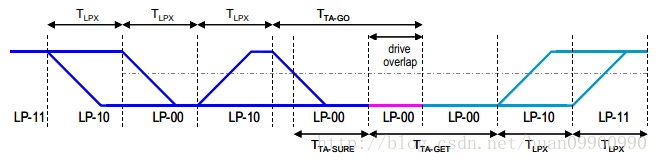

下面是Turnaround 反映到时序图上的过程

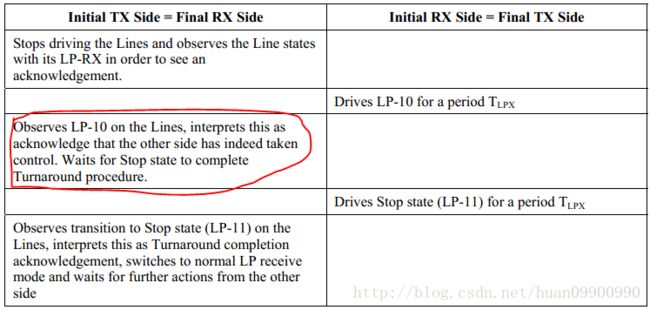

5、Escape Mode

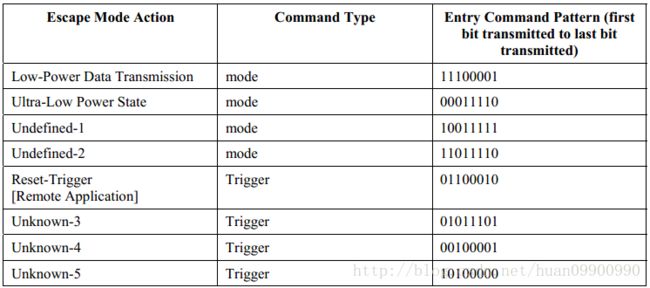

Escape Mode是一个比较特殊的模式,在该模式下,可以使data lane 进入Low-Power states,有了这个模式,就可以使用一些其他的功能。在正向传输时,是肯定支持Escape Mode的,但反向时可以不支持。Data lane 通过一系列进入Escape Mode的操作流程(LP-11,LP-10,LP-00,LP-01,LP-00)才能进入Escape Mode。只要最后的LP-00状态出现在data lane上,就进入Escape Mode了。如果在没有到最后的LP-00状态前,data lane上出现了LP11,则会退出进入Escape Mode流程。只要进入了Escape Mode,发送方就会发送一个8位宽的输入命令,来代表其请求的操作。

下表就是一些可以发送的请求操作命令,比如发送8位1110_0001,就表示将进入低功耗数据传输模式,发送0001_1110 就表示将进入超低功耗状态。

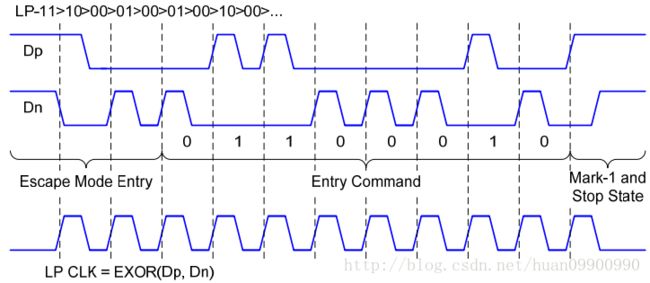

PHY在Escape Mode是用独热编码进行异步通信,所以,data lane 在Escape Mode时,不用时钟 lane,时钟是data lane的两根信号线Dp和Dn 异或而来的,下面就是在Escape Mode发送Reset-Triger命令的过程。首先肯定是进入Escape Mode流程,进入后再发送Reset-Triger命令。

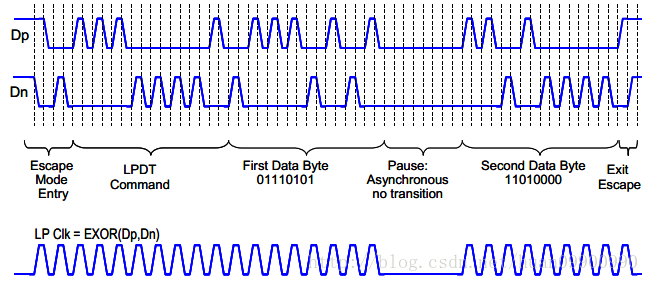

5.1 LPDT(Low-Power Data Transmission) 低功耗数据传输

如果在Escape Mode进入流程后紧跟的输入命令是1110_0001(Low-Power Data Transmission),则data lane进入 Low-Power Data Transmission以低速(10Mbps)进行数据传输。这样数据跟输入命令一样,同样是以独热码的编码方式进行传输,同样不需要时钟lane。Stop state出现在data lane时,停止LPDT,退出Escape Mode,进入Control mode。下图是一个低功耗发送2个字节的时序图。

5.2 Ultra-Low Power State 超低功耗状态

如果在Escape Mode进入流程后紧跟的输入命令是0001_1110(Ultra-Low Power State),则data lane进入 Ultra-Low Power State ,在该状态下,data lane 处于 space state (LP00)。

6、Global Operation Flow Diagram

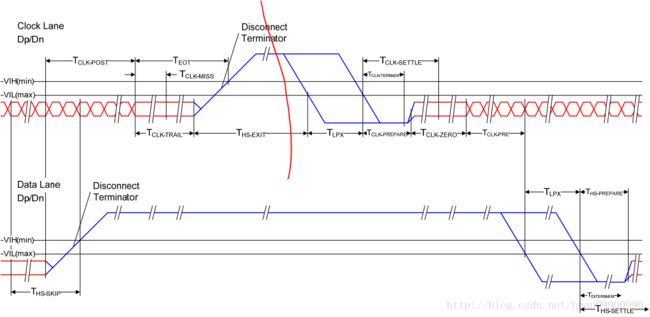

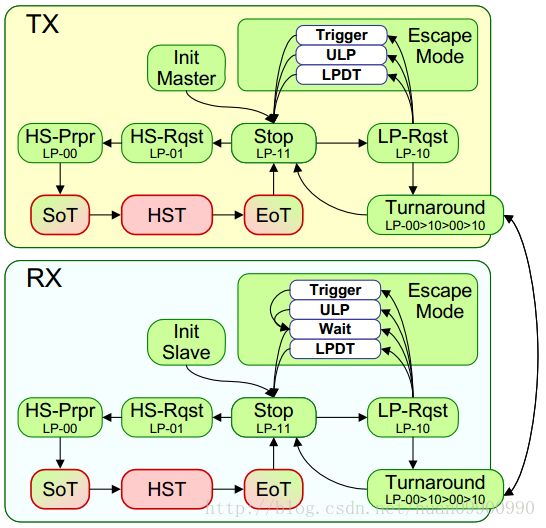

下图表示的是data lane 模块总的一个收发流程图,主要包括四个部分:High-Speed Transmission ,Escape Mode,Turnaround ,Initialization。

下图是对应上面的收发流程的状态机图