编码器设计

引言

并行ADC的主要优点就是可获得极高的模数转换频率及很小的转换延迟。特别是对嵌入式高速并行ADC而言,还需要满足低功耗和小面积的要求。然而在高速模数转换时,随着输入信号频率升高,噪声影响趋于严重,此外受预放大器及比较器带宽有限的影响,都会带来ADC误码率上升。误码率是ADC比较容易被忽视的一个重要性能指标。

当误码率极高时,转换所得数字码对应的波形呈现非连续现象且严重降低ADC的信噪比,从而降低ADC的有效分辨率。在某些用来测量窄脉冲或毛刺的系统中,对ADC的误码率提出很高的要求。

高速ADC中由于存在噪声或器件失配等诸多非可控因素的影响,单靠ADC前段完全消除误码是代价非常昂贵甚至不可能的,因此ADC编码器完成比较器输出的温度码/循环码向二进制的转换外,还需要增加相应误码校正电路以降低误码率。

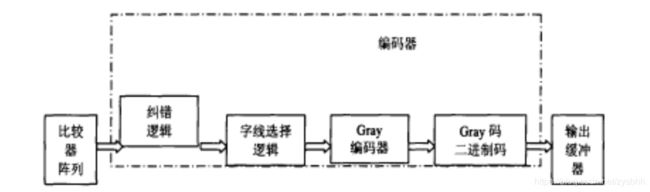

编码器结构

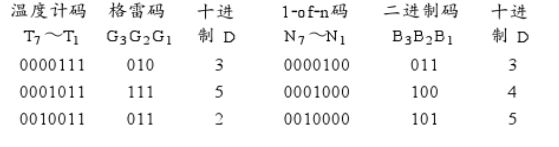

对ADC中并行多个比较器而言,理想情况下输入信号比对应参考电压高的比较器输出为1,反之则输出为0.对于flash ADC而言,其比较器阵列输出为温度码,即输入信号高于参考信号为全1,输入信号低于参考信号为全0.而对于折叠ADC,由前述的预处理器原理可知,其比较器阵列输出为循环温度码。二者和对应的二进制码如下所示:

无论是温度码还是循环温度码,其中0-1,1-0的转换位只有1个,因此如果实现温度码向二进制码或循环温度码向二进制码的转换,原则上只需要找到0、1之间的转换为就可以通过使用逻辑电路、ROM或者PLA确定相应二进制码

无论是温度码还是循环温度码,其中0-1,1-0的转换位只有1个,因此如果实现温度码向二进制码或循环温度码向二进制码的转换,原则上只需要找到0、1之间的转换为就可以通过使用逻辑电路、ROM或者PLA确定相应二进制码

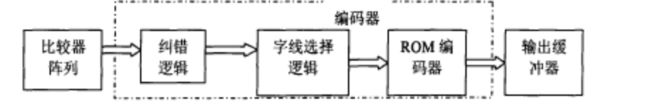

对应N位温度码,可以通过对相邻位做异或逻辑来判断0-1转换点位置,判断结果作为ROM编码器的字线选择逻辑来实现温度码向二进制的转换。

上表显示的仅是理想状况下的温度码和循环温度码,实际设计中,由于存在放大器非线性、器件匹配、噪声干扰等非理想因素,比较器的输出有可能产生亚稳态误码。误码的存在使比较器输出编码会出现不止1个0-1转换点,导致二进制编码错误,从而使ADC的信噪比下降,降低转换器的有效分辨率。因此并行ADC的编码器设计必须考虑误码矫正问题。

目前最常见的编码及误码矫正方法有Gray编码、quasi-Gray编码、邻码矫正逻辑、位交换技术等。

基于ROM编码的编码器基本结构如下图所示:

##

##

误码产生的原因

(1)采样误差

信号在采样过程中,使用的是非理想的MOS开关,因此电荷注入和时钟馈通效应会降低采样精度。由于高速并行CMOS ADC采样频率非常高,难以设计满足要求的高增益带宽积的运放,因此通常高精度采样中所用的“虚地”的方法难以使用,这使独立的高速采样/保持电路设计非常困难。而flash ADC中常用的直接通过比较器采样的方法,会由于比较器和预放大器信号贷款有限,造成高频输入信号时误码率严重上升的问题。折叠差值ADC由于信号预处理器对信号折叠作用产生额外的谐波失真,因此对采样误差要求更高。

(2)预放大器/预处理器非线性

通常并行ADC的比较器在实际进行比较前会使用预放大器进行信号预防大以增大信号增益、减小噪声干扰。折叠ADC为实现信号折叠还需要增加信号预处理器。因此这些放大器的非线性将会增大整个ADC信噪比中的谐波噪声成份,增大误码几率,降低ADC有效分辨率。

(3)比较器失调

由于高速比较器增益有限、工艺实现中造成的MOS管匹配误差(如尺寸失配、阈值失配、工艺不稳定性等)及噪声干扰等问题使比较器分辨率有限,因此当输入信号和相应参考信号非常接近时会造成比较器输出可能出现亚稳态误码现象。

(4)Kickback噪声

对并行ADC性能影响最严重的噪声是kickback噪声。kickback噪声指比较器或预放大器的信号放大过程中,输出大摆幅信号通过寄生电容被反馈到参考源,引起参考电压的波动。Kickback噪声会严重影响参考电压精度和稳定性,引起ADC信噪比下降,是高速ADC设计中必须考虑的问题。

误码

正确的进行编码并最终输出的前提是转换电路必须正确生成温度计码。由于转换电路中比较器的失调,亚稳态以及噪声的干扰,很容易造成温度计码中出现单独或者少量的0,从而形成火花码,进而在编码电路中造成相应地误码。一般以在连续的1中间出现0个数的不同而相应地称作一阶或二阶火花码,甚至更高阶,下表以一个三位ADC编码为例,出现一阶和二阶不同火花码时,两种编码方式对应的编码。

格雷码编码方式

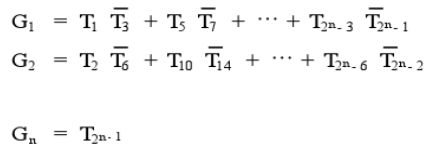

对于一个n位的ADC,从2^n-1位温度计码转换到n位格雷码满足:

二进制编码

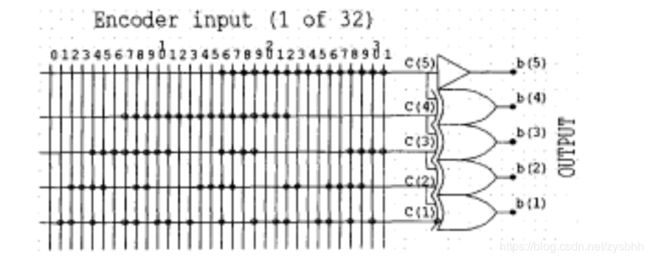

二进制编码对温度计码按照二进制数的规律进行编码。采用二进制编码时,通常先将温度计码通过1-of-n电路转换为只含有1个1的编码串,及1-of-n码,然后以ROM阵列的方式转换为二进制编码。

常用误差解决方案

由于格雷码编码特性,虽然不能完全消除火花码的影响,但对火花码引入的误差具有一定的抑制作用,因此格雷码是模数转换器中常用的一种编码方式。

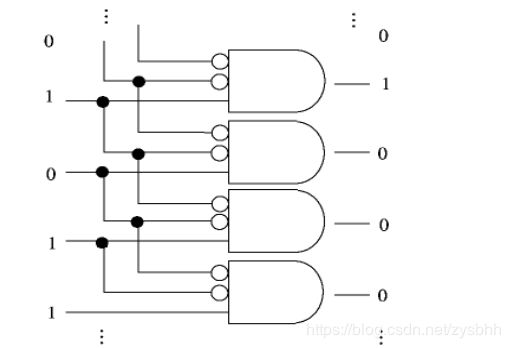

二进制ROM阵列编码中,采用三输入与门阵列,消除一阶火花码,形成只含有一个1的1-of-n编码,如下图所示。

这种方法最大的不足就是只能消除一阶火花码,对于高于二阶的火花码没有抑制作用,这样会导致高于二阶的火花码无法争取转换成相应的1-of-n码 。对于二阶或者高阶的火花码将增大误差。

这种方法最大的不足就是只能消除一阶火花码,对于高于二阶的火花码没有抑制作用,这样会导致高于二阶的火花码无法争取转换成相应的1-of-n码 。对于二阶或者高阶的火花码将增大误差。

格雷码最大的优势在于其特定的编码方式能对各阶火花码都具有一定的抑制作用。

Gray码的ROM编码器

即使在某种情况下出现瞬态亚稳态错误使2路字线同时被选中,也至多产生1LSB的误差,从而实现了“抑止气泡”的功能。

由于gray编码中相邻字线的编码之间只有1bit发生变化,因此即使发生2路字线同时被选中的情况,误差也会被控制在1LSB,不会产生大的编码误差。

gray编码器的构成如下图所示,由于从gray编码到二进制编码需要额外的转换逻辑电路,因此这种编码会增加芯片面积、功耗和信号延迟时间,这也是它的缺点。

Quasi-Gray编码器

此编码器克服Gray编码器需要额外的转换逻辑的特点,从而节省功耗和面积,并使信号延迟缩短,提高工作效率。其编码器构成如下

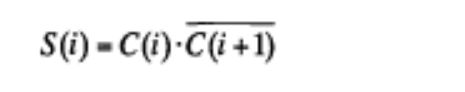

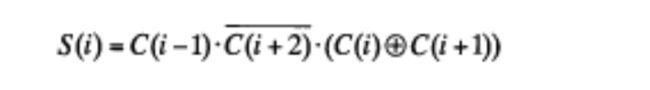

编码逻辑为:

编码逻辑为:

其中Bi为第i位二进制输出码,Ci为第i位Quasi-Gray输出码,M是指最高位MSB

邻码矫正逻辑

由分析可知,Gray编码器和Quasi-Gray编码器能抑制火花码的情况下的误码态。虽然绝大多数误码都发生在输入信号和参考信号非常接近处(即0-1转换点附近),Gray编码器和Quasi-Gray编码器可将这种误码影响限制在1lSB左右**,但如果某个比较器或锁存器由于噪声或者Stick-on故障呈现随机误码,而且该误码原理正常0-1转换点,那么Gray编码器和Quasi-Gray编码器将出现大的误码输出。**

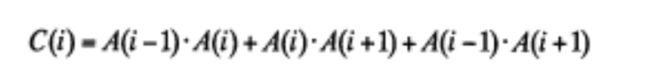

邻码校正逻辑是通过采用对各个比较器输出和其相邻的2个比较器输出进行校正,并校正出现的误码。检验是通过投票的方式来进行,即三个相邻码如果多数为1态,则中间码被赋值为1,否则就被赋值为0.

第i位的判断和赋值逻辑如下:

对误码进行校正后,就可以进行0-1转换点的判定,选择ROM编码的字线信号,得到对应的二进制编码。

对误码进行校正后,就可以进行0-1转换点的判定,选择ROM编码的字线信号,得到对应的二进制编码。

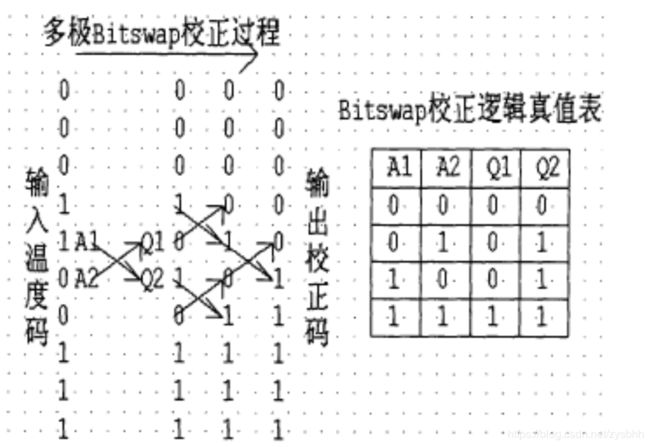

Bitswap校正逻辑

是利用温度码0和1顺序固定的特点,将误码出现处的2个相邻码进行互相交换,实现逐级校正。Bitswap校正逻辑可以通过串联方式实现完全的误码校正。

当Bitswap校正逻辑对比比较器阵列中出现原理0-1转换点的误码进行校正时,需要多个Bitswap校正逻辑进行串连,逐级进行校正,代价较高。

因此对于偶然出现的单个误码态进行校正时,BItswap校正逻辑不如邻码校正逻辑效率高。此外,由Bitswap实现原理可知,这种校正方法只适用于flash ADC中比较器阵列输出的温度码,而无法直接校正这些ADC中比较器阵列输出的循环温度码。

动态编码器

前述各种误码校正电路都是和相应编码逻辑配合使用的。通过分析可知目前常用的各种编码器各具特色和优点,然而存在一些问题,如适用范围不广、误码态校正不完全。特别是目前所用的编码电路多数不能直接用于折叠ADC所需的循环温度码的编码,必须增加额外电路进行判断,从而增加了电路面积、功耗和信号延迟时间。

本设计基于动态电路提出一种新型的温度码和循环温度码到二进制的动态编码电路,这种动态编码电路不需要字线选择和ROM编码,且易于和各种误码校正逻辑配合使用,具有速度快、面积小、功耗低等优点。同时通过所给的编码压缩方法可使这种动态编码电路的适用范围拓展到8-12bit分辨率的并行CMOS ADC,并避免采用普通逻辑电路,ROM单元或PLA等进行编码时电路复杂性会随分辨率上升而增大过快造成的电路延迟增加、功耗上升、噪声容限下降等诸多不利影响。

循环温度码

循环温度码在相同位数时,所含的信息量比温度码要多一倍,因此采用循环温度码可以减少硬件资源开销。

压缩编码

先对比较器阵列输出的温度码进行压缩,再进行编码。

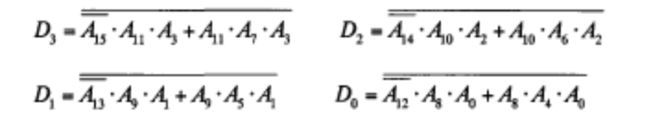

可采用4倍压缩,例如转换逻辑

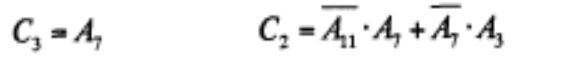

对应二进制的高2位的判断逻辑如下

对应二进制的高2位的判断逻辑如下

二进制码低2位C1、C0由压缩码编码后获得。

二进制码低2位C1、C0由压缩码编码后获得。

通过先采用合适的压缩率进行压缩,再进行循环温度码转换,然后使用动态编码电路,可设计8bit以上的flash型ADC的编码电路。对更高分辨率的 flash型ADC电路,如果压缩逻辑过于复杂,可以分两次进行压缩,再进行编码。

而对于折叠内插型ADC,由于预处理电路本身已经对输入信号进行折叠处理,因此比较器数目不会非常多,至多使用一次压缩就足以完成编码操作。

通过使用压缩编码,可进行32bit以上的温度码和循环温度码的编码,随着温度码和循环温度码位数的指数增长,这种动态编码电路的功耗和面积增加非常缓慢且速度基本不受影响,而常见的 ROM、PLA等编码电路功耗和面积均随之指数上升。