Vivado 实现逆序ip核,AXI4-Lite Interface(vcu118,HLS级开发)

实验环境

1、软件:Vivado HLS 2017.04,Vivado 2017.04,Vivado SDK2017.04

2、硬件:Xilinx Virtex UltraScale+ FPGA VCU118

本人是XILINX开发套件的菜鸟一枚。实验室买了块Xilinx Virtex UltraScale+ FPGA VCU118,后期也会不定期更新自己做的实验,希望对入门的有帮助,也可以一起交流学习(1987212851没事别打扰,忙着学习呢)。

Vivado HLS

1、打开vivado HLS 软件,创建相关的项目(此处省略,HLS如何创建一个项目可以参考 ug871。输入项目名和路径,一直点击Next,到选择开发板,然后点击Finish,完成项目的创建。

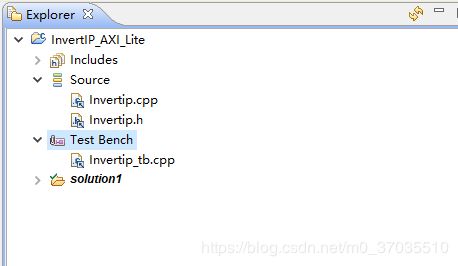

2、在你创建项目的目录创建三个文件,Invertip.cpp,用于写你的ip核内容,Invertip.h,头函数,Invertip_tb.cpp,验证函数,然后添加到你的项目中。

右击Source,然后点击Add Files,这里选择Invertip.cpp,Invertip.h两个文件,同样的右击Test Beach,然后添加Invertip_tb.cpp。(文件是没有内容的,需要自己书写。)

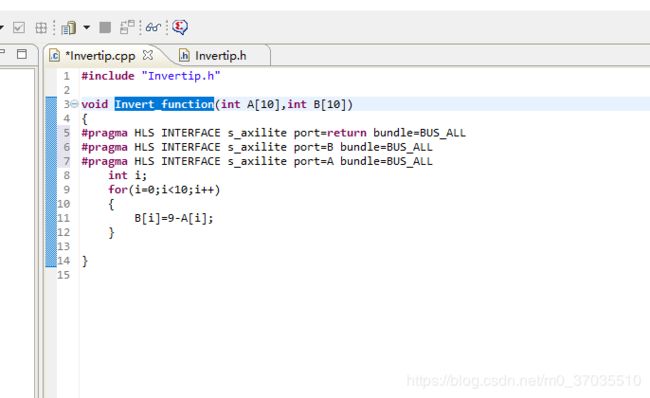

3、在三个文件上写上函数如下:

Invertip.cpp:

#include "Invertip.h"

void Invert_function(int A[10],int B[10])

{

int i;

for(i=0;i<10;i++)

{

B[i]=9-A[i];

}

}

Invertip.h:

#include <stdio.h>

#include "ap_int.h"

void Invert_function();

Invertip_tb.cpp:

#include "Invertip.h"

void Invert_function(int A[10],int B[10]);

int main()

{

int A[10];

int B[10];

int C[10];

int i;

for(i=0;i<10;i++)

{

A[i]=i;

}

Invert_function(A,B);

for(i=0;i<10;i++)

{

C[i]=A[9-i];

}

for (i=0;i<10;i++)

{

if(B[i]!=C[i])

{

printf("ERROR: HW and SW results mismatch\n");

return 1;

}

printf("Success: HW and SW results match\n");

return 0;

}

}

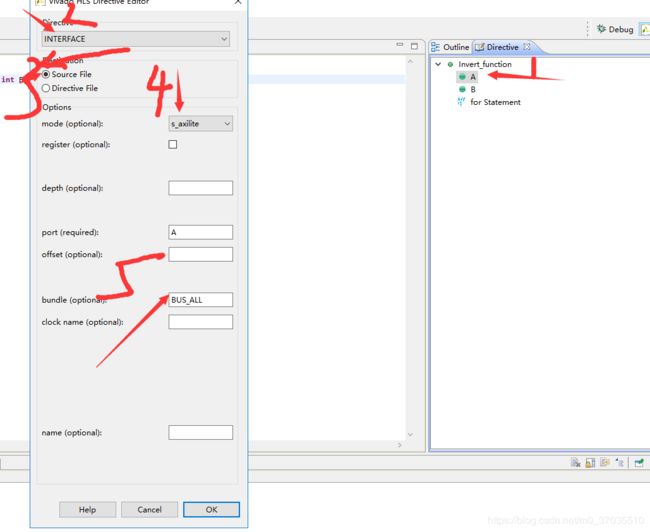

4、插入优化指令,并且使用AXI4-Lite4 Interface。

同理对B和invert_function,进行这样的操作,得到如下的Invertip.cpp(不懂这个操作的看ug902,p112,AXI4-Lite Interface):

然后进行从左向右依次进行仿真,综合,协同仿真,导出ip核(不懂操作的看ug 871),完成ip核的制作。接下来就是vivado中使用,和sdk中编程。

Vivado

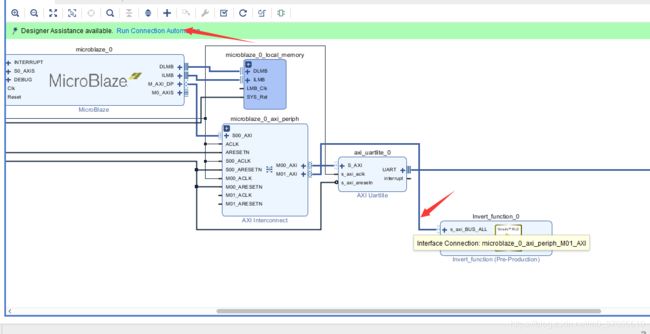

1、参考我这个博客创建一个模板的电路图,(原文:https://blog.csdn.net/m0_37035510/article/details/89325860 ),然后删除GPIO ip核,留着UART。

2、添加HLS制作的ip核。第四步,找到刚刚自己HLS中的路径,然后找到impl中的ip,加入即可。点击添加ip核,然后就可以看见我们做的ip核了。

链接红色箭头所指的那根线,然后点击自动连接,完成电路图绘制。然后导到sdk,进行编程。参考上个教程。

Vivado SDK

1、跟上个教程一样使用了模板,然后在testperiph.c添加代码,如下:(具体什么意思,可以看ug902,p113,然后就是看下C Driver Files,文档上都有。)

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xinvert_function.h"

XInvert_function HlsExample;

XInvert_function_Config *ExamplePtr;

int main()

{

init_platform();

int outdata[10];

int indata[10];

int m;

for(m=0;m<10;m++)

{

indata[m]=m;

}

ExamplePtr=XInvert_function_LookupConfig(XPAR_INVERT_FUNCTION_0_DEVICE_ID);

if (!ExamplePtr)

{

print("ERROR: Lookup of accelerator configuration failed.\n\r");

return XST_FAILURE;

}

int status = XInvert_function_CfgInitialize(&HlsExample, ExamplePtr);

if (status != XST_SUCCESS)

{

print("ERROR: Could not initialize accelerator.\n\r");

exit(-1);

}

XInvert_function_Start(&HlsExample);

for(m=0;m<10;m++)

{

XInvert_function_Write_A_Words(&HlsExample,0,indata,10);

}

for(m=0;m<10;m++)

{

XInvert_function_Read_B_Words(&HlsExample,0,outdata,10);

xil_printf("%d",outdata[m]);

}

print("Hello World\n\r");

cleanup_platform();

return 0;

}

2、调试串口,打印下,就可以看见逆序出现9,8,……,2,1,0。

3、具体实验代码。大家可以花5积分下载下,就算支持下吧,花了一上午写的,后期后更新实验,流接口,ELM。谢谢大家啦:https://download.csdn.net/download/m0_37035510/11217900

(有什么问题留言,或者加QQ:1987212851(欧阳))