4412 u-boot详细启动流程

u-boot启动

1. start.S

1.1 u-boot 入口 函数 _start

设置异常向量表, 跳转到reset函数

58 _start: b reset

59 ldr pc, _undefined_instruction

60 ldr pc, _software_interrupt

61 ldr pc, _prefetch_abort

62 ldr pc, _data_abort

63 ldr pc, _not_used

64 ldr pc, _irq

65 ldr pc, _fiq

1.2 reset

1.2.1 设置cpu模式SVC32 禁止IRQ & FIQ

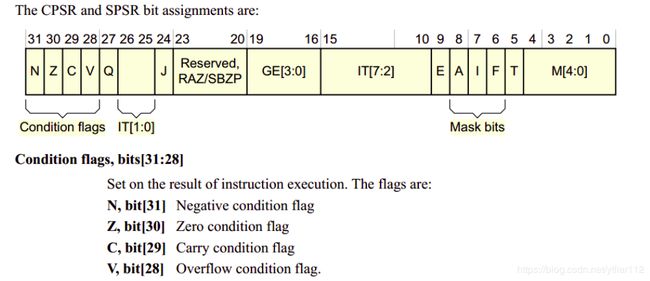

CPSR是ARM体系结构中的程序状态寄存器,其结构如下:

模式

| M[4:0] | 处理器模式 | 可访问的寄存器 |

| ------- | ---------- | ----------------------------------------- |

| ob10000 | user | pc,r14~r0,CPSR |

| 0b10001 | FIQ | PC,R14_FIQ-R8_FIQ,R7~R0,CPSR,SPSR_FIQ |

| 0b10010 | IRQ | PC,R14_IRQ-R13_IRQ,R12~R0,CPSR,SPSR_IRQ |

| 0B10011 | SUPERVISOR | PC,R14_SVC-R13_SVC,R12~R0,CPSR,SPSR_SVC |

| 0b10111 | ABORT | PC,R14_ABT-R13_ABT,R12~R0,CPSR,SPSR_ABT |

| 0b11011 | UNDEFINEED | PC,R14_UND-R8_UND,R12~R0,CPSR,SPSR_UND |

| 0b11111 | SYSTEM | PC,R14-R0,CPSR(ARM V4以及更高版本) |

mask bit

| 1 | 0 | 描述 | |

|---|---|---|---|

| T | Thumb | arm | 工作状态 |

| F | 禁止 | 使能 | FIQ |

| I | 禁止 | 使能 | IRQ |

至于usr模式,由于此模式无法直接访问很多的硬件资源,而uboot初始化,就必须要去访问这类资源,所以此处可以排除,不能设置为用户usr模式,而

svc模式本身就属于特权模式,本身就可以访问那些受控资源,而且,比sys模式还多了些自己模式下的影子寄存器,所以,相对sys模式来说

194 mrs r0, cpsr

195 bic r0, r0, #0x1f

196 orr r0, r0, #0xd3

197 msr cpsr,r0

1.2.2 cache_init

202 mrc p15, 0, r0, c0, c0, 0 @ read main ID register

203 and r1, r0, #0x00f00000 @ variant

204 and r2, r0, #0x0000000f @ revision

205 orr r2, r2, r1, lsr #20-4 @ combine variant and revision

206 cmp r2, #0x30

207 mrceq p15, 0, r0, c1, c0, 1 @ read ACTLR

208 orreq r0, r0, #0x6 @ Enable DP1(2), DP2(1)

209 mcreq p15, 0, r0, c1, c0, 1 @ write ACTLR

210 /*

211 * Invalidate L1 I/D

212 */

213 mov r0, #0 @ set up for MCR

214 mcr p15, 0, r0, c8, c7, 0 @ invalidate TLBs

215 mcr p15, 0, r0, c7, c5, 0 @ invalidate icache

216

217 /*

218 * disable MMU stuff and caches

219 */

220 mrc p15, 0, r0, c1, c0, 0

221 bic r0, r0, #0x00002000 @ clear bits 13 (--V-)

222 bic r0, r0, #0x00000007 @ clear bits 2:0 (-CAM)

223 orr r0, r0, #0x00001000 @ set bit 12 (---I) Icache

224 orr r0, r0, #0x00000002 @ set bit 1 (--A-) Align

225 orr r0, r0, #0x00000800 @ set bit 11 (Z---) BTB

226 mcr p15, 0, r0, c1, c0, 0

1.2.3 获取启动信息

4412 Power Management Unit 操作状态有两种

Local power control

System-level power control 包含5种方式

252 ldr r0, =POWER_BASE //0x10020000

253 ldr r1, [r0,#OMR_OFFSET]

254 bic r2, r1, #0xffffffc1

297 ldr r0, =INF_REG_BASE

298 str r3, [r0, #INF_REG3_OFFSET]

启动信息

| OM[5:1] | 1st Device | 2nd Device |

|---|---|---|

| 5b’00 000x | Reserved | |

| 5b’00 001x | Reserved | |

| 5b’00 010x | SDMMC_CH2 | USB |

| 5b’00 011x | eMMC43_CH0 | USB |

| 5b’00 100x | eMMC44_CH4 | USB |

| 5b’00 101x to 5b’00 111x | Reserved | |

| 5b’01 000x | NAND_512_8ECC | USB |

| 5b’01 001x | NAND_2KB_OVER | USB |

| 5b’01 001x to 5b’01 111x | Reserved | |

| 5b’10 000x | Reserved | |

| 5b’10 001x | Reserved | |

| 5b’10 010x | Reserved | |

| 5b’10 011x | eMMC43_CH0 | SDMMC_CH2 |

| 5b’10 100x | eMMC44_CH4 | SDMMC_CH2 |

| 5b’10 101x to 5b’10 111x | Reserved | |

| 5b’11 000x | NAND_512_8ECC | SDMMC_CH2 |

| 5b’11 001x | NAND_2KB_OVER | SDMMC_CH2 |

| 5b’11 001x to 5b’11 111x | Reserved |

1.3 lowlevel_init

1.3.1 使用 iROM stack in bl2

| BaseAddr | Limit Addr | size | 描述 |

|---|---|---|---|

| 0x0000_0000 | 0x0001_0000 | 64k | iROM |

| 0x0000_0000 | 0x0001_0000 | 64 KB | iROM |

| 0x0200_0000 | 0x0201_0000 | 64 KB | iROM (mirror of 0x0 to 0x10000) |

| 0x0202_0000 | 0x0206_0000 | 256 KB | iRAM |

66 /* use iROM stack in bl2 */

67 ldr sp, =0x02060000

1.3.2 检查复位状态

71 /* check reset status */

72 ldr r0, =(INF_REG_BASE + INF_REG1_OFFSET) //0x10020800 + 0x4

73 ldr r1, [r0]

74

75 /* AFTR wakeup reset */

76 ldr r2, =S5P_CHECK_DIDLE //0xBAD00000

77 cmp r1, r2

78 beq exit_wakeup

79

80 /* Sleep wakeup reset */

81 ldr r2, =S5P_CHECK_SLEEP// 0xBAD00000

82 cmp r1, r2

83 beq wakeup_reset

1.3.3 PS-Hold high

85 /* PS-Hold high */

86 ldr r0, =0x1002330c

87 ldr r1, [r0]

88 orr r1, r1, #0x300

89 str r1, [r0]

90

91 ldr r0, =0x11000c08

92 ldr r1, =0x0

93 str r1, [r0]

95 /* Clear MASK_WDT_RESET_REQUEST */

96 ldr r0, =0x1002040c

97 ldr r1, =0x00

98 str r1, [r0]

后面再说