verilog编码器及七段译码器设计及仿真

题目要求:设计一个10输入编码器和一个七段译码器,要求使输入值在译码器显示

- 所需仪器:

- 步骤

- 代码

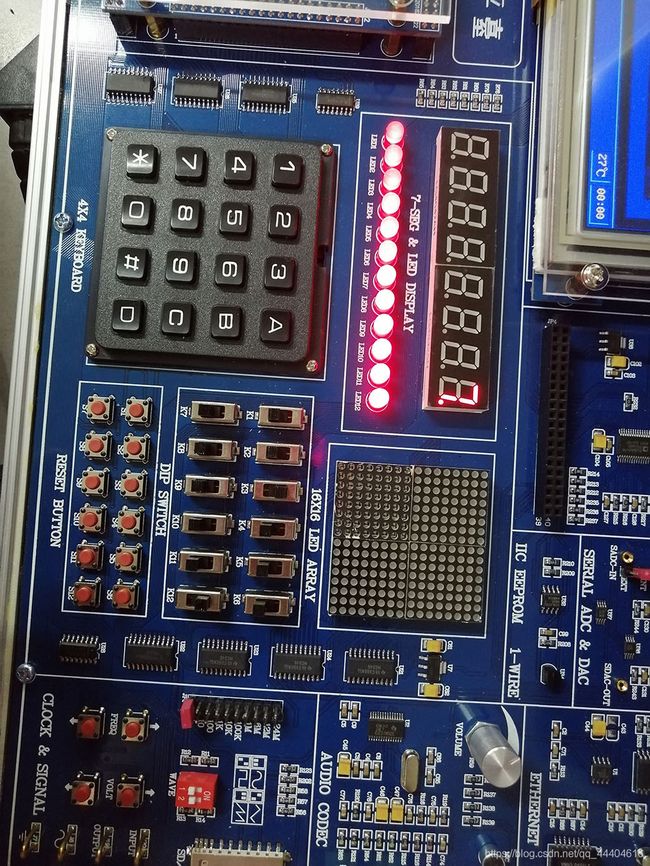

- 实验图

所需仪器:

软件:modelsim、quartus。

硬件:实验箱。

步骤

- 在modelsim中新建工程并添加Verilog文件后编写代码;

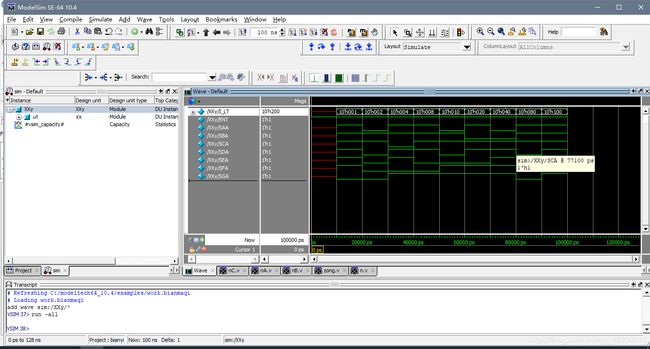

- 编译并仿真得到波形图;

- 在quarters中新建工程并将Verilog源文件添加进去,编译并运行;

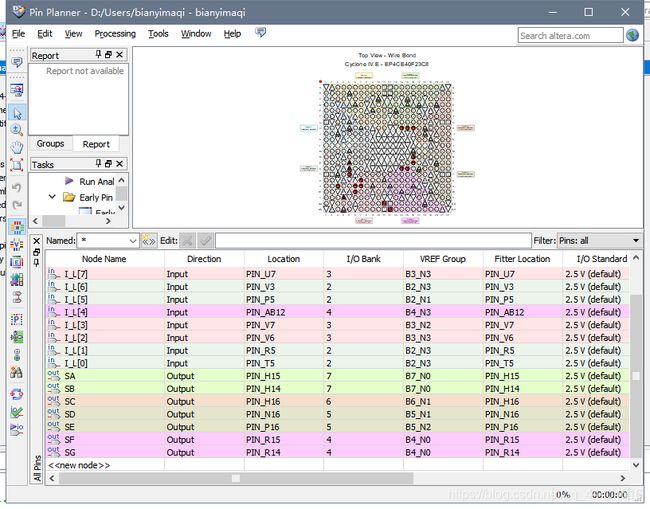

- 设置管脚并连接试验箱进行测试。

代码

** 10输入编码器**:

module bianmaqi(I_L,A_L);

input [9:0] I_L;

output [3:0] A_L;

reg [3:0] A_L;

integer j;

always @ (I_L or A_L)

begin

for(j=0;j<=9;j=j+1)

begin

if(I_L[j]==1)

A_L=j;

end

end

endmodule

七段译码器:

module Vrseg(A_L,EN,SA,SB,SC,SD,SE,SF,SG);

input EN;

input[3:0]A_L;

output SA,SB,SC,SD,SE,SF,SG;

reg SA,SB,SC,SD,SE,SF,SG;

reg [1:7]SS;

always@(A_L or EN)begin

if(EN)

case (A_L)

4'b0000:SS=7'b1111110;

4'b0001:SS=7'b0110000;

4'b0010:SS=7'b1101101;

4'b0011:SS=7'b1111001;

4'b0100:SS=7'b0110011;

4'b0101:SS=7'b1011011;

4'b0110:SS=7'b0011111;

4'b0111:SS=7'b1110000;

4'b1000:SS=7'b1111111;

4'b1001:SS=7'b1110011;

default SS=7'bx;

endcase

else SS=7'b0;

{SA,SB,SC,SD,SE,SF,SG}=SS;

end

endmodule

顶层模块:

module xx(I_L,EN,SA,SB,SC,SD,SE,SF,SG);

input [9:0]I_L;

input EN;

output SA,SB,SC,SD,SE,SF,SG;

wire [3:0] A_L;

Vrseg u1(A_L,EN,SA,SB,SC,SD,SE,SF,SG);

bianmaqi u2(I_L,A_L);

endmodule

测试代码

`timescale 1ns/100ps

`include

module XXy();

reg [9:0] I_LT;

reg ENT;

wire SAA,SBA,SCA,SDA,SEA,SFA,SGA;

xx ut(.I_L(I_LT),.EN(ENT),.SA(SAA),.SB(SBA),.SC(SCA),.SD(SDA),.SE(SEA),.SF(SFA),.SG(SGA));

initial begin

ENT=1;

#10

I_LT=10'b0000000001;

#10

I_LT=10'b0000000010;

#10

I_LT=10'b0000000100;

#10

I_LT=10'b0000001000;

#10

I_LT=10'b0000010000;

#10

I_LT=10'b0000100000;

#10

I_LT=10'b0001000000;

#10

I_LT=10'b0010000000;

#10

I_LT=10'b0100000000;

#10

I_LT=10'b1000000000;

end

endmodule