NOR Flash擦写和原理分析 (一)

1. NOR FLASH 的简单介绍

NOR FLASH 是很常见的一种存储芯片,数据掉电不会丢失.NOR FLASH支持Execute On Chip,即程序可以直接在FLASH片内执行(这意味着存储在NOR FLASH上的程序不需要复制到RAM就可以直接运行).这点和NAND FLASH不一样.因此,在嵌入式系统中,NOR FLASH很适合作为启动程序的存储介质.NOR FLASH的读取和RAM很类似(只要能够提供数据的地址,数据总线就能够正确的给出数据),但不可以直接进行写操作.对NOR FLASH的写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作.

从支持的最小访问单元来看,NOR FLASH一般分为 8 位的和16位的(当然,也有很多NOR FLASH芯片同时支持8位模式和是16 位模式,具体的工作模式通过特定的管脚进行选择).

对8位的 NOR FLASH芯片,或是工作在8-BIT模式的芯片来说,一个地址对应一个BYTE(8-BIT)的数据.例如一块8-BIT的NOR FLASH,假设容量为4个BYTE.那芯片应该有8个数据信号D7-D0 和2个地址信号,A1-A0.地址0x0对应第0个 BYTE,地址0x1对应于1BYTE,地址0x2对应于第2个BYTE,而地址0x3则对应于第3 个BYTE.对16位的 NOR FLASH芯片,或是工作在16-BIT模式的芯片来说,一个地址对应于一个HALF-WORD(16-BIT)的数据.例如,一块16-BIT的 NOR FLASH,假设其容量为4个BYTE.那芯片应该有16 个数据信号线D15-D0 和1个地址信号A0.地址 0x0对应于芯片内部的第0个HALF-WORD,地址0x1对应于芯片内部的第1个 HALF-WORD

FLASH一般都分为很多个SECTOR,每个SECTOR包括一定数量的存储单元.对有些大容量的FLASH,还分为不同的BANK,每个BANK包括一定数目的SECTOR.FLASH的擦除操作一般都是以SECTOR,BANK或是整片FLASH为单位的.

在对FLASH进行写操作的时候,每个BIT可以通过编程由1变为0,但不可以有0修改为1.为了保证写操作的正确性,在执行写操作前,都要执行擦除操作.擦除操作会把FLASH的一个SECTOR,一个BANK或是整片FLASH的值全修改为0xFF.这样,写操作就可以正确完成了.

由于NOR FLASH没有本地坏区管理,所以一旦存储区块发生毁损,软件或驱动程序必须接手这个问题,否则可能会导致设备发生异常. 在解锁、抹除或写入NOR FLASH区块时,特殊的指令会先写入已绘测的记忆区的第一页(Page).接着快闪记忆芯片会提供可用的指令清单给实体驱动程序,而这些指令是由一般性闪存接口(CommON FLASH memory Interface, CFI)所界定的. 与用于随机存取的ROM不同,NOR FLASH也可以用在存储设备上;不过与NAND FLASH相比,NOR FLASH的写入速度一般来说会慢很多.

小结:NOR FLASH类似于RAM,8位地址就是每个地址对应1个byte,16位地址就是每个地址对应2个byte,ARM的每个地址只对应1个byte

2.NOR Flash的读写方式

2.1 处理器寻址

ARM处理器中每个地址对应的是一个byte的数据单元,这和很多别的处理器是一样的。

2.2 CPU于NOR Flash的硬件连接

从前面的先容,我们知道从处理器的角度来看,每个地址对应的是一个 BYTE 的数据单元.而,NOR FLASH 的每个地址有可能对应的是一个BYTE的数据单元,也有可能对应的是一个HALF-WORD的数据单元.所以在硬件设计中,连接ARM处理器和 NOR FLASH时,必须根据实际情况对地址信号做特别的处理。

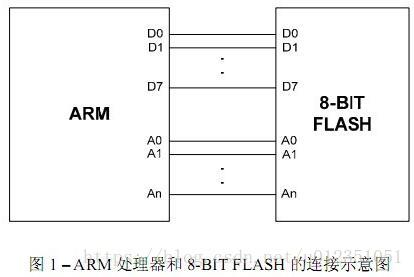

假如ARM处理器外部扩展的是8-BIT的NOR FLASH, 数据线和地址线的连接应该如图1所示. 从图中我们可以看到,处理器的数据信号D0-D7和 FLASH的数据信号D0-D7是逐一对应连接的,处理器的地址信号A0-An和NOR FLASH的地址信号A0-An 也是逐一对应连接的.如下图所示:

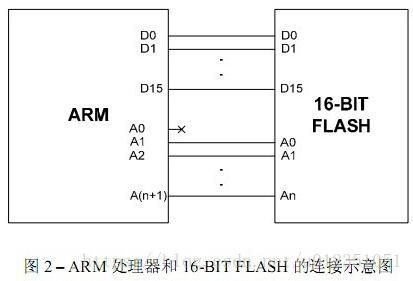

假如ARM处理器外部扩展的是16-BIT的NOR FLASH, 地址线必须要错位连接. 图2给了一个ARM处理器和16-BIT NOR FLASH的连接示意图.如图2所示,ARM处理器的数据信号D0-D15和FLASH 的数据信号D0-D15是逐一对应的.而ARM处理器的地址信号和NOR FLASH 的地址信号是错位连接的,ARM的A0悬空,ARM 的A1 连接FLASH 的A0,ARM 的A2连接FLASH的A1,依次类推.需要错位连接的原因是:ARM处理器的每个地址对应的是一个BYTE 的数据单元,而 16-BIT 的 FLASH 的每个地址对应的是一个HALF-WORD(16-BIT)的数据单元.为了保持匹配,所以必须错位连接.这样,从ARM处理器发送出来的地址信号的最低位A0对16-BIT FLASH来说就被屏蔽掉了.如下图所示:

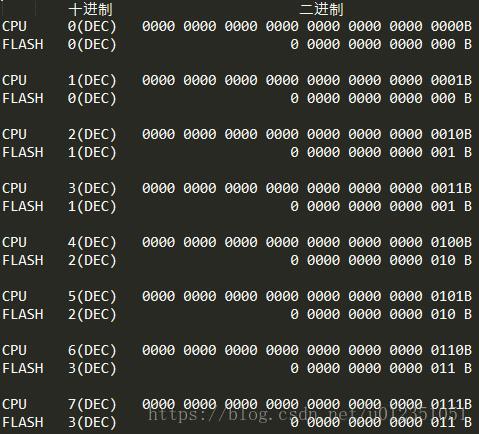

这里简单的总结:CPU发出地址对应1个字节,而16位flash的一个地址对应2个字节,所以需要错位,那么数据对应关系如下图所示:

从上可以看到,CPU读地址0和1对应的字节,flash返回的都是第1个字(相对于flash,地址为0)

CPU读地址2和3对应的字节,flash返回的都是第2个字(相对于flash,地址为1)

CPU读地址4和5对应的字节,flash返回的都是第3个字(相对于flash,地址为2)

这个逻辑竟然是对的,CPU要做的就是对读到的16bit字进行取高8位字节,还是低8位字节处理。

补充说明:

- 一般来说,ARM处理器内部要设置相应的寄存器,告诉处理器外部扩展的FLASH的位宽(8-BIT/16-BIT/32-BIT) .这样,处理器才知道在访问的时候如何从FLASH正确的读取数据;

- 有些ARM处理器内部可以设置地址的错位.对于支持软件选择地址错位的处理器,在连接16-BIT FLASH的时候,硬件上可以不需要把地址线错位.读者设计的时候,请参考MCU的数据手册,以手册为准,以免造成不必要的麻烦;

- 假如处理器支持内部设置地址错位,在实际访问的时候,送出的地址实际上是在MCU内部做了错位处理,其作用是等效于硬件连接上的错位的

2.3 从软件角度来看 ARM 处理器和 NOR FLASH 的连接

从软件的角度来理解ARM处理器和 FLASH的连接.对于8-BIT的FLASH的连接,很好理解,由于ARM处理器和8-BIT FLASH的每个地址对应的都是一个 BYTE 的数据单元.所以地址连接毫无疑问是逐一对应的.假如 ARM 处理器连接的是 16-BIT 的处理器,由于 ARM 处理器的每个地址对应的是一个 BYTE 的数据单元,而 16-BIT FLASH 的每个地址对应的是一个 HALF-WORD 的16-BIT的数据单元.所以,也毫无疑问,ARM处理器访问16-BIT处理器的时候,地址肯定是要错开一位的.在写FLASH驱动的时候,我们不需要知道地址错位是由硬件实现的,还是是通过设置ARM处理器内部的寄存器来实现的,只需要记住2点:

- ARM处理器访问8-BIT FLASH的时候,地址是逐一对应的;

- ARM处理器访问16-BIT FLASH的时候,地址肯定是错1位的.