使用Verilog实现FPGA偶数/奇数分频电路设计并使用modelsim仿真

本人地大14级师兄,如果有学弟学妹搜到这个评论一个呗!

一、设计要求

编写VerilogHDL程序,实现如下功能:

输入时钟信号和复位/信号,实现4分频/5分频,占空比为1:1.

二、设计思路

1.偶数分频

假设为N分频,计数到N/2-1时,时钟翻转、计数清零,如此循环就可以得到N(偶)分频

2.奇数分频(占空比为50%)

(1)假设为N分频,取一个进行上升沿触发的模N计数,触发时钟翻转后,经过(N-1)/2再次进行翻转,得到一个占空比非50%奇数N频时钟。再取一个同时进行下降沿触发的模N计数,触发时钟翻转后,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数N分频时钟。两个时钟进行相或运算,得到占空比为50%的奇数n分频时钟。

(2)与(1)相似,取两个都是上升沿触发的模N计数,一个是(N-1)/2时翻转,另一个是(N+1)/2时翻转。两个时钟进行相或运算,得到占空比为50%的奇数n分频时钟。

(3)小数分频

本次使用思路(1)

三、Verilog代码及说明

1. 偶数分频

module FreqDivFour(CLK , CLK_Out, rst); //四分频,括号内只能是输入输出型

input CLK,rst;

output CLK_Out ;

reg[1:0] cnt;

reg CLK_Out ; //可为寄存器输出型

always@(posedge CLK or negedge rst)

begin

if(!rst) begin cnt<= 0; CLK_Out <= 0; end

else if(cnt == 1)

begin

CLK_Out<=~ CLK_Out; //时钟翻转

cnt<= 0; //计数清零

end

elsecnt <= cnt + 1;

end

endmodule

2. 奇数分频(占空比为50%)

module FreqDivFive(CLK , CLK_Out, rst); //五分频

input CLK,rst;

output CLK_Out ;

reg[2:0] cnt_One, cnt_Two;

reg CLK_One,CLK_Two;

always@(posedge CLK or negedge rst) //上升沿触发

begin

if(!rst) begin cnt_One <= 0; CLK_One <=0; end

else

begin

if(cnt_One== 4)

cnt_One<= 0; //计数清零

else

cnt_One<= cnt_One + 1;

if(cnt_One== 1)

CLK_One<=~ CLK_One; //时钟翻转

elseif(cnt_One == 3)

CLK_One<=~ CLK_One; //时钟翻转

end

end

always@(negedge CLK or negedge rst) //下降沿触发

begin

if(!rst) begin cnt_Two <= 0; CLK_Two <= 0; end

else

begin

if(cnt_Two== 4)

cnt_Two<= 0; //计数清零

else

cnt_Two<= cnt_Two + 1;

if(cnt_Two== 1)

CLK_Two<=~CLK_Two; //时钟翻转

elseif(cnt_Two == 3)

CLK_Two<=~CLK_Two; //时钟翻转

end

end

assign CLK_Out = CLK_One | CLK_Two; //两输出波形相或运算,assign只能是net型

endmodule

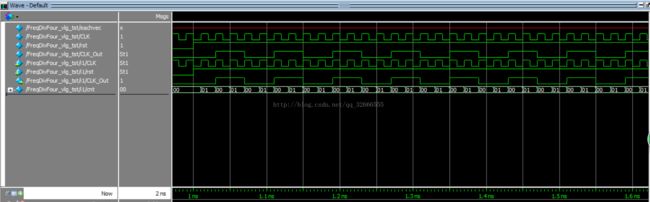

四、实验结果及分析

1.偶数分频

2.奇数分频(占空比为50%)

附件:modelsim测试代码

// Generated on "03/22/201721:49:38"

// Verilog Test Bench template for design :FreqDivFour

//

// Simulation tool : ModelSim-Altera (Verilog)

//

`timescale 1 ps/ 1 ps

module FreqDivFour_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg CLK;

reg rst;

// wires

wire CLK_Out;

// assign statements (if any)

FreqDivFour i1 (

// port map - connection between masterports and signals/registers

.CLK(CLK),

.CLK_Out(CLK_Out),

.rst(rst)

);

initial

begin

// code that executes only once

// insert code here --> begin

CLK= 0;

forever

#10CLK=~CLK;

// --> end

$display("Runningtestbench");

end

initial

begin

rst = 0;

#1000 rst=1;

#1000;

$stop;

end

always

// optional sensitivity list

// @(event1 or event2 or .... eventn)

begin

// code executes for every event on sensitivitylist

// insert code here --> begin

@eachvec;

// --> end

end

endmodule