带你了解TI的DSP入门芯片TMS320F28335

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:

TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。其主要性能如下:

高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;

高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;

6通道的DMA控制器;

片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;

控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;

8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。GPI00~GPI063连接到该中断。GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;

支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;

增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);

3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;

串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;

12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;

88个可编程的复用GPIO引脚;

低功耗模式;

1.9 V内核,3.3 V I/O供电;

符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:

片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

OTP ROM区(0x38 0000~0x38 03FF)为只读空间,存储A/D转换器的校准程序,用户不能对此空间写入程序。

即使不应用eCAN模块,也应使能时钟模块,将为eCAN分配的RAM空间用作一般RAM。

如果设置安全代码,存储器区域Ox33FF80~0x33FFF5需全部写入数据0x0000,而不能用于存储程序或数据。反之,0x33FF80~Ox33FEF可以存储数据或程序,其中0x33FFF0~Ox33FFF5只能存储数据。

仿真工具和开发环境:

TMS320F28335开发工具有:标准的优化C/C++编译/汇编/连接器,CCS集成开发环境,评估板和XDS510仿真器。其中CCS是一个界面友好,功能完善的集成的开发平台,具有编辑、汇编、编译、软硬件仿真调试功能。

TMS320F28335 的ADC:

TMS320F28335上有16通道、12位的模数转换器ADC。他可以被配置为两个独立的8通道输入模式,也可以通过配置AdcRegs.ADCTRL1.bit.SEQ_CASC=1,将其设置为一个16通道的级联输入模式。输入的方式可以通过配置 AdcRegs.ADCTRL1.bit.ACQ_PS=1,将其设置为顺序采集。即从低通道开始到高通道结束。 值得注意的是片上ADC的输入电压范围为0--3V,一旦超过3V,片上的ADC模块将会被烧掉。TI上的DATASHEET介绍其ADC的精度可达到12位,实际上达到不了。经测试,我们估计最好的时候可以达到11位就不错了。下面我们来简单介绍一下ADC模块的原理。其数字值由下面公司来计算,其中公式中的3为片内参考电压Digital Value=4096*(Input Analog Voltage-ADCLO)/3 ;(when 0 V 《 input 《 3 V)。ADC可以分为SEQ1和SEQ2两个模块,其中SEQ1包括ADCIN00--ADCIN07;SEQ2包括ADCIN08--ADCIN15。SEQ1模块可以通过软件、PWM、外部中断引脚来启动,而SEQ2不可以通过外部中断引脚来启动。另外就是ADC可以与DMA进行数据交换。

TMS320F28335 的时钟介绍:

TMS320F28335上有一个基于PLL电路的片上时钟模块,为CPU及外设提供时钟有两种方式:一种是用外部的时钟源,将其连接到X1引脚上或者XCLKIN引脚上,X2接地;另一种是使用振荡器产生时钟,用30MHz的晶体和两个20PF的电容组成的电路分别连接到X1和X2引脚上,XCLKIN引脚接地。我们常用第二种来产生时钟。此时钟将通过一个内部PLL锁相环电路,进行倍频。由于F28335的最大工作频率是150M,所以倍频值最大是5。其中倍频值由PLLCR的低四位和PLLSTS的第7、8位来决定。其详细的倍频值可以参照TMS320F28335的Datasheet。下面是F28335的时钟设置:

void InitPll(Uint16 val, Uint16 divsel)

{

// Make sure the PLL is not running in limp mode

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)

{

// Missing external clock has been detected

// Replace this line with a call to an appropriate

// SystemShutdown(); .

asm(“ ESTOP0”);

}

// DIVSEL MUST be 0 before PLLCR can be changed from

// 0x0000. It is set to 0 by an external reset XRSn

// This puts us in 1/4

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

EDIS;

}

// Change the PLLCR

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

// Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;

SysCtrlRegs.PLLCR.bit.DIV = val;

EDIS;

// Optional: Wait for PLL to lock.

// During this time the CPU will switch to OSCCLK/2 until

// the PLL is stable. Once the PLL is stable the CPU will

// switch to the new PLL value.

//

// This time-to-lock is monitored by a PLL lock counter.

//

// Code is not required to sit and wait for the PLL to lock.

// However, if the code does anything that is timing critical,

// and requires the correct clock be locked, then it is best to

// wait until this switching has completed.

// Wait for the PLL lock bit to be set.

// The watchdog should be disabled before this loop, or fed within

// the loop via ServiceDog()。

// Uncomment to disable the watchdog

DisableDog();

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)

{

// Uncomment to service the watchdog

// ServiceDog();

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;

EDIS;

}

// If switching to 1/2

if((divsel == 1)||(divsel == 2))

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

EDIS;

}

// If switching to 1/1

// * First go to 1/2 and let the power settle

// The time required will depend on the system, this is only an example

// * Then switch to 1/1

if(divsel == 3)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

DELAY_US(50L);

SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

EDIS;

}

}

TMS320F28335 的外部中断总结:

在这里我们要十分清楚DSP的中断系统。C28XX一共有16个中断源,其中有2个不可屏蔽的中断RESET和NMI、定时器1和定时器2分别使用中断13和14。这样还有12个中断都直接连接到外设中断扩展模块PIE上。说的简单一点就是PIE通过12根线与28335核的12个中断线相连。而PIE的另外一侧有12*8根线分别连接到外设,如AD、SPI、EXINT等等。这样PIE共管理12*8=96个外部中断。这12组大中断由28335核的中断寄存器IER来控制,即IER确定每个中断到底属于哪一组大中断(如IER |= M_INT12;说明我们要用第12组的中断,但是第12组里面的什么中断CPU并不知道需要再由PIEIER确定 )。接下来再由PIE模块中的寄存器PIEIER中的低8确定该中断是这一组的第几个中断,这些配置都要告诉CPU(我们不难想象到PIEIER共有12总即从PIEIER1-PIEIER12)。另外,PIE模块还有中断标志寄存器PIEIFR,同样它的低8位是来自外部中断的8个标志位,同样CPU的IFR寄存器是中断组的标志寄存器。由此看来,CPU的所有中断寄存器控制12组的中断,PIE的所有中断寄存器控制每组内8个的中断。除此之外,我们用到哪一个外部中断,相应的还有外部中断的寄存器,需要注意的就是外部中断的标志要自己通过软件来清零。而PIE和CPU的中断标志寄存器由硬件来清零。

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址

EDIS; // This is needed to disable write to EALLOW protected registers

PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE block使能PIE

PieCtrlRegs.PIEIER1.bit.INTx5= 1; //使能第一组中的中断5

IER |= M_INT1; // Enable CPU 第一组中断

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

也就是说,12组中的每个中断都要完成上面的相同配置,剩下的才是去配置自己的中断。如我们提到的EXINT,即外面来个低电平我们就进入

中断,完成我们的程序。在这里要介绍一下,DSP的GPIO口都可以配置为外部中断口,其配置方法如下:

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 0; //选择他们是GPIO口

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 0;

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0;

GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO54 = 0;//选择他们都是输入口

GpioCtrlRegs.GPBDIR.bit.GPIO55 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO56 = 0;

GpioCtrlRegs.GPBDIR.bit.GPIO57 = 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO54= 0;//GPIO时钟和系统时钟一样且支持GPIO

GpioCtrlRegs.GPBQSEL2.bit.GPIO55= 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO56= 0;

GpioCtrlRegs.GPBQSEL2.bit.GPIO57= 0;

GpioIntRegs.GPIOXINT3SEL.bit.GPIOSEL = 54;//中断3选择GPIO

GpioIntRegs.GPIOXINT4SEL.bit.GPIOSEL = 55;

GpioIntRegs.GPIOXINT5SEL.bit.GPIOSEL = 56;

GpioIntRegs.GPIOXINT6SEL.bit.GPIOSEL = 57;

XIntruptRegs.XINT3CR.bit.POLARITY= 0;//触发模式为下降沿触发

XIntruptRegs.XINT4CR.bit.POLARITY= 0;

XIntruptRegs.XINT5CR.bit.POLARITY= 0;

XIntruptRegs.XINT6CR.bit.POLARITY= 0;

XIntruptRegs.XINT3CR.bit.ENABLE = 1;//使能中断

XIntruptRegs.XINT4CR.bit.ENABLE = 1;

XIntruptRegs.XINT5CR.bit.ENABLE = 1;

XIntruptRegs.XINT6CR.bit.ENABLE = 1;

注意一点就是外部中断1和2只能对GPIO0—GPIO31配置;外部中断3和4、5、6、7只对GPIO32—GPIO63配置。

基于TMS320F28335信号处理板的设计与实现

硬件系统设计

1.1 方案概述

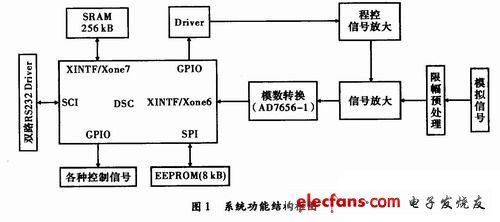

该系统主要功能是DSC通过ADC采样芯片对12路模拟信号进行同时采样。在DSC中进行数据处理后通过异步串行收发器上传到上位机。同时,上位机也可以通过异步收发器向DSC发送预先制定的命令,来控制信号处理板的工作模式和状态。

按照功能要求,整个硬件电路可分为3部分:电源模块、数字部分和模拟部分。其功能结构框图如图1所示。

1.2 电源模块设计

整个处理板的外部输入电压为5 V和±12 V,分别通过对应的电压转换芯片为模拟和数字部分提供不同的电压幅值。对于数字部分,电源模块需要为DSC提供1.9 V的核电压,同时为DSC的外围和其他芯片提供3.3 V的外围电压。本系统选用LT1963AES8集成芯片提供1.9 V,LT1963AEST-3.3集成芯片提供3.3 V。对于模拟部分,系统要求输入ADC的信号幅值范围在±12V内,所以系统分别选用LT1086IT-12和LT11 75IT把输入的±15V电压转换成±12V。

1.3 数字电路设计

数字部分电路主要是以DSC为中心的应用电路。该部分主要是对ADC传送的数据进行处理、存储,同时完成DSC同上位机的通信和数据传输。由图1可以看到,它包含以下几个部分。外围SRAM扩展,EEPROM扩展电路,SCI上位机通信接口电路。

1.3.1 外围SRAM扩展

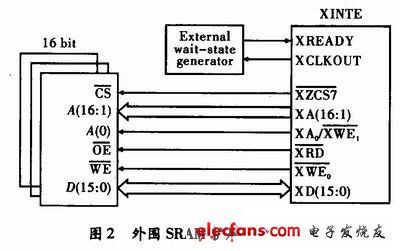

考虑到TMS320F28335片内的RAM资源有限,加上程序空间和数据空间RAM仅为34 kB,16位数据宽度,从而需要对片内的RAM进行扩展,来满足较大量程序的运行。本系统选用Cypress公司的CY7C1011CV33-12ZSXE集成芯片,利用TMS320F28335提供的XINTF接口完成片外RAM的扩展。

XINTF是TMS320F28335所提供的一个非复用异步总线,用来完成外部异步器件的扩展。XINTF可以映射外设到3个固定的内存映射区域,当外部资源挂接到某个区域时,则需要通过XINTF的一个片选信号来进行外部资源的选定。

CY7C1011CV33-12ZSXE是一个CMOS的静态RAM存储器,其容量大小为64 kB,16位数据宽度。图2是外围SRAM扩展电路连接图。

如图2所示,本系统选用ZONE7区域作为RAM的外围扩展。DSC通过其XZCS7管脚向片外SRAM发送片选信号。WE信号用来控制DSC对片外SRAM的读写,当DSC的XWEo管脚为低电平,则DSC对片外RAM进行读写操作;XWEo为高电平,同时DSC的XRD管脚为低电平,则为读操作。

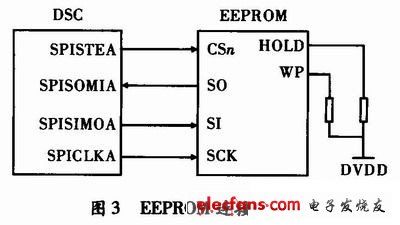

1.3.2 EEPROM扩展

考虑到系统在加电后,需要对一些设备的状态进行一些初始化,而这些初始化的数据在设备运转时又需要不断改变。因此,在设备运转过程中,实时将数据加以保存,以至于设备断电后数据依旧存在。本系统利用TMS320F28335的SPI接口外扩了一个EEPROM保存设备运转时实时获取的初始化数据。本系统选用Atmel公司的AT25160集成芯片。该芯片的容量为2 kB,其宽度为8位数据宽度。模块电路如图3所示。

如图3所示,DSC通过SPISTEA管脚发送片选信号选中EEPROM,通过SPICLKA管脚发送SPI传输时钟,而数据的写入和读出则分别通过SPIS-IMOA和SPISOMIA管脚完成。EEPROM中的HOLD管脚用来暂停与主设备间串行数据传输,WP管脚则用来进行对EEPROM的写保护,如果其为低电平,则主机无法向其写人数据。系统对两管脚输入高电平,保证EEPROM在读写操作过程中一直可以进行而不被中断。

1.3.3 SCI上位机通信接口

为了实现上位机同DSC异步的通信和数据传输,本系统利用TMS320F28335所提供的SCI接口来完成所需要求。SCI是一个2线的异步串行端口,即常说的UART。其数据的收发支持全双工通信,内部收发均有一个16级的FIFO来缓存数据。为了保证数据可靠,SCI提供奇偶校验,数据溢出检测等操作。SCI接口输出信号的电平是LV—TTL电气标准,通过RS232收发转换器加以驱动,获得RS232电气标准的信号,以便上位机接收。

1.4 模拟电路设计

模拟部分电路主要是以ADC为中心的应用电路。其主要实现模拟信号的处理,采集等工作。其中核心部分为AD转换。

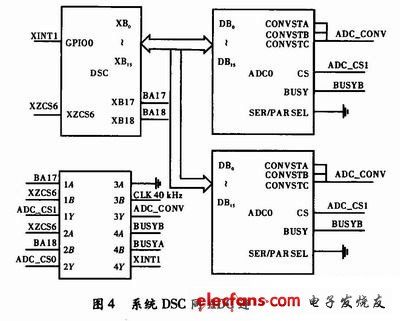

AD转换部分,主要是通过数字采样来完成模拟信号到数字信号的转变。本系统选用的ADC芯片是美国模拟电气公司的AD7656。模数转换芯片AD7656是高集成度、6通道6 bit逐次逼近(SAR)型ADC,内含1个2.5 V基准电压和基准缓冲器。该器件的功耗比最接近的同类双极性ADC降低了60%。AD7656在每通道250kb·s-1采样速率下的精度是同类产品的两倍。可以由引脚和软件选择模拟电压范围:10 V或5 V;模拟电源电压范围为4.75~5.25 V,因而大范围的工作电压使其无需电平转换等其他措施便可以直接与DSC相连;提供有并行和串行接口。可以工作在-40~85℃。标准模式5 V供电,250 kb·s-1时的功耗为140 mW,待机时仅为100μW。基于iCOMS技术制造的AD7656可以满足工业领域对分辨率、多通道、转换速率和功耗等方面的较高要求。

AD7656支持和DSC的并口、串口数据传输,通过SER/PAR SEL管脚的高低电平的选择,来控制采样后数字信号的传输方式。当其为高电平,则使用串行传输方式,反之则使用并行传输方式。本系统选用并行传输方式。在具体的转换过程中,每片AD7656内部的6条采样通路可以分为A、B、C共3组,其中每组通路包含2路通路。3组通路可以同时采样,也可以单独采样,而每组内的两条通路同时采样。管脚CONVSTA,CONVSTB,CONVSTC分别用来对A、B、C采样通路进行控制。当一个上升沿电平到达任一管脚,则该管脚对应模数转换的2路通路被启动,开始完成模数转换。当把三管脚连接,3组采样通路,即所有的6条采样通路同时采样。系统选用3组通路同时采样。

当DSC连接有多片ADC时,则需要通过CS片选管脚来进行ADC的选择。当采样开始,BUSY管脚将从低电平变为高电平,在整个采样的过程中,BUSY一直保持高电平,当采样结束,BUSY则从高电平变为低电平,此时DSC就可以开始读取数据。本系统则利用该管脚作为DSC外部中断源的输入管脚。当BUSY上电平由高变低,则通知DSC产生中断,来进行数据的读取。

本系统选用2片AD7656完成12路数据采样,通过DSC的XINTF ZONE6把ADC设备映射到DSC上,进行数据传输。通过地址译码和逻辑控制实现2片ADC同DSC的连接。具体结构如图4所示。

图4中左下角为逻辑部分,通过DSC的地址线BA17和BA18完成对ADC的选择。可以得到ADC0和ADC1在DSC中的地址映射为0x180000和0x1400 00。而外部输入40 kHz的时钟,作为ADC的采样频率。两个ADC对应DSC的同一个中断,当任意一片ADC采样完毕,都会引起DSC的中断,从而进行采样数据的读取。

2.系统软件设计

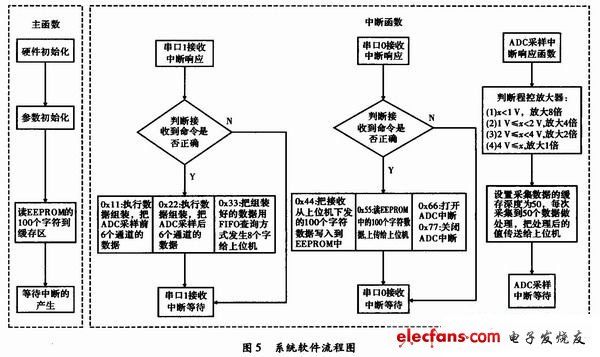

如前所述,整个信号处理板一共有12路模拟信号通路,通过传感器接收到12路模拟信号。2片AD7656把12路模拟信号转换为数字信号传送给TMS320F28335,在TMS320F28335中对这些采集到的数据做相应处理后通过SCI传送给上位机。同时对有必要保存的数据通过SPI接口保存到EEPROM中。整个采集、通信过程由上位机发送相关的命令来加以控制。程序的流程如图5所示。

在主函数中,程序首先完成相应模块的初始化,设定好CPU运行的时钟,选定好各个模块的工作模式,然后读取EEPROM中的设备初始化数据,后进行入等待状态。此时CPU等待ADC采样的数据,当ADC采样过程结束,则进入ADC中断响应函数,在此函数中,主要完成数据的读取,对于小信号,通过程控放大器放大其幅值,然后存储到自定义的缓存区中。两个串口工作方式均由上位机发送命令,从而触发SCI的串口收中断服务函数。然后在中断服务函数中完成对应命令要求。系统选用串口1完成采集数据向上位机的传输,串口0完成向EEPROM发送需保存的数据和一些相关操作。而SCI0和SCI1分别对应DSC外设中断的INT9.1和INT9.3,外部中断XINT1对应INT1.4。程序设置两个串口的传输速率均为38.4 kb·s-1。

在设备工作时,由于SCI1的中断源是上位机的命令发送,系统规定上位机每20ms发送一个数据接受命令,因此SCI1的中断响应周期为td= 20 ms。而由于采样率为40 kHz,因此ADC的中断服务函数响应周期为0.025 ms。系统规定采集一组数据的个数为50,那么采集一组数据的时间即为tc=1.25 ms,所以在一次SCI1中断过程中,ADC会采集16组数据。考虑到串口传输的波特率为38.4kb·s-1,因此传送一个16位的数据时间为tt=0.417 ms。而一组数据采集时间加上串口数据传输的时间为tc+tt=1.667 ms《 4 结束语

所设计的信号处理板以TMS320F28335为核心处理器,利用AD7656完成模拟信号采样的功能硬件平台。TMS320F28335片内集成了丰富的外围资源,通过驱动软件的配置和硬件系统的设计,可以方便、高效地完成大量数字信号的处理和运算。AD7656的6路模拟信号采集和16位高精度的模拟信号采样,较好地完成了模拟信号的数字化转换,减少了模拟信号采样的失真。实验证明,信号处理板所采集到的数字信号的误差值约为1.37 mV,可达14位的采样精度。