高云1N1开发板高云gowin软件使用教程

国产FPGA是最近几年起来的产品,具有性价比高特点。高云FPGA,很多用户都用在LED,电机控制,PLC设备上。

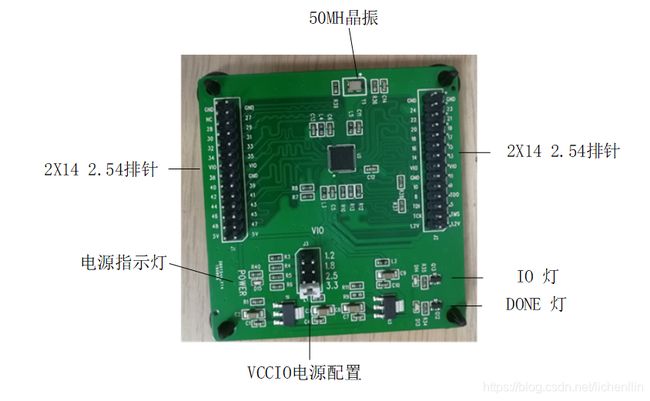

开发板子采用GW1N-LV1QN48C6/I5 FPGA器件。具有低功耗,瞬时启动,高安全性,低成本,方便扩展等特点。本开发板价格价格便宜,板子扩张性容易,帮助用户比较快递进入国产FPGA学习能力。

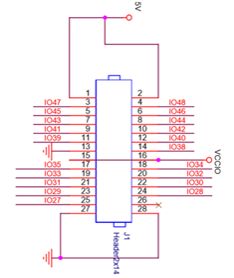

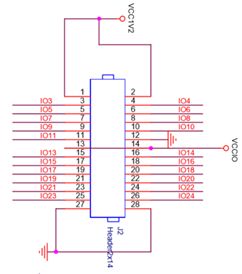

开发板集成多个GPIO接口和多个LVDS接口,电压可以从3.3,2.5,1.8,1.2V选择。用户可以选择不同电压适配不同的IO口。其中每个VCCIO也是独立供电,可以很简单改装成其他的不同bank不同电压要求。

芯片资源GW1N-1的资源有1K的LUT4,并且还有4个18K SRAM快,一个PLL锁相环。

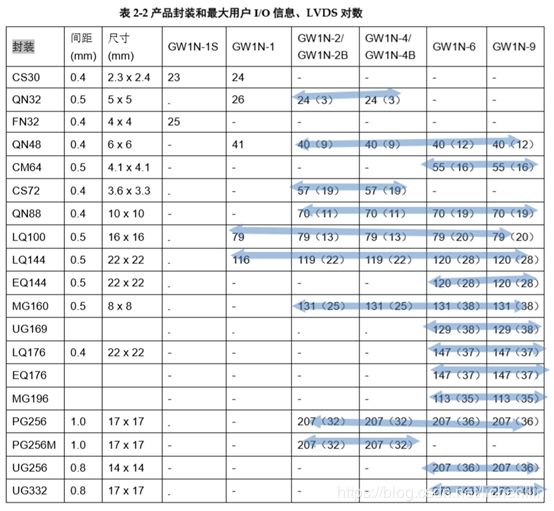

封装有最小的CS30的封装,也有QN32,QN48,LQ100,LQ144这类封装。灰色线代表是兼容封装。其实芯片同等封装都是类似的电源和地,IO管脚有差别。

板子上两排引脚名称都已经标记了锁定管脚的名称。用户很容易使用该平台。

2. 高云FPGA软件使用教程

高云设计软件在 http://cdn.gowinsemi.com.cn/Gowin_V1.9.1.01Beta_win.rar 直接复制就可以下载,关于license 可以在官网申请就可以,但是必须要有公司名称和电话号码。

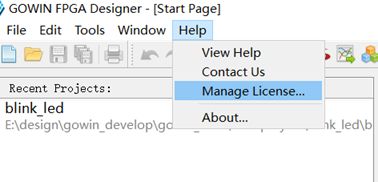

双击桌面的 图标进入软件,设定软件的license。 在help中选择mange license。

图标进入软件,设定软件的license。 在help中选择mange license。

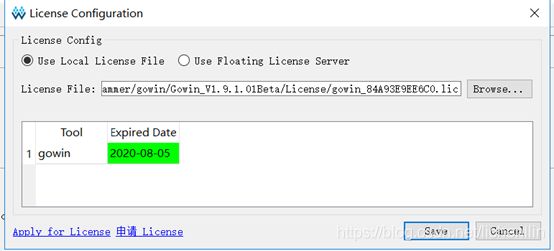

选择本地license文件。选择对应文件browse 选择文件。Save就可以保存设定。这个窗口还可以设定license文件,会跳到官方网站申请。

另外还得设定synplify软件路径。在个人用户变量的LM_LICENSE_FILE设定gowin的 synplify的 编译软件的license位置。

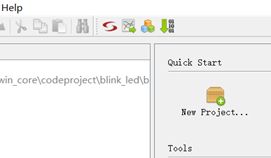

建立一个工程,选择FILE-NEW或者桌面quick start中new project

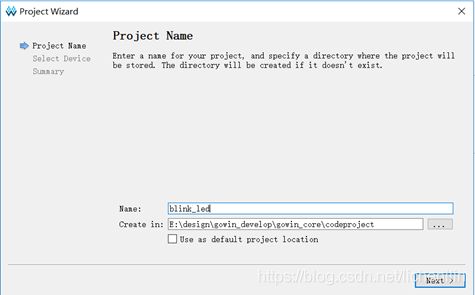

输入工程的名字和位置.

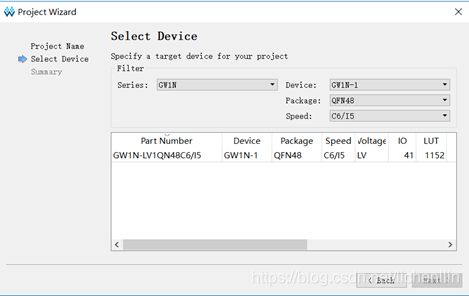

选择芯片类型GW1N系列,Device为GW1N-1,Package选择QFN48,SPEED选择C6/I5.

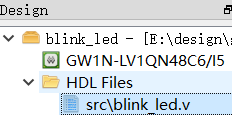

把blink-led文件复制到工程中src中.

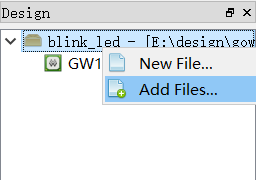

在design中增加文件.

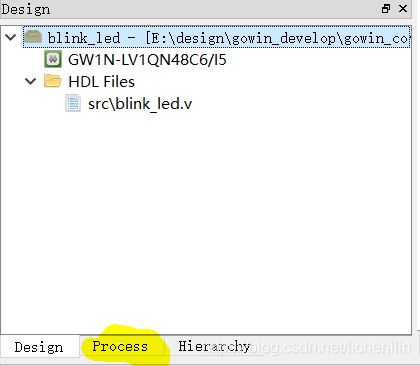

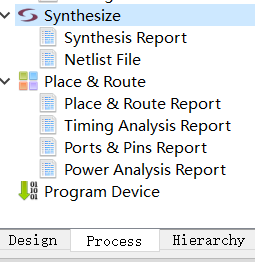

选择process选项卡

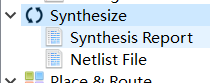

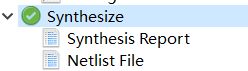

选择synthesize综合当前文件.

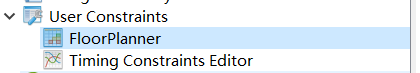

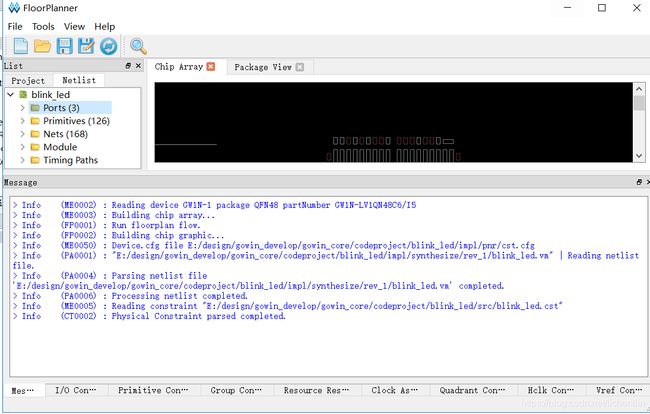

再双击user constraints,选择floorplanner.

在打开的floorplanner的窗口,可以看到ports名称,底部有几个选择项。

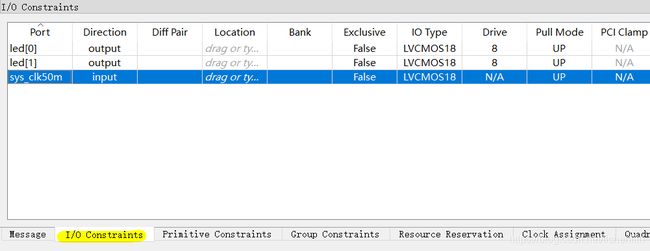

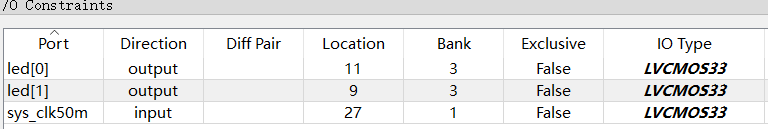

选择I/O Constraints设定管脚位置,电压。

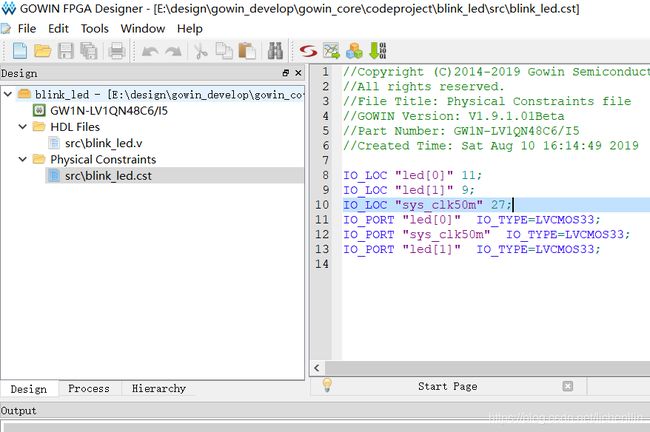

Led[0]设定在11,IO Type设定为lvcmos33,Led[1]设定在9,IO TYPE设定为LVCMOS33,sys-clk50m在27管脚,IO Type为LVCMOS33。

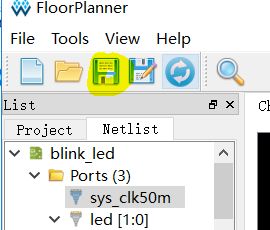

选择保存文件。关闭floorplanner软件。

在主程序中,选择design,看到有一个cst文件就是管脚约束文件,设定IO和电压要求。

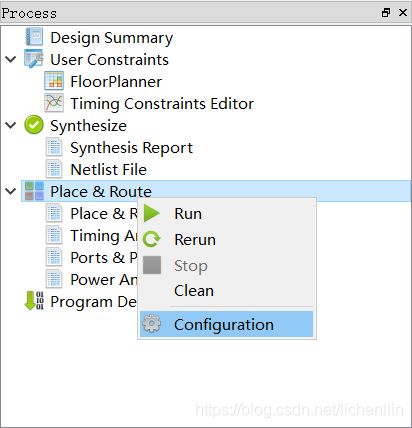

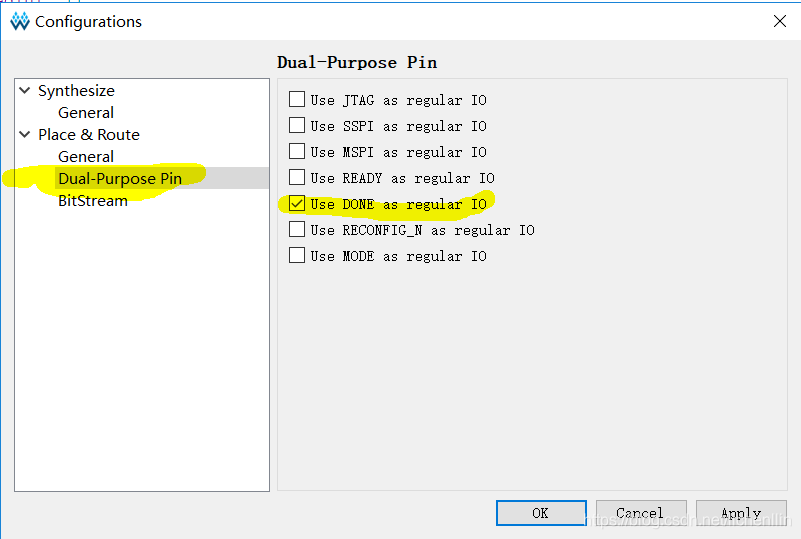

再次选择process,右键选择configuration。配置其中DONE管脚为普通IO管脚。

在配置窗口选择,DUAL-PUROSE pin 选择 USE DONE as regular IO,设定为普通的IO功能。

双击place&route 或者右键选择run。

完成布局布线操作以后,选择program device。

开发板上面下载线缆连接对应的管脚。

插入烧录器排线。USB电源暂时不插入。

接入5V OUT在5V引脚。

再接入JTAG的TDI,TDO,TCK,TMS以及GND。

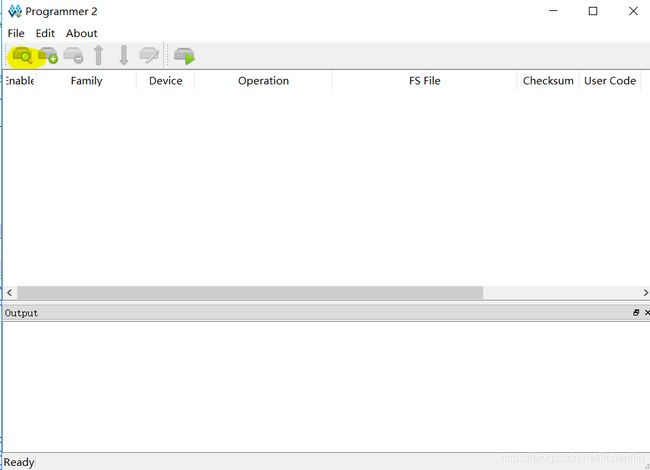

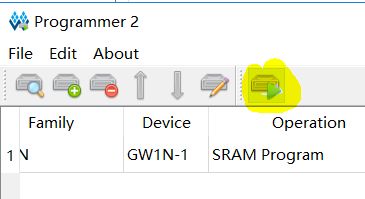

选择scan的按钮,找到芯片。

选择operation ,设定为SRAM Program。Filename选择impl/pnr/blink-led.fs文件,save保存

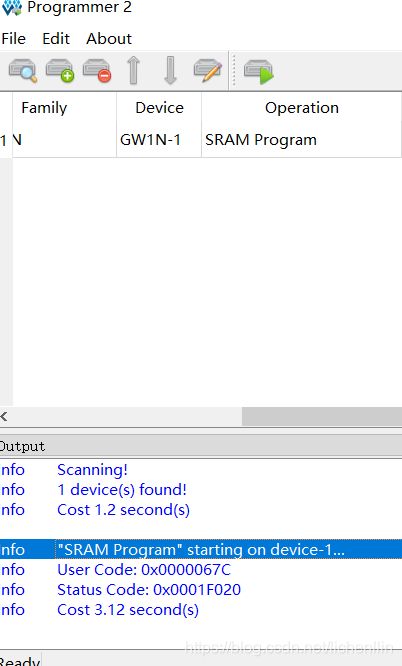

选择箭头,编程设备。

上述是SRAM烧录,这个烧录掉电以后是不会存在的。

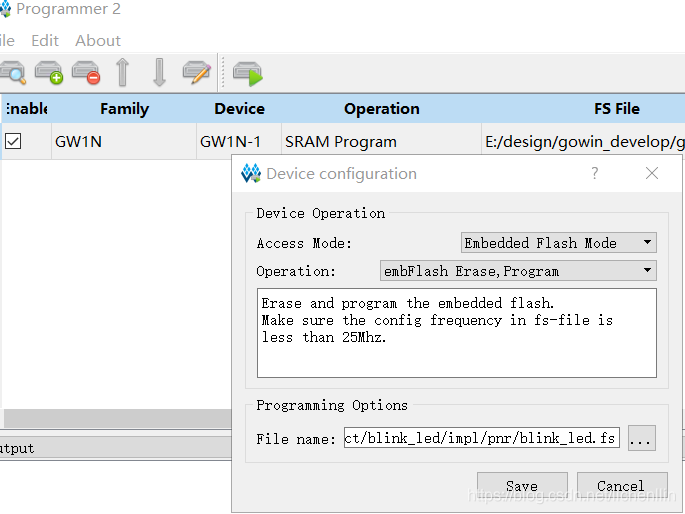

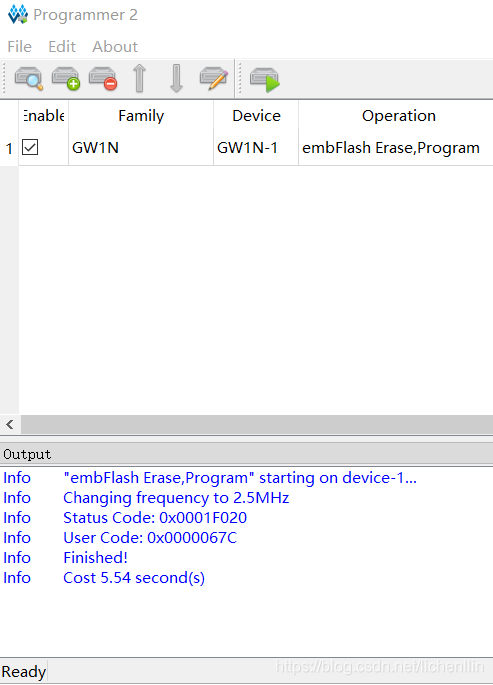

由于软件存在bug问题,所以要关闭一次program软件,再打开。选择embedded flash mode,选择embflash erase,program。选择save。

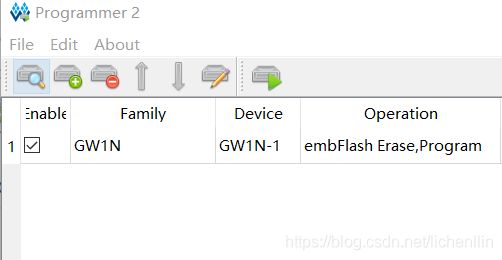

再次选择箭头,烧录内部flash。

如果再烧录其他的模式,记住必要重新打开一次烧录软件。

代码内容。blink_led.v

module blink_led

(

input sys_clk50m,

output[1:0] led

);

// wire sys_clk50m;

// GW_OSC osc_inst ( .oscout(sys_clk50m)) ;

localparam clk500ms = 50_000_000;

reg[31:0] clk_count;

always @(posedge sys_clk50m)

begin

if( clk_count ==clk500ms)

clk_count <=0;

else

clk_count <= clk_count + 1'd1;

end

wire led_temp;

assign led_temp =( clk_count> clk500ms[31:1]) ? 1'b0: 1'b1;

assign led= {led_temp,~led_temp};

//assign led =1'b0;

endmodule