X86系统寄存器(初始化系统,控制系统操作)

一、系统寄存器

1. EFLAGS 寄存器

① 存放system flags和IOPL;

②控制任务切换和模式切换,处理终端,指令追踪;

2.控制寄存器(CR0,CR2,CR3,CR4)

①控制系统级操作;

②支撑操作系统某些特性;

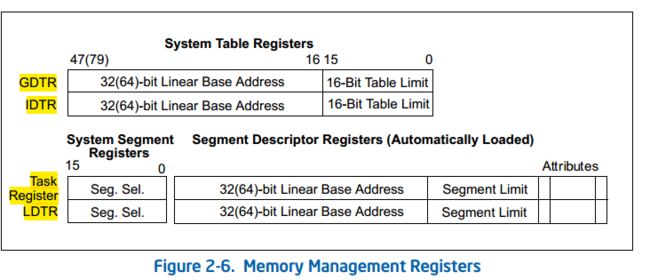

3.GDTR/LDTR/IDTR

①记录了GDT/LDT/IDT表的线性基址和大小;

4. 任务寄存器(task register)

①当前任务的线性地址;

②当前任务TSS的的大小;

5.Model-specific registers(MSRs)

① 主要用于操作系统或程序执行过程;

6.调试寄存器(debug registers)(DR0—DR7):用于设置断点

注:多数系统限制应用程序对系统寄存器的访问(除了EFLAGS);程序运行在特权级0时,可以更新系统寄存器的值;

7.IA-32e(64位扩展技术)

- GDTR/LDTR/TR被扩充到64bit;EFLAGES扩充为RFLAGS;CRO-CR4被扩充到64bits;

- 控制IA-32e mode 指令的MSRs

(1)IA32_KernelGSbase

(2)IA32_LSTAR

(3)IA32_SYSCALL_FLAG_MASK

(4)IA32_STAR_CS

(3)IA32_SYSCALL_FLAG_MASK

(4)IA32_STAR_CS

二、内存管理相关的寄存器(GDTR,LDTR,IDTR&&TR)

1. GDTR(Global Descriptor Table Register,全局符号表寄存器)

(1)基址(保护模式:32位;IA-32e模式:64bits)+GDT表最大size(16bit),基址是全局符号表GDT的地址;

(2)LGDT、SGDT分别load和store GDTR寄存器;

(3)计算机刚启动或者处理器重置之后,基址被设置为0,limit设置为0FFFFH;设置基址的值是保护模式下初始化处理器的一部分;

2. LDTR(Local Descriptor Table Register, 本地符号表寄存器)

(1)段选择器(16bits) + 基址(保护模式:32bits;IA-32e模式:64bits)+ segment Limit+LDT的属性;基址是LDT表的基础地址,Segment Limit表明了段字节数目;

(2)LLDT和SLDT指令分别load和store LDTR寄存器;GDT中存在LDT表的段描述符,LLDT指令load segment selector到LDTR时,基址和LDT属性也自动被load到LDTR中;

(3)任务切换时,新任务的段选择器、段基址、LDT表属性会自动被加载到LDTR中;

(4)计算机上电或者处理器重置时,LDTR中的segment selector、base address分别被置为0和0FFFFH

3.IDTR(Interrupt Descriptor Table Register,中断符号表寄存器)

(1)base address(保护模式:32bit;IA-32e模式:64bits)+table limit(16bit),基址指定了IDT表的地址,table limit说明了IDT表的大小;

(2)LIDT和SIDT命令分别负责IDTR寄存器的load/store操作;

(3)计算机刚上电或者处理器reset时,基址设置为0,limit设置为0FFFFH;LDTR初始化是处理器初始化的一部分;

4.TR(Task Register,任务寄存器)

(1)segment selector(16bit,段选择器)+base address(保护模式:32位;IA-32e模式:64bits)+ segment limit+当前任务TSS段属性描述符;(基址是TSS段基址;segment limit限制了TSS大小)

(2)GDT表中记录了TSS段描述符;

(3)LTR和STR分别负责TR寄存器的load和store操作;计算机上电或者处理器重置时,base address置为0,segment limit 设置为0FFFFH;

(4)发生任务切换时,自动调用LTR,将新任务的段选择器、基址、描述等load到TR寄存器中;

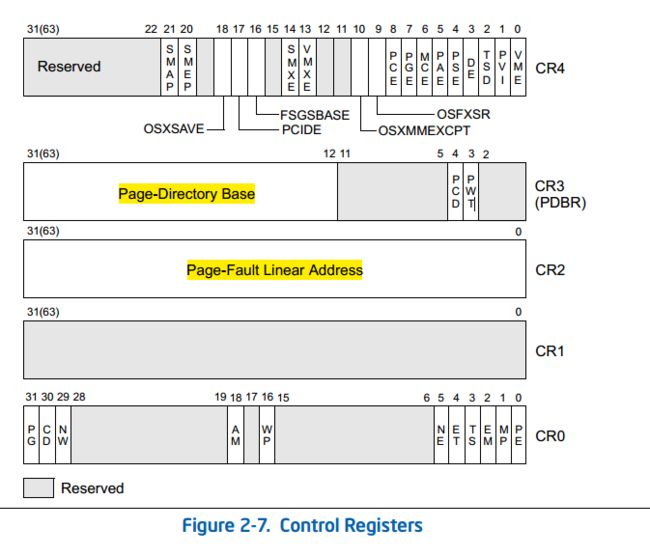

三、控制寄存器(CR0--CR4,CR8)

1.一般约定

(1)CRO和CR4的32~63bit预留,必须全为0;CR0和CR4高32位任意一位非0会触发general-protection exception;

(2)CR2的所有64bits均可被软件读写;

(3)CR3的40bit~51bit预留,必须为0;

(4)CR8仅仅在64bit模式下可以使用;

2.控制寄存器

- CR0:system control flags,控制操作模式和处理器状态;

- CR1:预留

- CR2:page-fault线性地址(导致页错误的线性地址)

- CR3:页全局目录的地址+PCD&&PWT(控制页表在cache中的缓存),使用物理地址扩展时,CR3寄存器包含页表目录表的指针;IA-32e模式下,CR3寄存器记录PML4表的基址;

- CR4:包括系统扩展相关的flags;通过mov指令读写该寄存器的值;

- CR8:提供对Task Priority Register(TPR)寄存器的读写访问;64bit模式下才可以使用;指定了操作系统用来控制可中断处理器的外部中断级别;

3.控制寄存器中的标识

- PG(bit 31 of CR0):Paging,置位:启动分页机制;清除:disable分页机制,所有线性地址作为物理地址;当PE没有置位时,PG flag没有效果;PG flag设置,PE flag没有置位时,会导致general protection exception;

- CD(bit 30 of CR0):Cache Disable,当CD和NW flags被清0时,启用cache机制(可以缓存整个内存系统数据);CD标识设置后,缓存满足一下限定表;CD flags置位后,处理器不可访问访问、更新cache;

- NW(bit 29 of CR0): Not Write-Through,NW和CD flags 被清零,启用write-back或者write-through,

- AM(bit 18 of CR0): Alignment Mask,启用自动对齐校验设置;清零,不支持自动地址对齐校验;置位,自动进行地址对齐校验;

- WP(bit 16 of CR0):write protect,置位:禁止处于超级权限的进程向只读pages写入数据;清零:允许超级权限进程向只读pages写入数据;支持LInux系统以copy-on-write的方法创建进程;

- NE(bit 5 of CR0): Numeric Error,置位:提供报告X87 浮点运算单元错误;清零:enables PC-Style X87 FPU error reporting;NE flag被清零&&IGNNE# input被断言,X87 FPU errors被忽略;NE flag被清零&&IGNNE#断言错误,unmasked x87 FPU errors导致处理器assert FERR# pin,产生外部中断,立刻终止指令执行;

- ET(bit 4 of CR0):Extension Type,奔腾4、Intel Xeon、P6 famil和奔腾处理器中保留该位;该位被硬编码为1;Intel386和Intel486处理器中,flag被置位后表明支持Intel 387 DX 数学协处理器指令集;

- TS(bit 3 of CR0):Task Switched,允许X87 FPU/MMX/SSE/SSE2/SSE3/SSE4 上下文转换推迟到新任务真正需要FPU/MMX/SSE/SSE2/SSE3/SSE4时;

- EM(bit 2 of CR0):Emulation

- MP(bit 1 of CR0):Monitor Coprocessor

- PE(bit 0 of CR0):Protection Enable

- PCD(bit 4 of CR3):Page-level Cache Disable,控制访问页全局目录的方式;disable 分页基址或者PAE分页模式下、IA-32e模式下,CR4.PCIDE=1,该位不被使用;

- PWT(bit 3 of CR3):Page-Level Write-Through,控制访问页全局目录的方式;

- VME(bit 0 of CR4):Virtual-8086 Mode Extension,置位后,允许在virtual-8086模式下处理中断和异常,由于避免了通过virtual-8086 monitor处理异常和中断的开销,因而可以提高应用的性能;

- PVI(bit 1 of CR4):Protected-Mode Virtual Interrupts,置位:为Virtual interrupt flag(VIF)提供了硬件支持;清零,不支持VIF;

- TSD(bit 2 of CR4):Time Stamp Disable,置位,限制特权级0下使用RDTSC指令;清零后,允许在任何特权级执行RDTSC指令;

- DE(bit 3 of CR4):Debugging Extension,置位后,使用调试寄存器DR4和DR5会引发undefined opcode 的异常;清零,处理器依靠使用DR4和DR5兼容早期IA-32处理器;

- PSE(bit 4 of CR4):Page Size Extension,置位后,enable 4MB page;清零后,页基本大小4KB;

- PAE(bit 5 of CR4):Physical Address Extension,置位后,允许分页过程中产生大于32bit的地址(页框号);清零后,页号必须不大于32bit;IA-32e模式下必须激活PAE

- MCE(bit 6 of CR4): machine check enable,置位后,启用机器校验;清零后,disable machine check exception;

- PGE(bit 7 of CR4):Page Global Enable,第六代处理器中引入;置位后,启用global page feature;清零后,disable global page ;global page feature允许经常使用的pages或者共享pages被标记为global to all users;上下文任务切换或者写寄存器CR3时,global pages不从TLB中flush出去;

- PCE(bit 8 of CR4):Performance-Monitoring Counter Enable,置位,允许在任何保护级别执行RDPMC指令;清零,RDPMC指令仅仅可以在特权级0执行;

- OSFXSR(bit 9 of CR4):Operating System Support for FXSAVE and FXRSTOR instruction,置位:(1)表明操作系统支持指令FXSAVE和FXRSTOR;(2)FXSAVE和FXSTORE指令分别用来保存和恢复寄存器X87 FPU、XMM、MXCSR和MMX的内容;(3)处理器执行SSE/SSE2/SSE3/SSSE3/SSE4指令时会抛出PAUSE, PREFETCHh,SFENCE, LFENCE, MFENCE,MOVNTI, CLFLUSH, CRC32, POPCNT异常;

- OSXMMEXCPT(bit 10 of CR4):Operating System Support for Unmasked SIMD Floating-Point Exception,置位:表明操作系统支持unmasked SIMD浮点Exception的执行;SIMD floating-point异常仅仅会由SSE/SSE3/SSE2/SSE4 SIMD浮点指令产生;

- VMXE(bit 13 of CR4):VMX-Enabled bit,置位后启用VMX操作;

- SMXE(bit 14 of CR4):SMX-Enabled Bit,置位后启用SMX操作;

- FSGSBASE (bit 16 of CR4):FSGSBASE-Enable Bit,置位后启用RDFSBASE,RDGSBASE,WRFSBASE和WRGSBASE指令;

- PCIDE(bit 17 of CR4):PCID-Enable Bit,置位后启用process-context-identifiers(PCIDs);

- OSXSAVE(bit 18 of CR4):XSAVE and Processor Extended Stats-Enable Bit,置位:(1)表明操作系统支持普通软件使用XGETBV,XSAVE和XRSTOR指令;(2)启用XSAVE和XRSTOR指令保存或恢复X87 FPU寄存器和SSE寄存器状态以及其他XCR0状态;(3)启用可读写XCR0的XGETBV和XSETBV指令;

- SMEP(bit 20 of CR4):SMEP-Enable Bit,置位:禁止在监督模式下执行指令;

- SMAP(bit 21 of CR4):SMAP-Enable Bit,置位:禁止在监督模式下访存

- PKE(bit 22 of CR4):Protection Key Enable Bit, IA-32e分页基址中,允许为每个线性地址分配一个protection key;PKRU寄存器内的值表明用户模式下带有protection key的线性地址是否可被读或被写;RDPKRU和WRPKRU指令分别读写寄存器PKRU的值;

- TPL(bit 3:0 of CR8):Task Priority Level,设置中断可以被阻塞的优先级阈值,0表示所有中断均enabled;15表示中断特权disabled

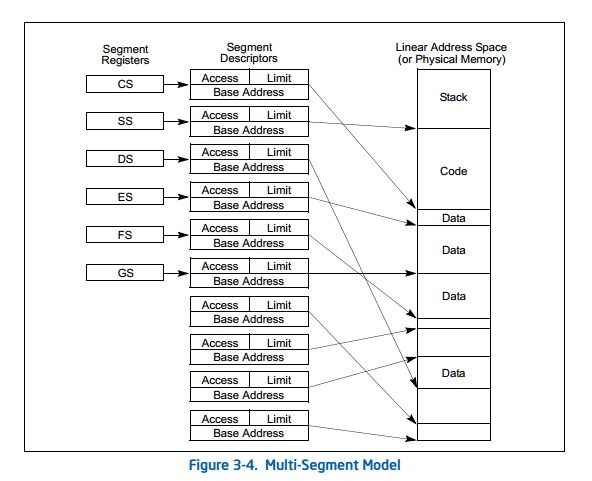

四、Segment Register

- CS存放代码段基址;

- SS寄存器存放堆栈段基址;

- DS/ES/FS/GS寄存器存放数据段基址;

注:code segment被设置为Read-Only Segments;64bit模式下,分段一般是disabled的,处理器将CS/DS/ES/SS值设置为0;

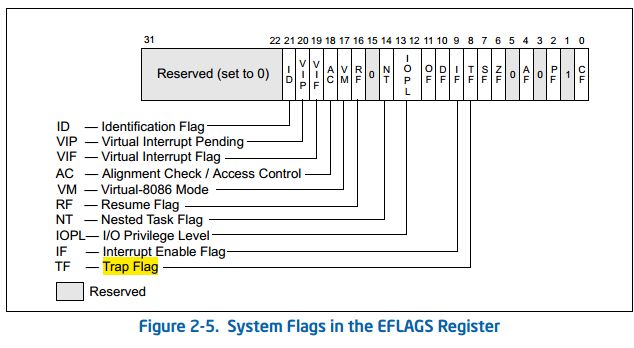

五、EFLAGS寄存器中系统标志

控制I/O,可屏蔽硬件中断、调试、任务切换,支持virtual-8086 mode;

- TF(8):Trap,①置位,启用单步调试;②清除,disable单步调试;

- IF(9):Interrupt enable,控制the response to maskable hardware interrupt;①置位,响应可屏蔽硬件中断;②清零,禁止可屏蔽中断;该位不影响不可屏蔽中断(NMI);

- IOPL(12,13bit):I/O privilege level filed(I/O特权级),表明当前正在运行任务的I/O特权级,当前运行程序的特权级必须不大于IOPL;当且仅当当前特权级为0时,POPF和IRET指令可以更新该域;

- NT(14bit):Nested task,控制嵌套中断和嵌套任务;

- RF(16bit):Resume,控制处理器对指令中断的相应;①置位,disable debug exceptions;②清零,中断条件满足时,产生debug exception;

- VM(17bit):置位,启用virtual-8086 mode;清除,返回到protected mode;

- AC(18bit): alignment check or access control,①置位:AMbit通过CR0置位时,对齐检查和用户模式下数据访问启用,访问非对齐地址时,会产生algnment-check exception;②可用来检查数据是否对齐,

- VIF(19bit): Virtual Interrupt,当VME flag or PVI flag在CR4中置位,或者IOPL小于3时,处理器才可以识别VIP flag;

- VIP(20bit): Virutal Interrupt Pending,①置位,中断正在执行;②清零,无中断正在运行;该标志和VIF标识结合使用,处理器读取该标志,但从来不更新该标志;当VME flag or PVI flag在CR4中置位,或者IOPL小于3时,处理器才可以识别VIP flag;

- ID(21bit):Identification,表明是否支持CPUID指令;