1、RS485采用差分信号负逻辑,+2V~+6V表示“0”,- 6V~- 2V表示“1”。RS485有两线制和四线制两种接线,四线制是全双工通讯方式(以前有四线制接法,只能实现点对点的通信方式,现很少采用), 两线制是半双工通讯方式。常用的是半双工的通信总线,在通信时要保证收发时序不冲突、同向时序不冲突。

2、485的匹配电阻分置在两端,当多个器件连接在485总线上时,只有最远端的器件添加有匹配电阻,增减器件时要保证包含匹配电阻的器件在通信总线上的完整性。

3、使用串口485时,485之间的信号是差分信号,485与串口通信时TTL信号,485的优点是保证两485芯片之间的差分信号能过远距离传输。传输速率取决于距离、485芯片、匹配电阻、以及串口速率(当基于串口通信时)等。

4、信号接地的原因:①485芯片SN65HVD1782在5v供电时,共模电压在2.5v左右,RS-485接口采用差分方式传输信号,并不需要相对于某个参照点来检测信号,系统只需检测两线之间的电位差就可以了。但收发器有一定的共模电压范围, RS-485收发器共模电压范围为-7~+12V,只有满足上述条件,整个网络才能正常工作。当网络线路中共模电压超出此范围时就会影响通信的稳定可靠,甚至损坏接口芯片。所以在使用中最好接地。上电时通过测量共模电压可以判断芯片是否损坏, 在差分相AB端接TVS管进行AB相保护,首先检查TVS管是否烧毁。

②、EMI(电磁兼容性)问题:发送驱动器输出信号中的共模部分需要一个返回通路,如没有一个低阻的返回通道(信号地),信号中的共模部分就会以辐射的形式返回源端,整个总线就会像一个巨大的天线向外辐射电磁波。

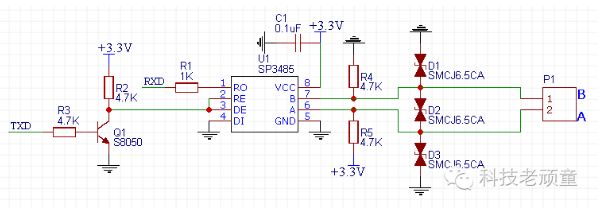

485自动收发电路(该电路引自瑞生网http://www.rationmcu.com/elecjc/2397.html)

当TXD发送bit0时,Q1关闭,485芯片使能引脚为高电平,为发送状态,发送端口DI接地,AB相发送bit0。

当TXD发送bit1时,Q1开启,485芯片使能引脚为低电平,为接受状态,AB相位为高阻态,由于R4和R5下拉和上拉电阻的作用AB相数据为1。

当接受状态时,TXD引脚一直为高电平。

5、在进行项目调试时使用循环指令对手挽手连接的485通讯电路进行485通讯,发现部分485电路有超时回复的现象,静态通讯测试时无通讯超时问题,当控制子485电路运行时则出现超时回复的现象,

当即认为是运行的机器干扰,也确实未使用屏蔽双绞线进行屏蔽措施。经过使用一些措施并无效果。这里存在思维定势,机器运行是通讯变化的因素,但是程序的控制回路也是变化的因素,通过对超时现象的整理与统计发现超时出现很有规律性,

当上一个以逻辑的的485电路运行时会影响下一个逻辑的485电路通讯,改变布置位置顺序关系仍存在该问题。初步判断为程序控制问题排除硬件给干扰。通过逻辑分析仪进行波形采集发现接收的波形数据存在问题,波形相同但是译码存在错误,因为若有数据也在发送则波形不会相同,则认为发送收到影响,只有发送控制端有使能高电平的时候子485电路才能对总线产生干扰,根据分析猜想运行的关节通信使能端口对发送指令产生影响。通过对2号逻辑的使能端检测与3号板的输入和输出信号检测。在超时通讯超时时使用逻辑分析仪进行采集,通过对比发现,在超时现象发生时2号板的发送使能端在发送完成后并未置为低电平的接收状态,与正常通讯相比延长了30us,从而造成与主485电路发送的指令冲突,造成3号板接收数据错误从产生无回复的现象。数据回复发送使用串口DMA进行,在程序DMA发送中有等待发送完成检测,等待发送完成后置为接收状态,出现该现象可能是因为该等待程序被运行的控制程序打断,造成接受状态的转换延时,造成时序冲突。通过采取取消等待发送检测,使用高优先级的DMA传输完成中断对发送至接收状态的转换。

总结:1、当问题现象发生时要观察问题发生的特点看有无规律和特点可言,了解问题整体的轮廓不要一下子扎进去。通过问题现象分析故障的范围。

2、保持原有的实验环境不变,静态和动态测试改变的不止电磁等工作环境也存在程序控制回路的改变。

3、逻辑分析仪采集的采集波形只能作为参考和实际示波器采集有很大的不同,在通讯时不仅要看逻辑分析仪的解码同样要看逻辑分析仪的波形或者看示波器采集的波形,通讯码的解析对应有通信波特率的时间点的采样,对比问题波形与正常波形的特点。

4、485通讯总线上若有两个设备同事占用总线时会对总线数据产生干扰,同时有数据发送时会造成解析数据错误、波形错误,若一方只是占用则波形会近似相等。

5、在进行通讯等一些程序对时序有严格要求的时程序要进行一些安全保护措施防止费打断,如屏蔽中断、使用DMA发送接收,不使用等待语句进行状态的切。

6、相互配合完成项目目时时要指出程序中的哪些进程不能被打断。