EDA笔记(13)--代码举例汇总(待续)

目录

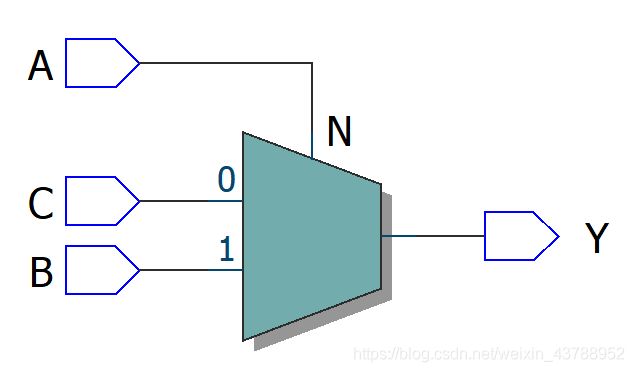

1.设计一个选择器(IF语句)

代码:

逻辑图:

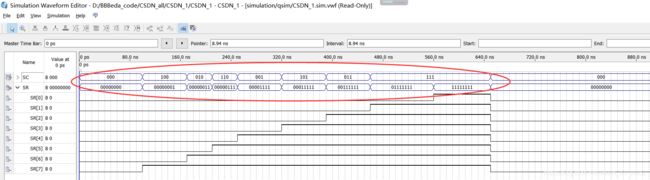

2.设计8-3线优先编码器(IF语句)

代码:

验证仿真波形图:

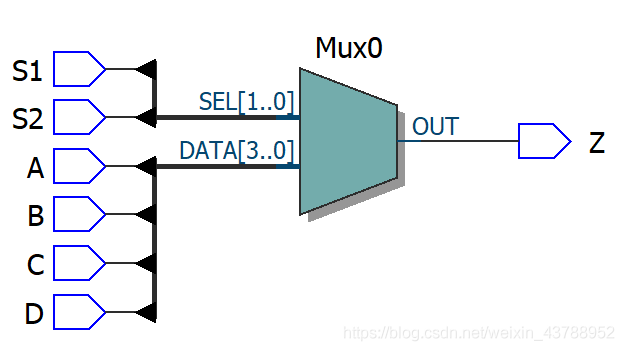

3.设计4选1多路信号选择器(case语句)

代码:

逻辑图:

4.十进制加法计数器(组合逻辑电路)

代码:

验证仿真波形图:

5.十进制加法计数器(时序逻辑电路)

代码:

验证仿真波形图:

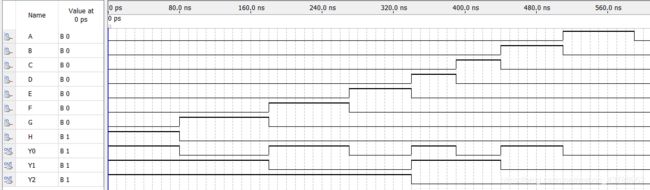

6.八线-三线优先编码器(条件赋值语句)

代码:

验证仿真波形图:

7.设计指令译码器(选择信号控制语句)

代码:

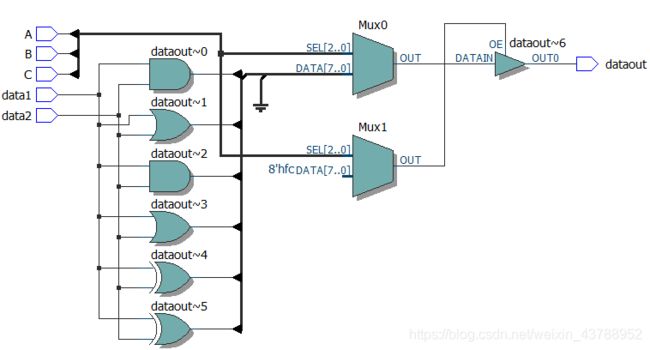

逻辑图:

8.设计三个相同与非门构成的电路(元件例化)

代码:

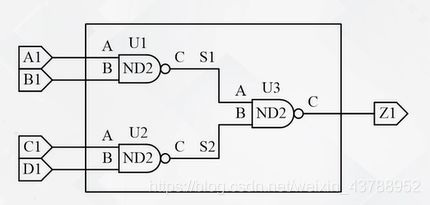

逻辑图:

10.设计3线-8线译码器(高电平有效)

代码:

11.设计8线-3线优先编码器(LOOP语句)

代码:

12.设计4选1信号选择器(IF_ELSE语句)

代码:

13.设计8位单向总线驱动器

代码:

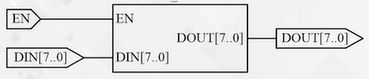

参考图:

14.设计8位双向总线缓冲器

代码:

参考图:

15.设计异步复位/置位的D触发器

代码:

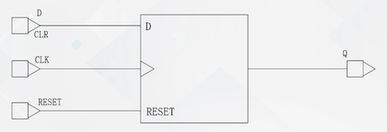

参考图:

16.设计同步复位的D触发器

代码:

参考图:

17.设计JK触发器

代码:

参考图:

18.设计并行输入,同步复位的8位移位寄存器

代码:

参考图:

19.设计带时钟使能的十进制同步计数器

代码:

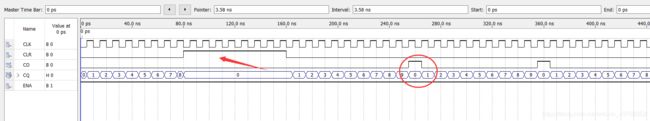

验证仿真波形图:

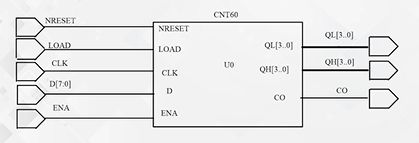

20.设计8421 BCD码60进制计数器

代码:

参考图:

21.设计1khz方波转换为50hz信号的非均匀分频电路

代码:

验证仿真波形图:

22.设计1khz方波转换为50hz信号的均匀分频电路

代码:

验证仿真波形图:

1.设计一个选择器(IF语句)

代码:

--设计一个选择器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_1 is

port (A,B,C: in boolean;

Y: out boolean);

end entity CSDN_1;

architecture bhv of CSDN_1 is

begin

process(A,B,C) is

variable N: boolean;

begin

if A then N:=B;

else N:=C;

end if;

Y<=N;

end process;

end architecture bhv;逻辑图:

2.设计8-3线优先编码器(IF语句)

代码:

--8线-3线优先编码器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_2 is

port(SR: in std_logic_vector(0 to 7);

SC: out std_logic_vector(0 to 2));

end entity CSDN_2;

architecture bhv of CSDN_2 is

begin

process(SR) is

begin

if(SR(7)='0') then SC<="000"; --优先级最高

elsif(SR(6)='0') then SC<="100";

elsif(SR(5)='0') then SC<="010";

elsif(SR(4)='0') then SC<="110";

elsif(SR(3)='0') then SC<="001";

elsif(SR(2)='0') then SC<="101";

elsif(SR(1)='0') then SC<="011";

else SC<="111";

end if;

end process;

end architecture bhv;验证仿真波形图:

即有波形仿真可以看出,SR(7)的优先级最大

3.设计4选1多路信号选择器(case语句)

代码:

--设计4选1多路信号选择器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_3 is

port(S1,S2: in std_logic;--选择控制信号

A,B,C,D: in std_logic;--输入信号

Z: out std_logic);--选择器的输出信号

end entity CSDN_3;

architecture bhv of CSDN_3 is

signal S: std_logic_vector(1 downto 0);

begin

S<=S1&S2;--合并,方便选择控制

process(S,A,B,C,D) is

begin

case S is

when "00"=>Z<=A;

when "01"=>Z<=B;

when "10"=>Z<=C;

when "11"=>Z<=D;

when others=>Z<='X';

end case;

end process;

end architecture bhv;

逻辑图:

4.十进制加法计数器(组合逻辑电路)

代码:

--十进制加法计数器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_4 is

port(CLR: in std_logic;--清零

DIN: in std_logic_vector(3 downto 0);--输入

CNT: out std_logic_vector(3 downto 0));--输出

end entity CSDN_4;

architecture bhv of CSDN_4 is

begin

process(DIN,CLR) is

begin

if(CLR='1' or DIN="1001") then

CNT<="0000";

else

CNT<=DIN+1;

end if;

end process;

end architecture bhv;验证仿真波形图:

5.十进制加法计数器(时序逻辑电路)

代码:

--十进制加法计数器(时序逻辑电路)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_5 is

port(CLR: in std_logic;

CLK: in std_logic;

CNT: buffer std_logic_vector(3 downto 0));

end entity CSDN_5;

architecture bhv of CSDN_5 is

begin

process is

begin

wait until CLK'event AND CLK= '1';--等待CLK的上升沿

if (CLR= '1' or CNT=9) then

CNT<="0000";

else

CNT<=CNT+1;

end if;

end process;

end architecture bhv;验证仿真波形图:

6.八线-三线优先编码器(条件赋值语句)

代码:

--8线-3线优先编码器(条件赋值语句)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity CSDN_6 is

port(A,B,C,D,E,F,G,H: in std_logic;

Y0,Y1,Y2: out std_logic);

end entity CSDN_6;

architecture bhv of CSDN_6 is

signal SY: std_logic_vector(2 downto 0);

begin

SY(2 downto 0)<="111" when H='1' else --优先级最高

"110" when G='1' else

"101" when F='1' else

"100" when E='1' else

"011" when D='1' else

"010" when C='1' else

"001" when B='1' else

"000" when A='1' else

"XXX";

Y0<=SY(0);

Y1<=SY(1);

Y2<=SY(2);

end architecture bhv;验证仿真波形图:

7.设计指令译码器(选择信号控制语句)

代码:

--指令译码器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_7 is

port(A,B,C: in std_logic;--输入控制信号

data1,data2: in std_logic;--输入操作数据

dataout: out std_logic);--输出结果

end entity CSDN_7;

architecture bhv of CSDN_7 is

signal Q :std_logic_vector(2 downto 0);

begin

Q<=C&B&A;

with Q select

dataout<=data1 AND data2 when "000",

data1 OR data2 when "001",

data1 NAND data2 when "010",

data1 NOR data2 when "011",

data1 XOR data2 when "100",

data1 XNOR data2 when "101",

'Z' when others; --Z为高阻态

end architecture bhv;逻辑图:

8.设计三个相同与非门构成的电路(元件例化)

代码:

--设计三个相同与非门构成的电路(元件例化)

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_8 is

port(A,B: in std_logic;

C: out std_logic);

end entity CSDN_8;

architecture bhv of CSDN_8 is

begin

C<=A NAND B; --与非

end architecture bhv;

library ieee;

use ieee.std_logic_1164.all;

entity OR3 is

port(A1,B1,C1,D1: in std_logic;

Z1: out std_logic);

end entity OR3;

architecture art of OR3 is

component CSDN_8 is --元件调用声明

port(A,B: in std_logic;

C: out std_logic);

end component;

signal S1,S2: std_logic;

begin

U1: CSDN_8 port map(A1,B1,S1);--位置关联

U2: CSDN_8 port map(A=>C1,C=>S2,B=>D1);--名字关联方式

U3: CSDN_8 port map(S1,S2,C=>Z1);--混合关联方式

end architecture art;逻辑图:

10.设计3线-8线译码器(高电平有效)

代码:

--3线-8线译码器(高电平有效)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_10 is

port (A,B,C: in std_logic;

Y: out bit_vector(7 downto 0));

end entity CSDN_10;

--SLL逻辑左移

architecture bhv1 of CSDN_10 is

signal SR: std_logic_vector(2 downto 0);

begin

SR<=C&B&A;

Y<="00000001" SLL(conv_integer(SR));--SLL逻辑左移

--标准逻辑位矢量类型数据强制转换成整数类型数据

end architecture bhv1;

--使用进程process语句

architecture bhv2 of CSDN_10 is

signal SR: std_logic_vector(2 downto 0);

begin

SR<=C&B&A;

process(SR) is

begin

Y<=(others=>'0'); --Y的非指定位都赋值给'0'

Y(conv_integer(SR))<='1'; --由SR所确定的Y的指定位赋值为'1'

end process;

end architecture bhv2;

--when-else语句

architecture bhv3 of CSDN_10 is

signal SR: std_logic_vector(2 downto 0);

begin

SR<=C&B&A;

Y(0)<='1' when SR="000" else '0';--并行执行,当只有一个条件成立时,其他条件不成立

Y(1)<='1' when SR="001" else '0';

Y(2)<='1' when SR="010" else '0';

Y(3)<='1' when SR="011" else '0';

Y(4)<='1' when SR="100" else '0';

Y(5)<='1' when SR="101" else '0';

Y(6)<='1' when SR="110" else '0';

Y(7)<='1' when SR="111" else '0';

end architecture bhv3;

--case-when语句

architecture bhv4 of CSDN_10 is

signal SR: std_logic_vector(2 downto 0);

begin

SR<=C&B&A;

process(SR) is

begin

case SR is

when "000"=>Y<="00000001";

when "001"=>Y<="00000010";

when "010"=>Y<="00000100";

when "011"=>Y<="00001000";

when "100"=>Y<="00010000";

when "101"=>Y<="00100000";

when "110"=>Y<="01000000";

when "111"=>Y<="10000000";

when others=>Y<="00000000";

end case;

end process;

end architecture bhv4;

11.设计8线-3线优先编码器(LOOP语句)

代码:

--设计8线-3线优先编码器(LOOP语句)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity CSDN_11 is

port(A,B,C,D,E,F,G,H: in std_logic;

Y0,Y1,Y2: out std_logic);

end entity CSDN_11;

--loop循环语句

architecture bhv of CSDN_11 is

begin

process(A,B,C,D,E,F,G,H) is

variable V: std_logic_vector(7 downto 0);

variable I: integer;

begin

V:=(H,G,F,E,D,C,B,A);--H优先级最高

I:=7;

while I>=0 AND V(I)/='1' loop

I:=I-1;

end loop;

(Y2,Y1,Y0)<=conv_std_logic_vector(I,3);--转换为位宽为3

end process;

end architecture bhv;

12.设计4选1信号选择器(IF_ELSE语句)

代码:

--4选1信号选择器(IF_ELSE语句)

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_12 is

port(X: in std_logic_vector(3 downto 0);--输入信号

A,B: in std_logic;--控制信号

Y: out std_logic);--输出信号

end entity CSDN_12;

architecture bhv of CSDN_12 is

signal SEL : std_logic_vector(1 downto 0);

begin

SEL<=B&A;

process(X,SEL) is

begin

if(SEL="00") then Y<=X(0);

elsif (sel="01") then Y<=X(1);

elsif (sel="10") then Y<=X(2);

else Y<=X(3);

end if;

end process;

end architecture bhv;13.设计8位单向总线驱动器

代码:

--8位单向总线驱动器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_13 is

port(DIN: in std_logic_vector(7 downto 0);--输入

EN: in std_logic;--使能端

DOUT: out std_logic_vector(7 downto 0));--输出

end entity CSDN_13;

architecture bhv of CSDN_13 is

begin

process(EN, DIN) is

begin

if(EN='1') then

DOUT<=DIN;

else

DOUT<="ZZZZZZZZ";

end if;

end process;

end architecture bhv;参考图:

14.设计8位双向总线缓冲器

代码:

--设计8位双向总线缓冲器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_14 is

port(A,B: inout std_logic_vector(7 downto 0);--双向输入输出端口

EN,DIR: in std_logic);--使能端,方向控制端口

end entity CSDN_14;

architecture bhv of CSDN_14 is

signal AOUT,BOUT: std_logic_vector(7 downto 0);

begin

process(A,EN,DIR) is --A输入B输出

begin

if((EN='0') AND (DIR='1')) then

BOUT<=A;

else

BOUT<="ZZZZZZZZ";

end if;

B<=BOUT;

end process;

process(B,EN,DIR) is --B输入A输出

begin

if((EN='0') AND (DIR='0')) then

AOUT<=B;

else

AOUT<="ZZZZZZZZ";

end if;

A<=AOUT;

end process;

end architecture bhv;参考图:

15.设计异步复位/置位的D触发器

代码:

--异步复位/置位的D触发器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_15 is

port(CLK,D,PRESET,CLR: in std_logic;

Q: out std_logic);

end entity CSDN_15;

architecture bhv of CSDN_15 is

begin

process(CLK, PRESET, CLR) is

begin

if(PRESET='1') then --置位信号为1,触发器被置位

Q<='1';

elsif(CLR='1') then --复位信号为1,触发器被复位

Q<='0';

elsif(CLK'EVENT AND CLK='1') then

Q<=D;

end if;

end process;

end architecture bhv;

参考图:

16.设计同步复位的D触发器

代码:

--同步复位的D触发器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_16 is

port(D,CLK,RESET: in std_logic;

Q: out std_logic);

end entity CSDN_16;

architecture bhv of CSDN_16 is

begin

process(CLK) is

begin

if(CLK'EVENT AND CLK='1') then

if(RESET='0') then --时钟上升沿到来且复位信号有效时,触发器被复位

Q<='0';

else

Q<=D;

end if;

end if;

end process;

end architecture bhv;参考图:

17.设计JK触发器

代码:

--JK触发器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_17 is

port(J,K,CLK: in std_logic;

Q,QB: buffer std_logic);

end entity CSDN_17;

architecture bhv of CSDN_17 is

signal Q_S, QB_S: std_logic;--保持信号变化的中间结果

begin

process(CLK,J,K) is

begin

if(CLK'EVENT AND CLK='1') then

if(J='0' AND K='1') then

Q_S<='0';

QB_S<='1';

elsif(J='1' AND K='0') then

Q_S<='1';

QB_S<='0';

elsif(J='1' AND K='1') then --反转

Q_S<=NOT Q_S;

QB_S<=NOT QB_S;--输出翻转

end if;

end if;

Q<=Q_S;

QB<=QB_S;

end process;

end architecture bhv;

参考图:

18.设计并行输入,同步复位的8位移位寄存器

代码:

--并行输入,同步复位的8位移位寄存器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_18 is

port(CLK, RESET: in std_logic; --时钟信号,复位信号

LSFT, REFT: in std_logic; --左移信号,右移信号

DATA: in std_logic_vector(7 downto 0); --数据输入

MODE: in std_logic_vector(1 downto 0); --模式控制

QOUT: buffer std_logic_vector(7 downto 0)); --输出端口

end entity CSDN_18;

architecture bhv of CSDN_18 is

begin

process is

begin

wait until (rising_edge(CLK));

if (RESET='1') then --同步复位

QOUT<="00000000";

else

case MODE is

when "01"=>QOUT<=REFT&QOUT(7 downto 1); --右移一位

when "10"=>QOUT<=QOUT(6 downto 0)&LSFT; --左移一位

when "11"=>QOUT<=DATA; --并行输入

when others=>NULL;

end case;

end if;

end process;

end architecture bhv;

参考图:

19.设计带时钟使能的十进制同步计数器

代码:

--带时钟使能的十进制同步计数器

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_19 is

port(CLK: in std_logic; --计数时钟信号

CLR: in std_logic; --清零信号

ENA: in std_logic; --计数使能信号

CQ: out integer range 0 to 15; --4位计数结果输出

CO: out std_logic); --计数进位

end entity CSDN_19;

architecture bhv of CSDN_19 is

signal CQ1: integer range 0 to 15;--保持计数过程的中间结果

begin

process(CLK,CLR,ENA) is --计数控制进程

begin

if CLR='1' then --异步清零

CQ1<=0;

elsif CLK'EVENT AND CLK='1' then

if ENA='1' then

if CQ1=9 then --等于9,计数器清零

CQ1<=0;

else

CQ1<=CQ1+1;

end if;

end if;

end if;

end process;

process(CLK,CQ1) is --控制进位输出

begin

if CLK'EVENT AND CLK='1' then --利用同步时钟可以去毛刺

if CQ1=9 then

CO<='1';

else

CO<='0';

end if;

end if;

end process;

CQ<=CQ1;

end architecture bhv;验证仿真波形图:

20.设计8421 BCD码60进制计数器

代码:

--8421 BCD码60进制计数器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_20 is

port(EN: in std_logic; --使能信号

RESET: in std_logic; --异步复位

LOAD: in std_logic; --置数

D: in std_logic_vector(7 downto 0); --预置数据

CLK: in std_logic; --时钟信号

CO: out std_logic; --进位输出

QH: buffer std_logic_vector(3 downto 0); --输出高四位

QL: buffer std_logic_vector(3 downto 0)); --输出低四位

end entity CSDN_20;

architecture bhv of CSDN_20 is

begin

CO<='1' when (QH="0101" AND QL="1001" AND EN='1' ) --进位输出

else '0';

process (CLK,RESET) is

begin

if(RESET='0') then --异步复位

QH<="0000";

QL<="0000";

elsif(CLK'EVENT AND CLK='1') then --同步置数

if(LOAD='1') then

QH<=D(7 downto 4);

QL<=D(3 downto 0);

elsif(EN='1') then --计数控制

if(QL=9) then

QL<="0000";

if(QH<=5) then

QH<="0000";

else

QH<=QH+1;

end if;

else

QL<=QL+1;

end if;

end if;

end if;

end process;

end architecture bhv;

参考图:

21.设计1khz方波转换为50hz信号的非均匀分频电路

代码:

--1khz方波转换为50hz信号的非均匀分频电路

library ieee;

use ieee.std_logic_1164.all;

entity CSDN_21 is

port(CLK: in std_logic; --1khz信号输入

NEWCLK: out std_logic); --50hz信号输出

end entity CSDN_21;

architecture bhv of CSDN_21 is

signal CNT: integer range 0 to 10#19#; --保持计数中间结果

begin

process(CLK) is --分频计数器,1khz时钟信号产生50hz信号

begin

if CLK'EVENT AND CLK='1' then

if CNT=10#19# then --1khz转换50hz,分频常数为1000/50=20

CNT<=0;

else

CNT<=CNT+1;

end if;

end if;

end process;

process(CLK,CNT) is --分频输出

begin

if CLK'EVENT AND CLK='1' then

if CNT=10#19# then

NEWCLK<='1';

else

NEWCLK<='0';

end if;

end if;

end process;

end architecture bhv;验证仿真波形图:

22.设计1khz方波转换为50hz信号的均匀分频电路

代码:

--1khz方波转换为50hz信号的均匀分频电路

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity CSDN_22 is

port(CLK_IN: in std_logic;

RESET: in std_logic;

CLK_OUT: out std_logic);

end entity CSDN_22;

architecture bhv of CSDN_22 is

constant Q: integer:=20;

begin

process(CLK_IN,RESET) is

variable CNT: integer range 0 to 19;

begin

if(RESET='1') then

CNT:=0;

CLK_OUT<='0';

elsif rising_edge(CLK_IN) then

if(CNT<(Q/2)) then --前一半周期输出高电平

CLK_OUT<='1';

CNT:=CNT+1;

elsif(CNT<(Q-1)) then --后一半周期输出低电平

CLK_OUT<='0';

CNT:=CNT+1;

else --计数值大于20,则清零

CNT:=0;

end if;

end if;

end process;

end architecture bhv;验证仿真波形图:

23.