SPI总线verilog hdl实现(1)SPI通信

SPI总线传输只需要4根线就能完成,这四根线的作用分别如下:

SCK(Serial Clock):SCK是串行时钟线,作用是Master向Slave传输时钟信号,控制数据交换的时机和速率;

MOSI(Master Out Slave in):在SPI Master上也被称为Tx-channel,作用是SPI主机给SPI从机发送数据;

CS/SS(Chip Select/Slave Select):作用是SPI Master选择与哪一个SPI Slave通信,低电平表示从机被选中(低电平有效);

MISO(Master In Slave Out):在SPI Master上也被称为Rx-channel,作用是SPI主机接收SPI从机传输过来的数据;

SPI总线传输一共有4中模式,这4种模式分别由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义,其中CPOL参数规定了SCK时钟信号空闲状态的电平,CPHA规定了数据是在SCK时钟的上升沿被采样还是下降沿被采样。

模式0:CPOL= 0,CPHA=0。SCK串行时钟线空闲是为低电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

模式1:CPOL= 0,CPHA=1。SCK串行时钟线空闲是为低电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式2:CPOL= 1,CPHA=0。SCK串行时钟线空闲是为高电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式3:CPOL= 1,CPHA=1。SCK串行时钟线空闲是为高电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿切换

以模式0为例

发送:当FPGA通过SPI总线往从机中发送一个字节(8-bit)的数据时,首先FPGA把CS/SS片选信号设置为0,表示准备开始发送数据,整个发送数据过程其实可以分为16个状态:

状态0:SCK为0,MOSI为要发送的数据的最高位,即I_data_in[7]

状态1:SCK为1,MOSI保持不变

状态2:SCK为0,MOSI为要发送的数据的次高位,即I_data_in[6]

状态3:SCK为1,MOSI保持不变

状态4:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[5]

状态5:SCK为1,MOSI保持不变

状态6:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[4]

状态7:SCK为1,MOSI保持不变

状态8:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[3]

状态9:SCK为1,MOSI保持不变

状态10:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[2]

状态11:SCK为1,MOSI保持不变

状态12:SCK为0,MOSI为要发送的数据的下一位,即I_data_in[1]

状态13:SCK为1,MOSI保持不变

状态14:SCK为0,MOSI为要发送的数据的最低位,即I_data_in[0]

状态15:SCK为1,MOSI保持不变

一个字节数据发送完毕以后,产生一个发送完成标志位O_tx_done并把CS/SS信号拉高完成一次发送。

接收:当FPGA通过SPI总线从从机中接收一个字节(8-bit)的数据时,首先FPGA把CS/SS片选信号设置为0,表示准备开始接收数据,整个接收数据过程其实也可以分为16个状态,但是与发送过程不同的是,为了保证接收到的数据准确,必须在数据的正中间采样,也就是说模式0时序图中灰色实线的地方才是代码中锁存数据的地方,所以接收过程的每个状态执行的操作为:

状态0:SCK为0,不锁存MISO上的数据

状态1:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[7]

状态2:SCK为0,不锁存MISO上的数据

状态3:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[6]

状态4:SCK为0,不锁存MISO上的数据

状态5:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[5]

状态6:SCK为0,不锁存MISO上的数据

状态7:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[4]

状态8:SCK为0,不锁存MISO上的数据

状态9:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[3]

状态10:SCK为0,不锁存MISO上的数据

状态11:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[2]

状态12:SCK为0,不锁存MISO上的数据

状态13:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[1]

状态14:SCK为0,不锁存MISO上的数据

状态15:SCK为1,锁存MISO上的数据,即把MISO上的数据赋值给O_data_out[0]

一个字节数据接收完毕以后,产生一个接收完成标志位O_rx_done并把CS/SS信号拉高完成一次数据的接收。

I_clk是系统时钟;

I_rst_n是系统复位;

I_tx_en是主机给从机发送数据的使能信号,当I_tx_en为1时主机才能给从机发送数据;

I_rx _en是主机从从机接收数据的使能信号,当I_rx_en为1时主机才能从从机接收数据;

I_data_in是主机要发送的并行数据;

O_data_out是把从机接收回来的串行数据并行化以后的并行数据;

O_tx_done是主机给从机发送数据完成的标志位,发送完成后会产生一个高脉冲;

O_rx_done是主机从从机接收数据完成的标志位,接收完成后会产生一个高脉冲;

I_spi_miso、O_spi_cs、O_spi_sck和O_spi_mosi是标准SPI总线协议规定的四根线;

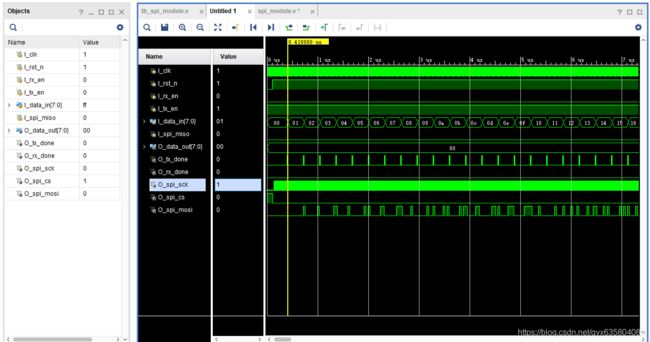

完整代码如下:

module spi_module

(

input I_clk,//系统时钟50MHz

input I_rst_n,//复位信号,低电平有效

input I_rx_en,//读使能信号

input I_tx_en,//发送使能信号

input [7:0] I_data_in,//要发送的数据

output reg [7:0] O_data_out,//接收到的数据

output reg O_tx_done,//发送一个字节完毕标志位

output reg O_rx_done,//接收一个字节完毕标志位

//四线标准SPI信号定义

input I_spi_miso,//SPI串行输入,用来接收从机数据

output reg O_spi_sck, //SPI时钟

output reg O_spi_cs, //SPI片选信号

output reg O_spi_mosi //SPI输出,用来给从机发数据

);

reg [3:0] R_tx_state ;

reg [3:0] R_rx_state ;

always @(posedge I_clk or negedge I_rst_n)

begin

if(!I_rst_n)

begin

R_tx_state <= 4'd0 ;

R_rx_state <= 4'd0 ;

O_spi_cs <= 1'b1 ;

O_spi_sck <= 1'b0 ;

O_spi_mosi <= 1'b0 ;

O_tx_done <= 1'b0 ;

O_rx_done <= 1'b0 ;

O_data_out <= 1'b0 ;

end

else if(I_tx_en)//发送使能信号打开

begin

O_spi_cs <= 1'b0;//把片选拉低

case(R_tx_state)

4'd1,4'd3,4'd5,4'd7,4'd9,4'd11,4'd13,4'd15: //奇数状态

begin

O_spi_sck <= 1'b1;

R_tx_state <= R_tx_state + 1'b1;

O_tx_done <= 1'b0;

end

4'd0://发送第7位

begin

O_spi_mosi <= I_data_in[7] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd2://发送第6位

begin

O_spi_mosi <= I_data_in[6] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd4://发送第5位

begin

O_spi_mosi <= I_data_in[5] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd6://发送第4位

begin

O_spi_mosi <= I_data_in[4] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd8://发送第3位

begin

O_spi_mosi <= I_data_in[3] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd10://发送第2位

begin

O_spi_mosi <= I_data_in[2] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd12://发送第1位

begin

O_spi_mosi <= I_data_in[1] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b0 ;

end

4'd14://发送第0位

begin

O_spi_mosi <= I_data_in[0] ;

O_spi_sck <= 1'b0 ;

R_tx_state <= R_tx_state + 1'b1 ;

O_tx_done <= 1'b1 ;

end

default:R_tx_state <= 4'd0 ;

endcase

end

else if(I_rx_en)//接收使能信号打开

begin

O_spi_cs <= 1'b0;//把片选拉低

case(R_rx_state)

4'd0,4'd2,4'd4,4'd6,4'd8,4'd10,4'd12,4'd14:

begin

O_spi_sck <= 1'b0 ;

R_rx_state <= R_rx_state + 1'b1;

O_rx_done <= 1'b0 ;

end

4'd1://接收第7位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[7] <= I_spi_miso ;

end

4'd3: // 接收第6位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[6] <= I_spi_miso ;

end

4'd5: // 接收第5位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[5] <= I_spi_miso ;

end

4'd7: // 接收第4位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[4] <= I_spi_miso ;

end

4'd9: // 接收第3位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[3] <= I_spi_miso ;

end

4'd11: // 接收第2位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[2] <= I_spi_miso ;

end

4'd13: // 接收第1位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b0 ;

O_data_out[1] <= I_spi_miso ;

end

4'd15: // 接收第0位

begin

O_spi_sck <= 1'b1 ;

R_rx_state <= R_rx_state + 1'b1 ;

O_rx_done <= 1'b1 ;

O_data_out[0] <= I_spi_miso ;

end

default:R_rx_state <= 4'd0 ;

endcase

end

else

begin

R_tx_state <= 4'd0 ;

R_rx_state <= 4'd0 ;

O_tx_done <= 1'b0 ;

O_rx_done <= 1'b0 ;

O_spi_cs <= 1'b1 ;

O_spi_sck <= 1'b0 ;

O_spi_mosi <= 1'b0 ;

O_data_out <= 8'd0 ;

end

end

endmodule

testbench文件

`timescale 1ns / 1ps

module tb_spi_module;

// Inputs

reg I_clk;

reg I_rst_n;

reg I_rx_en;

reg I_tx_en;

reg [7:0] I_data_in;

reg I_spi_miso;

// Outputs

wire [7:0] O_data_out;

wire O_tx_done;

wire O_rx_done;

wire O_spi_sck;

wire O_spi_cs;

wire O_spi_mosi;

// Instantiate the Unit Under Test (UUT)

spi_module tb_uut(

.I_clk (I_clk),

.I_rst_n (I_rst_n),

.I_rx_en (I_rx_en),

.I_tx_en (I_tx_en),

.I_data_in (I_data_in),

.O_data_out (O_data_out),

.O_tx_done (O_tx_done),

.O_rx_done (O_rx_done),

.I_spi_miso (I_spi_miso),

.O_spi_sck (O_spi_sck),

.O_spi_cs (O_spi_cs),

.O_spi_mosi (O_spi_mosi)

);

initial begin

// Initialize Inputs

I_clk = 0;

I_rst_n = 0;

I_rx_en = 0;

I_tx_en = 1;

I_data_in = 8'h00;

I_spi_miso = 0;

// Wait 100 ns for global reset to finish

#100;

I_rst_n = 1;

end

always #10 I_clk = ~I_clk ;

always @(posedge I_clk or negedge I_rst_n)

begin

if(!I_rst_n)

I_data_in <= 8'h00;

else if(I_data_in == 8'hff)

begin

I_data_in <= 8'hff;

I_tx_en <= 0;

end

else if(O_tx_done)

I_data_in <= I_data_in + 1'b1 ;

end

endmodule