FPGA开始学习verilog、vivado HLS

哎,可能要将算法搞到FPGA上去了,而作为一个FPGA小白,感觉好像很难的样子。于是开始了解这些:

一、step1 安装和HLS

1、在ubuntu下下载安装vivado:https://blog.csdn.net/wmyan/article/details/78926324 安装时会叫你选择哪个Edition,记住选择第三个(第三个才有HLS),然而第二个即Design Edition的介绍说包含了HLS,狗屁,装完根本没有HLS!试了几个安装包都没有!要用HLS一顶要选择第三个!安装完后会需要license文件,直接去CSDN上下载合适点license文件不要在官网买,然后放在/HOME/下,再license窗口的左侧load license 点copy license就行啦。(我装的是包含vivado HLS的,因为想做硬件加速)

事实证明,选第几个都没有找到HLS!崩溃!为什么就没有一个详细的教程说vivado HLS怎么装呢?倒是有一大把vivado怎么装。

问题已经解决:原来并不是选择第几个Edition的问题,其实之前我都装成功了,只是不要在/opt/xilinx/下去找HLS,而要去应用那里找,找到后启动即可!!!

邮件点击这个图标,将它锁定在任务栏,就可以像eclipse一样方便打开了!

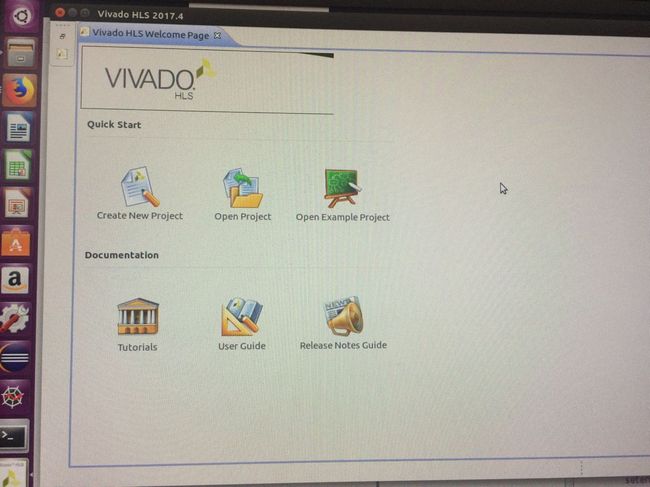

后来我是按照 https://blog.csdn.net/w371500241/article/details/53282859 这位大神的体验了一下,感觉真的很方便!他用的是自己写的c程序,我用的是安装目录下example里的文件:

真是太方便了!eclipse的界面,有种他乡遇故知的感觉!泪流满眶。

真是太方便了!eclipse的界面,有种他乡遇故知的感觉!泪流满眶。

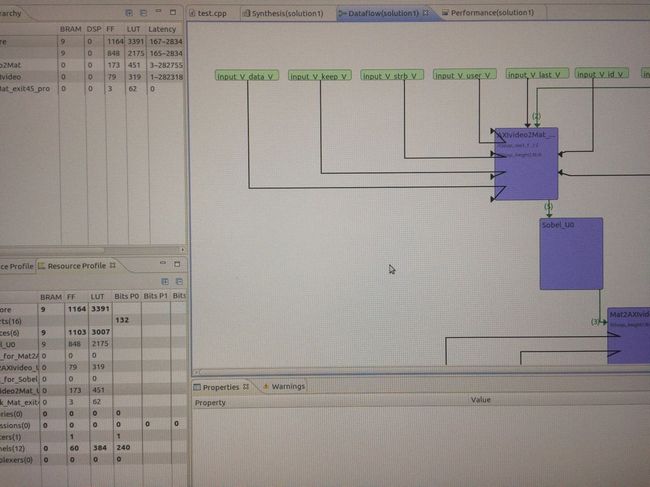

实现https://blog.csdn.net/long_fly/article/details/78839543仿真时报错:csim.exe:/error while loading libjpeg.so.62,解决办法:sudo apt-get install libjpeg62 ;如果出现少libtiff.so.3找不到,那么直接将电脑里原有的libtiff.so.不管版本是几,软链接为我们缺少的3即可。运行成功后:

按照他的步骤感受下仿真、综合、查看这些数据、生成IP核与查看生成好的verilog代码!

按照他的步骤感受下仿真、综合、查看这些数据、生成IP核与查看生成好的verilog代码!

好神奇。

另外发现vivado HLS2017.4这个版本里面的opencv是2.4.5这样老的版本,等有时间我准备将它换到opencv3.4.1。

暂时跟着 https://download.csdn.net/download/wd1603926823/10462911 这个资料学习实践。

以上可以了解Vivado HLS 的使用和开发流程、用HLS做仿真综合验证,还可以学习到怎么设计怎么约束更加优化!以及生成IP核给vivado使用!

/************************************************************************************************************/

二、step2 数据获取与使用

然而今天知道原来还要了解怎么从X86的PC端获取图像数据给开发板的PCIE端口,然后在vivado中得到这些图像数据给IP核使用,并返回算法给X86!

因为我没有FPGA基础,所以买的FPGA开发板的卖家告诉我要把下面这些框中的地方学完:

然后因为这块开发板的例子中有三个配套的摄像头,所以了解一种摄像头即可:

这些框中的部分都要学完。

学完这些再说!!

**************************************在学中.....

卖家给的这个第一季的视频里 S01_CH03_USB_JTAG使用.mp4 这个讲了怎么通过下载器下载程序到FPGA开发板跑起来。

第一季视频中的 S01_CH07_FPGA_RunLED.mp4 这个讲了跑LED流水灯的例子,如果生成.bit文件,从vivado下载到开发板跑起来。

带着痛苦看了两季........最后还是决定先看 《ug1270-vivado-hls-opt-methodology-guide.pdf》

************************************************************************************

以下是verilog的学习!

2、跟着 https://blog.csdn.net/jzj1993/article/category/3185349 在vivado上进行仿真。

3、下载了Verilog HDL入门资料 https://download.csdn.net/download/pingdangjun/9434439 。有时间时根据第一本书一边看一边在vivado上仿真。