SDRAM工作原理及S3C2410 SDRAM控制器配置方法(2)

SDRAM工作原理及S3C2410 SDRAM控制器配置方法(2)

转载自:http://www.embedu.org/Column/Column169.htm

作者: 刘洪涛, 华清远见嵌入式学院 讲师。

四、S3C2410 SDRAM控制器的配置方法

在 系统使用SDRAM之前,需要对S3C2410X的存储器控制器进行初始化。其中对与SDRAM(Bank6)相关的寄存器进行了特殊的设置,以使 SDRAM能够正常工作。由于C语言程序使用的数据空间和堆栈空间都定位在SDRAM上,因此,如果没有对SDRAM(Bank6)的正确初始化,系统就 无法正确启动。下面介绍与SDRAM相关的寄存器设置。

1、BWSCON寄存器

BWSCON 寄存器主要用来设置外接存储器的总线宽度和等待状态。在BWSCON中,除了Bank0,其他7个bank都各对应4个相关位的设置,分别为 STn,WSn和DWn。这里只需要对DWn进行设置,例如SDRAM(Bank6)采用32位总线宽度,因此,DW6=10,其他2位采用缺省值。 BWSCON寄存器在Bank6上的位定义如表4-1所示。

表4-1 BWSCON寄存器在Bank6上的位定义

| BWSCON |

位 |

描述 |

初始化状态 |

| ST6 |

27 |

这个位决定SRAM在Bank6上是否采用UB/LB |

0 |

| WS6 |

26 |

这个位决定Bank6的WAIT状态 |

0 |

| DW6 |

25~24 |

这2位决定Bank6的数据总线宽度 |

0 |

2、BANKCONn寄存器的设置

S3C2410X 有8个BANKCONn寄存器,分别对应着Bank0~Bank7。由于Bank6~Bank7可以作为FP/EDO/SDRAM等类型存储器的映射空 间,因此与其他bank的相应寄存器有所不同,其中MT位定义了存储器的类型。BANKCONn寄存器在Bank6和Bank7上的位定义如表4-2所 示。

表4-2 BANKCONn寄存器在Bank6和Bank7上的位定义

| BANKCONn |

位 |

描述 |

起始状态 |

| MT |

16~15 |

这2位决定了Bank6和Bank7的存储器类型 |

11 |

MT的取值又定义该寄存器余下几位的作用。当MT=11(即SDRAM型存储器)时,BANKCONn寄存器余下的几位定义如表4-3所示。

表4-3 BANKCONn寄存器在MT=11时的相关位定义

Trcd是从行使能到列使能的延迟,根据S3C2410X的HCLK频率(100M)及HY57V561620T-H的特性(见下图),此项取01,即3CLKS。SCAN为列地址线数量,此项根据HY57V561620特性取01,即9位(A0~A8)。

3 、REFRESH 寄存器

REFRESH寄存器是DRAM/SDRAM的刷新控制器。位定义如表4-4所示。

表4-4 REFRESH寄存器位定义

4 .BANKSIZE 寄存器

表4-5 BANKSIZE寄存器定义

| BANKSIZE |

位 |

描述 |

初始状态 |

| BURST_EN |

[7] |

ARM 内核猝发操作使能 |

0 |

| 保留 |

[6] |

不使用 |

0 |

| SCKE_EN |

[5] |

SCKE 使能控制 |

0 |

| SCLK_EN |

[4] |

只有在SDRAM访问周期期间,SCLK才使能,这样 |

0 |

| 保留 |

[3] |

未用 |

0 |

| BK76MAP |

[2:0] |

BANK6/7的存储空间分布 |

010 |

初始化时,BURST_EN可以取0或1,为了提高效率,最好设置为1。SCKE_EN设置为1。SCLK_EN设置为1。BK76MAP设置为2。

5、MRSR寄存器

MRSR寄存器有2个,分别对应MRSRB6和MRSRB7,对应着Bank6和Bank7。见表4-6。

表4-6 MRSRn寄存器定义

此寄存器S3C2410只允许CL可以设置,参照HY57V561620T-H手册,取011,即3CLKs。

猝发长度的具体值在程序中没有给出,根据后面触发时序猜测应该是8,HY57V561620T支持1、2、4、8、page猝发长度。

参照前面的HY57V561620命令表,写Mode寄存器用的是Mode register命令。其中的OP CODE参照下图:

注意:当代码在SDRAM中运行时,绝不能够重新配置MRSR寄存器。

五、SDRAM的控制时序分析

下面列出SDRAM的状态机及几种SDARM控制命令的时序。大家掌握了以后可以试着分析其它的命令时序。

1、SDRAM的状态机

SDRAM的完整状态机由多个状态构成,且状态转移是非随机的(如图5-1所示)。

正是如此众多的状态及其复杂的转换关系,导致SDRAM的控制较为复杂。通常FPGA开发人员在设计SDRAM控制器IP时需要详细了解这些状态机的过程。而一般开发人员以了解为主。

图5-1 SDRAM状态机

下面将结合上图及SDRAM的指令来分析SDRAM的控制时序

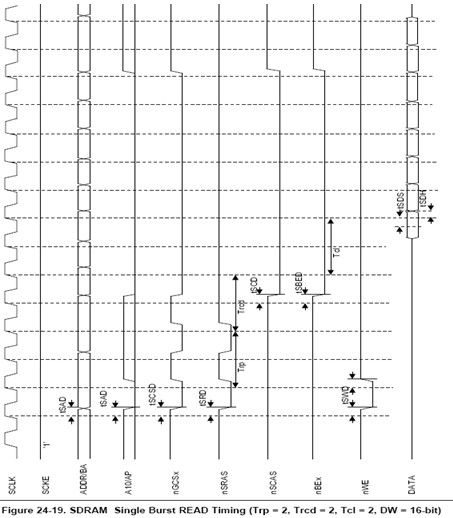

2、SDRAM single模式读时序

SDRAM初始化主要是由设置S3C2410 SDRAM控制器的模式寄存器(MRSR)完成的。主要设定了SDRAM的burst长度、CAS延时时间、突发类型等。然后就可以进行读写操作了。

下图是S3C2410以single方式读SDRAM时的时序。

对照HY57V5620的命令表,列出single read 命令实现过程。

| CLK |

SCKE |

A10/AP |

nGCSx |

nSRAS |

nSCAS |

nWE |

命令 |

备注 |

| 1 |

1 |

X |

1 |

1 |

1 |

1 |

空操作(NOP) |

|

| 2 |

1 |

0 |

0 |

0 |

1 |

0 |

预充电选定bank(PRE) |

Trp=2 |

| 3 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 4 |

1 |

X |

0 |

0 |

1 |

1 |

Bank激活命令(ACT) |

Trcd=2 |

| 5 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 6 |

1 |

0 |

0 |

1 |

0 |

1 |

读操作(READ) |

Tcl=3 |

| 7 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 8 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 9 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

数据有效 |

3、SDRAM burst模式读时序

对照HY57V5620的命令表,列出burst read 命令实现过程。

| CLK |

SCKE |

A10/AP |

nGCSx |

nSRAS |

nSCAS |

nWE |

命令 |

备注 |

| 1 |

1 |

X |

1 |

1 |

1 |

1 |

空操作(NOP) |

|

| 2 |

1 |

0 |

0 |

0 |

1 |

0 |

预充电选定bank(PRE) |

Trp=2 |

| 3 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 4 |

1 |

X |

0 |

0 |

1 |

1 |

Bank激活命令(ACT) |

Trcd=2 |

| 5 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 6 |

1 |

0 |

0 |

1 |

0 |

1 |

读操作(READ) |

Tcl=2 |

| 7 |

1 |

0 |

0 |

1 |

0 |

1 |

读操作(READ) |

|

| 8~13 |

1 |

0 |

0 |

1 |

0 |

1 |

读操作(READ) |

数据有效 |

| 14~15 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

数据有效 |

4、SDRAM Self Refresh时序

SDRAM 的Self Refresh功能在电源电源管理时经常使用,如:在主控器进入sleep状态时,会先让SDRAM工作在Self Refresh状态。下图为S3C2410发出Self Refresh命令时的时序图。

对照HY57V5620的命令表,列出进入Self Refresh的过程。

| CLK |

SCKE |

A10/AP |

nGCSx |

nSRAS |

nSCAS |

nWE |

命令 |

备注 |

| 1 |

1 |

X |

1 |

1 |

1 |

1 |

空操作(NOP) |

|

| 2 |

1 |

1 |

0 |

0 |

1 |

0 |

预充电所有bank(PRE) |

Trp=2 |

| 3 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 4 |

0 |

X |

0 |

0 |

0 |

1 |

Self Refresh命令(REFS) |

结合CKE的真值表 |

| 5 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

5、S3C2410 BUS Request时SDRAM控制时序

我 以前在做一个项目时涉及到两个主控器共享一个SDRAM的情况。现象是另一个主控器可以通过BUS Request功能获取到总线的控制权。当S3C2410的总线控制权被获取后,SDRAM控制不会再发出控制时钟信号。但SDRAM并没有因为失去时钟 而丢失数据。猜想一定是S3C2410在BUS Request时让SDRAM进入自刷新状态(就和S3C2410睡眠前要让SDRAM进入自刷新状态一样)、POWER DOWN状态、或者SUSPEND状态。下面就根据S3C2410 BUS Request时SDRAM控制时序图去确认一下到底是哪种。

对照HY57V5620的命令表,列出S3C2410 BUS Request时SDRAM时序过程。

| CLK |

SCKE |

A10/AP |

nGCSx |

nSRAS |

nSCAS |

nWE |

命令 |

备注 |

| 1 |

1 |

X |

1 |

1 |

1 |

1 |

空操作(NOP) |

|

| 2 |

1 |

0 |

0 |

0 |

1 |

0 |

预充电(PRE) |

Trp=2 |

| 3 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 4 |

1 |

X |

0 |

0 |

1 |

1 |

Bank激活命令(ACT) |

Trcd=2 |

| 5 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 6 |

1 |

0 |

0 |

1 |

0 |

1 |

读操作(READ) |

Tcl=2 |

| 7 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 8 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 9 |

1 |

X |

1 |

1 |

1 |

1 |

空操作 |

|

| 10 |

HZ |

HZ |

HZ |

HZ |

HZ |

HZ |

进入Clock suspend |

Note 1 |

Note1: 在第10个时钟周期时,SKE从1变为’HZ’(高阻)。我想此时SCKE从1变为高阻对于SDRAM来说相当于从1->0吧,看了一遍 HY57V5620手册,这个想法没有得到确认。但也只能这么理解了,不然后面都说不通了。我想之所以变为高阻而不是低电平,是因为S3C2410要放弃 自己对总线控制。

结合HY57V5620手册分析一下此时SDRAM会进入什么状态。

下图是CKE Enable(CKE) 真值表。

在第10个时钟周期时,SDRAM处于行激活状态。此时SCKE由1->0, 根据真值表可以得出系统会进入Clock suspend状态

六、总结

本文分析了SDRAM的工作原理、介绍了HY57V561620及其与S3C2410的接线原理、S3C2410 SDRAM控制器的配置方法、及部分SDRAM的控制时序分析。有些地方理解的不够深刻,欢迎大家指正。