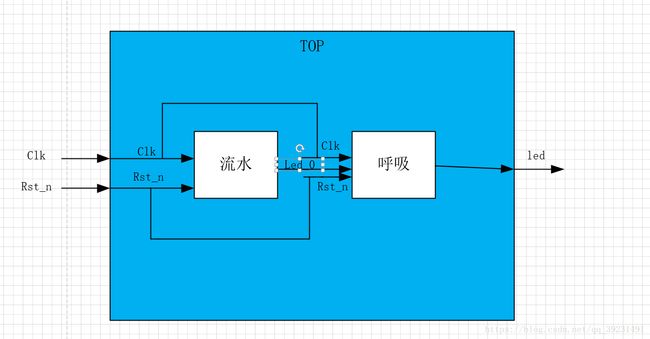

top down 的写法之流水呼吸灯综合

流水灯的编写:

module liushui1(

input wire clk ,

input wire rst_n ,

output reg[3:0] led

);

reg[26:0] cnt_s;

reg flag ;

parameter CNT_MAX=100000000-1;

//cnt_s

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt_s <= 0;

else if(cnt_s==CNT_MAX)

cnt_s <= 0;

else

cnt_s <= cnt_s +1;

//flag

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag <= 0;

else if(led==4’b1000)

flag <= 1;

else if(led==4’b0001)

flag <= 0;

//led

always@(posedge clk or negedge rst_n)

if(rst_n==0)

led <= 4’b0001;

else if(flag==0&&cnt_s==CNT_MAX)

led <= {led[2:0],led[3]};

else if(flag==1&&cnt_s==CNT_MAX)

led <= {led[0],led[3:1]};

endmodule

呼吸灯:

module huxi1(

input wire clk ,

input wire rst_n,

input wire[3:0] led_o,

output reg[3:0] led

);

reg[5:0] cnt_us;

reg[9:0] cnt_ms;

reg[9:0] cnt_s ;

reg flag ;

reg flag_cnt_us;

reg flag_cnt_ms;

reg flag_cnt_s ;

parameter CNT_US_MAX = 49;

parameter CNT_MS_MAX = 999;

parameter CNT_S_MAX = 999;

//cnt_us

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt_us <= 0;

else if(cnt_us==CNT_US_MAX )

cnt_us <= 0;

else

cnt_us <= cnt_us + 1;

//flag_cnt_us

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag_cnt_us <= 0;

else if(cnt_us==CNT_US_MAX )

flag_cnt_us <= 1;

else

flag_cnt_us <= 0;

//cnt_ms

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt_ms <= 0;

else if(cnt_ms==CNT_MS_MAX &&flag_cnt_us==1)

cnt_ms <= 0;

else if(flag_cnt_us==1)

cnt_ms <= cnt_ms + 1;

//flag_cnt_ms

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag_cnt_ms <= 0;

else if(cnt_ms==CNT_MS_MAX&&flag_cnt_us==1 )

flag_cnt_ms <= 1;

else

flag_cnt_ms <= 0;

//cnt_s

always@(posedge clk or negedge rst_n)

if(rst_n==0)

cnt_s <= 0;

else if(cnt_s==CNT_S_MAX &&flag_cnt_ms==1)

cnt_s <= 0;

else if(flag_cnt_ms==1)

cnt_s <= cnt_s + 1;

//flag_cnt_s

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag_cnt_s <= 0;

else if(cnt_s==CNT_S_MAX&&flag_cnt_ms==1 )

flag_cnt_s <= 1;

else

flag_cnt_s <= 0;

//flag

always@(posedge clk or negedge rst_n)

if(rst_n==0)

flag <= 0;

else if(flag_cnt_s==1 )

flag <= ~flag;

always@(posedge clk or negedge rst_n)

if(rst_n==0)

led <= 0;

else if(cnt_ms<=cnt_s&&flag==0)

led <= led_o;

else if(cnt_ms>cnt_s&&flag==0)

led <= 0;

else if(cnt_ms>=cnt_s&&flag==1)

led <= led_o;

else if(cnt_ms