DDR3学习之一 好用的学习资料

https://blog.csdn.net/u012923751/article/details/83241169 理解DDR

https://wenku.baidu.com/view/ac32c8bcf705cc1754270923.html Xilinx平台DDR3设计教程之仿真

https://wenku.baidu.com/view/2ffa1334783e0912a3162a26.html Xilinx平台DDR3设计教程之综合

https://max.book118.com/html/2018/0730/8023061102001116.shtm Xilinx平台DDR3设计教程之设计

https://blog.csdn.net/zhipao6108/article/details/81570681 理解DDR IP 核

https://wenku.baidu.com/view/63e8c92d195f312b3069a5ea.html 理解时序

学习DDR的时候首先要知道IP核怎么配置,然后就是用AXI 的应答机制怎么来控制读写。首先要把前面几个网址都看一遍,特别是DDR设计教程,还有一个应用,没有免费的,在CSDN账号上面有。

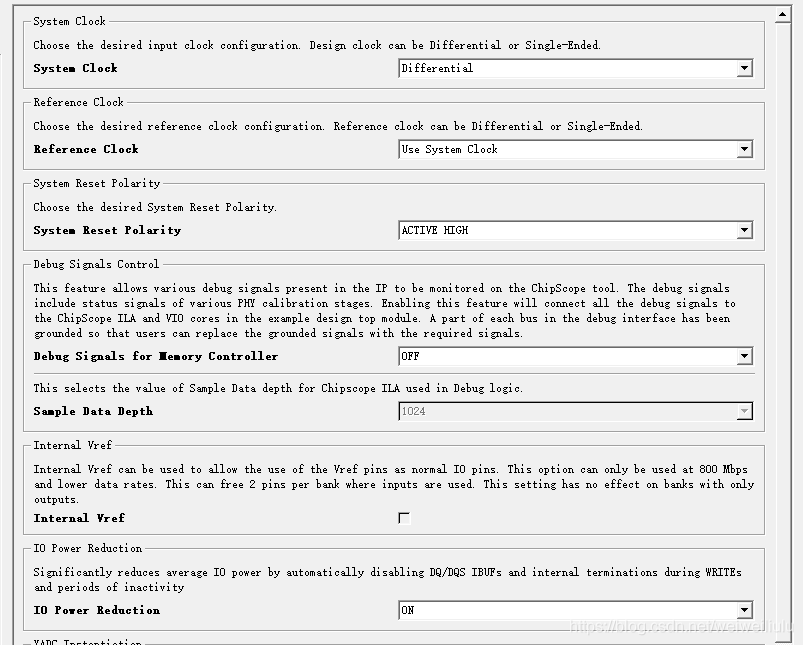

注意DDR IP 核输入时钟,可以是板子上的时钟,也可以是PLL 输出的时钟。但是需要注意,在使用锁相环输出时钟的时候,要把输出BUFG去掉。代码里,逻辑用的时钟,使用DDR IP 核产生的用户时钟。

DDR使用过程中,常用的是突发连续读写模式:只要指定起始地址和突发长度,后续的寻址与数据自行读写,只要控制好两段突发读取命令之间的间隔与突发长度相同即可。

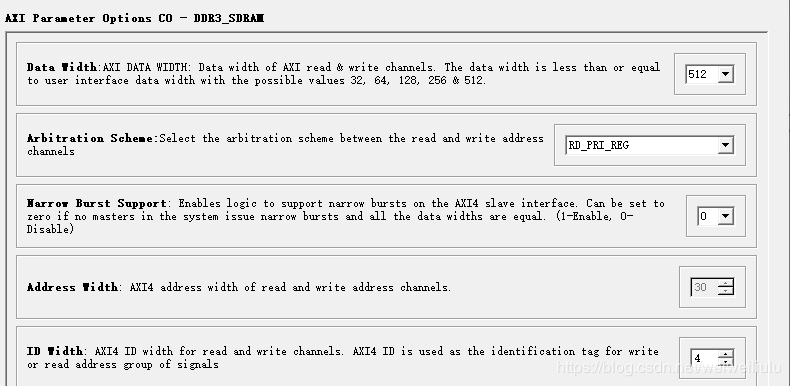

在很多博客中说到,突发长度是8 ,但是代码里写的是8192 ,有什么关系?突发长度8 是针对芯片底层来说,一次突发一个字节,8192是IP核层面使用的一个参数,设置8192的意思就是,一次突发8192个字节。这里和代码中的last 对应上,如果选择IP核数据位宽是256,那么(8192*8)/256 = 256。也就是数据通过AXI 一个时钟传输256bit的数据,一共传输256个时钟以后,产生一个last信号,表示当前突发完成。

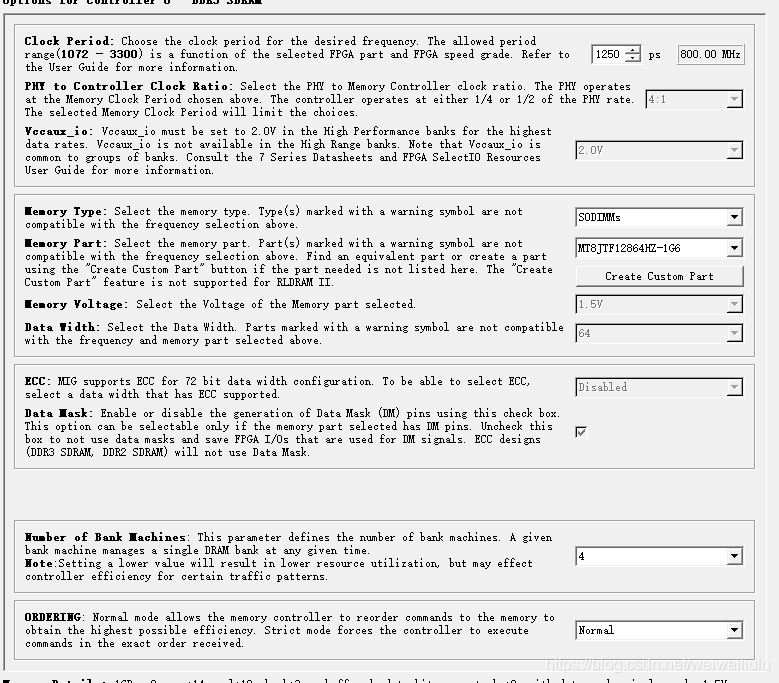

有关时钟核数据位宽的讨论,在我测试的代码中,DDR 3主频800MHZ,用户时钟可以进行4分频,或者2分频。IP核中选择800M 的时候默认是4分频,也就是200M ,即硬件输出的时钟是200M。IP核的数据位宽512bit,DDR芯片的数据位宽64bit,这怎么匹配的?

64* 2 * 4 = 512 (2 代表双沿触发,4代表倍频系数)。在更改DDR 内部配置的时候,也要遵从这样的一个原则,不能说是随意的更改。

DDR IP核配置可以按照上面链接中写的很详细,这里不再累赘,这里重点说一下DDR 一些IP核上的端口怎么配置。

1、我们要知道,自己的DDR 到底有没有工作。可以看下面几个信号:

sys_reset 是硬件输入复位信号,默认高,然后拉低。

aresetn 是IP核输入复位,低电平复位,aresetn = (~sys_reset);

app_reset 是IP核输出 默认高,拉低以后,表示内部复位完成。

init_calib_complete 拉高 表示初始化完成

mmcm_locked 拉高 表示内部锁相环锁存

上面几个信号正常说明DDR 已经工作,如果工作不正常,那就是DDR 状态机不对。DDR具体控制的状态机可以在本人上传资料中下载。一个简单的例程。配套上传资料中ddr.v的代码,IP核配置如下:

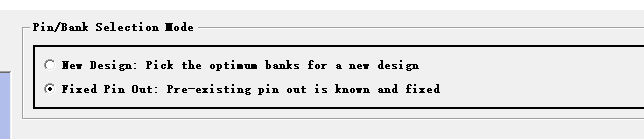

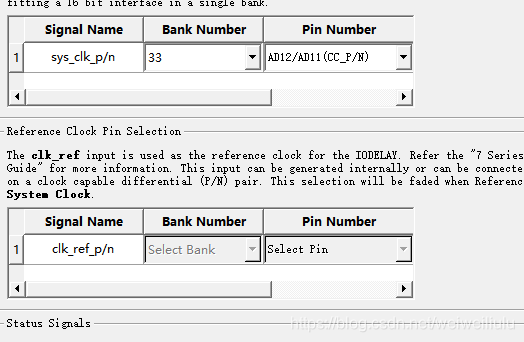

下一步引脚分配 一定要按照原理图对应清楚

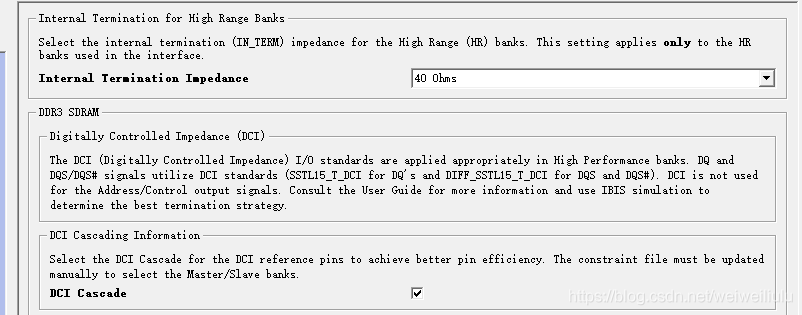

总结一下,IP核配置其实主要也就是关注主频时钟频率,分配系数,数据位宽,地址定义模式,输入时钟差分还是单端,引脚分配。这些只要没问题就不会错。当然如果是库里面没有的DDR3的模型,那就需要自己配置参数,看其他人配置过,貌似不太好弄,配错一个参数DDR就不工作