DDS正弦信号产生实验

正弦信号产生实验

实验目标

1.首先设计一个DDS, 50MHz的时钟速率,输出波形频率自行设定

2.DDS的输出数据格式为2补码,相位累加器32比特ROM波表尺寸和波形量化比特数自己决定

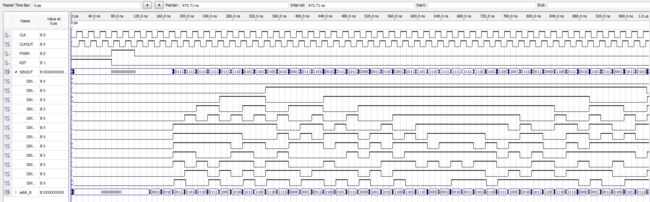

3.首先在Signaltap里,观察波形的正确性,然后把Signaltap的数据导入到Matlab,分析频域结果

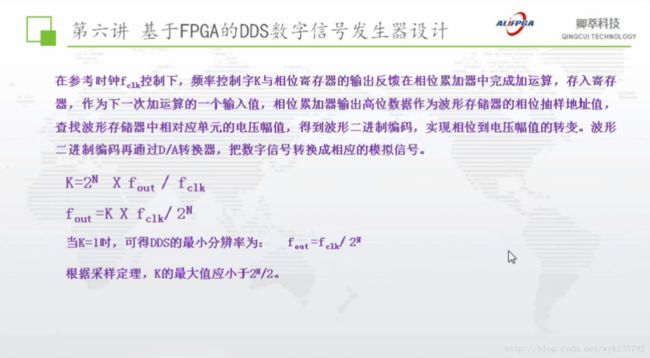

基础知识

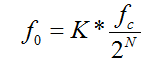

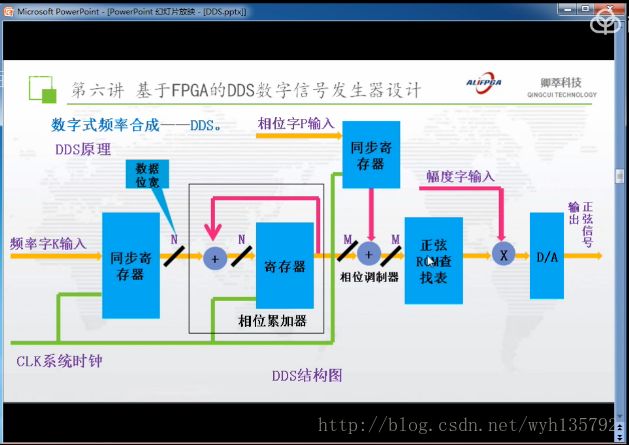

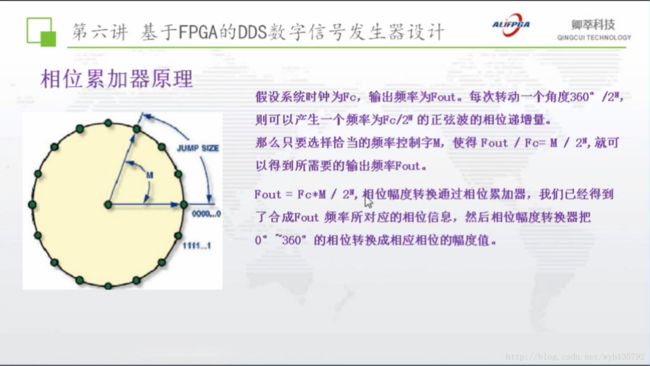

DDS的工作原理:输出频率由频率控制字决定,公式如下:

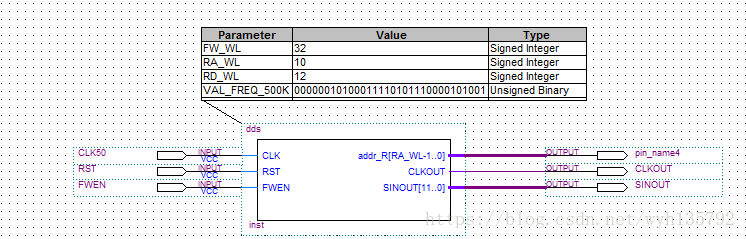

为输出频率,为时钟频率=50MHz,K为频率控制字,N为相位累加器的位数32。当输出频率500KHz,1MHz时,其对应的频率字分别为32’h028F_5C29、32’h028F_5C29 * 2,因此本实验中设定输出频率为500KHz。波形量化比特数为12bit,ROM波表尺寸为10bit地址。

实验代码:

module dds(

CLK , // clock, posedge valid

RST , // reset, high level reset

FWEN , // frequency word update enable, high level enable

//FWIN ,

addr_R, // input frequency word

CLKOUT, // output clock

SINOUT); // sine signal output, 2's complement format

input CLK;

input RST;

input FWEN;

//input [32-1:0] FWIN;

output [9:0] addr_R;

output[12-1:0] SINOUT;

output CLKOUT;

parameter FW_WL = 32; // frequency word word length in bit

parameter RA_WL = 10; // rom address word length in bit

parameter RD_WL = 12; // rom data word word length in bit

parameter VAL_FREQ_500K = 32'h028F_5C29;

reg [FW_WL -1:0] fwin_R; // freq word DFF

reg [FW_WL -1:0] acc_R; // phase ACC DFF

reg [RA_WL -1:0] addr_R; // rom address DFF

reg [RD_WL -1:0] sinout_R; // sin wave output DFF

wire [RD_WL -1:0] romout_W; // rom data output wire

always @ (posedge CLK or posedge RST) begin

if(RST) begin

fwin_R <= 0;

acc_R <= 0;

addr_R <= 0;

sinout_R <= 0;

end

else begin

// update fwin_R DFF

if(FWEN)

fwin_R <= #1 VAL_FREQ_500K;

else

fwin_R <= #1 fwin_R;

// update acc_R

acc_R <= #1 fwin_R + acc_R;

// update addr_R, the acc_R high RA_WL is rom address

addr_R <= acc_R[FW_WL-1:FW_WL-1-(RA_WL-1)];

// update output DFF

sinout_R <= #1 romout_W;

end

end

DDS_CORE_ROM u_sinrom(

.CLK (CLK ), // clock

.RA (addr_R ), // read address

.RD (romout_W )); // read data

assign SINOUT = sinout_R;

assign CLKOUT = CLK;

endmodule // module dds_core

DDS ROM波表实验代码:

module DDS_CORE_ROM(

CLK , // clock

RA , // read address

RD ); // read data

input CLK;

input [9 :0] RA;

output [11 :0] RD;

reg [11 :0] RD;

always @ (posedge CLK)

case(RA)

10'd 0 :RD = #1 12'b 000000000000; // 0 0x0

10'd 1 :RD = #1 12'b 000000001100; // 12 0xC

10'd 2 :RD = #1 12'b 000000011001; // 25 0x19

10'd 3 :RD = #1 12'b 000000100101; // 37 0x25

10'd 4 :RD = #1 12'b 000000110010; // 50 0x32

10'd 5 :RD = #1 12'b 000000111110; // 62 0x3E

10'd 6 :RD = #1 12'b 000001001011; // 75 0x4B

10'd 7 :RD = #1 12'b 000001010111; // 87 0x57

10'd 8 :RD = #1 12'b 000001100100; // 100 0x64

10'd 9 :RD = #1 12'b 000001110000; // 112 0x70

.........................

10'd 1017 :RD = #1 12'b 111110101001; // -87 0xFA9

10'd 1018 :RD = #1 12'b 111110110101; // -75 0xFB5

10'd 1019 :RD = #1 12'b 111111000010; // -62 0xFC2

10'd 1020 :RD = #1 12'b 111111001110; // -50 0xFCE

10'd 1021 :RD = #1 12'b 111111011011; // -37 0xFDB

10'd 1022 :RD = #1 12'b 111111100111; // -25 0xFE7

10'd 1023 :RD = #1 12'b 111111110100; // -12 0xFF4

default : RD = #1 0;

endcase

endmodule

matlab生成ROM波表实验代码:

function generate_DDS_rom()

clc;

close all;

disp('##########################################');

disp('# generate_DDS_rom() RUN');

disp('##########################################');

%%///

% set your rom config here

rom_word_len = 12; % rom data word length in bit

rom_addr_len = 10; % rom address word length in bit

rom_file_name = 'DDS_CORE_ROM.v'; % rom file name

rom_file_dir = './'; % rom file dir path

description = 'DDS CORE ROM FILE' % rom description

%%///

rom_vec_len = 2^rom_addr_len;

index = [0:rom_vec_len-1] .';

rom_data_vec_float = sin(2*pi*index/rom_vec_len);

figure; plot(rom_data_vec_float); % for debug

rom_data_vec_int = fix(rom_data_vec_float * (2^(rom_word_len-1) - 1));

figure; plot(rom_data_vec_int); % for debug

rom_cfg.rom_word_len = rom_word_len ;

rom_cfg.rom_file_name = rom_file_name ;

rom_cfg.rom_file_dir = rom_file_dir ;

rom_cfg.description = description ;

gen_rom_rtl(rom_cfg, rom_data_vec_int);

end % generate_DDS_rom()

% ///

% gen_rom_rtl()

% generate synthesizable rom hdl code(need synthesizer support).

% ///

% INPUT:

% data vector, must be integer value

% rom word len

% rom file dir string

% rom file name string

% OUTPUT:

% verilog format rom file, all data in 2's complement code format

function gen_rom_rtl(rom_cfg, data_vec);

rom_word_len = rom_cfg.rom_word_len ;

rom_file_name = rom_cfg.rom_file_name ;

rom_file_dir = rom_cfg.rom_file_dir ;

description = rom_cfg.description ;

data_vec_len = length(data_vec);

addr_word_len = ceil(log2(data_vec_len));

% check input be integer value

data_vec_fixed = fix(data_vec);

diff_sum = sum(data_vec == data_vec_fixed);

% all integer elements will cause the diff_sum be vector length

if(diff_sum < data_vec_len)

fprintf(1,'# ERROR, gen_rom_rtl(), input data_vec must be integer value\n');

return;

end

rom_file_dir_name = strcat(rom_file_dir, rom_file_name);

data_vec_fixed_2c = data_vec_fixed + (2^rom_word_len) .* (data_vec_fixed < 0);

romNum = 2^addr_word_len;

data_str_cell = cell(data_vec_len, 1);

for(idx = 1:data_vec_len)

data_str_cell{idx} = Dec2BinStr(data_vec_fixed_2c(idx), rom_word_len);

end % for(idx = 1:data_vec_len)

if(romNum > data_vec_len)

for(idx = data_vec_len+1:romNum)

data_str_cell{idx} = Dec2BinStr(0, rom_word_len);

end

end

fid_rom_file = fopen(rom_file_dir_name, 'w');

if(fid_rom_file == -1)

errMsg = strcat('ERROR, gen_rom_rtl(), create file',rom_file_dir_name, ',failed');

fprintf(1, '%s\n', errMsg);

return;

end

% rom data print

% get rom module name

rom_name = rom_file_name;

len_rom_file_name = length(rom_file_name);

if(rom_name(len_rom_file_name-1:len_rom_file_name) == '.v')

rom_name(len_rom_file_name-1:len_rom_file_name) = [];

else

fprintf(1,'#WARNINIG, gen_rom_rtl(), rom_file_name may error, check it!\n');

end

fprintf(fid_rom_file, ...

'// ************************************************************** //\n');

fprintf(fid_rom_file, ...

'// FILE : %s \n', rom_file_name);

fprintf(fid_rom_file, ...

'// DSCP : %s\n', description);

fprintf(fid_rom_file, ...

'// ABOUT : auto generated rom file by gen_rom_rtl.m\n');

fprintf(fid_rom_file, ...

'// DATE : %s \n', datestr(now));

fprintf(fid_rom_file, ...

'// ************************************************************** //\n');

% generate the crom module

fprintf(fid_rom_file, ...

'// module %s()\n', rom_name);

fprintf(fid_rom_file, ...

'module %s(\n', rom_name);

fprintf(fid_rom_file, ...

' CLK , // clock\n');

fprintf(fid_rom_file, ...

' RA , // read address\n');

fprintf(fid_rom_file, ...

' RD ); // read data\n');

fprintf(fid_rom_file, ...

'input CLK;\n');

fprintf(fid_rom_file, ...

'input [%-2d :0] RA;\n', addr_word_len-1);

fprintf(fid_rom_file, ...

'output [%-2d :0] RD;\n', rom_word_len-1);

fprintf(fid_rom_file, ...

'reg [%-2d :0] RD;\n', rom_word_len-1);

fprintf(fid_rom_file, ...

'always @ (posedge CLK)\n');

fprintf(fid_rom_file, ...

' case(RA)\n');

for addr = 0:1:data_vec_len-1

fprintf(fid_rom_file, ...

' %-2d''d %-6d:RD = #1 %-2d''b %s; ', ...

addr_word_len,addr, rom_word_len, data_str_cell{addr+1});

fprintf(fid_rom_file, ...

'// %6d 0x%s \n', ...

data_vec_fixed(addr+1), dec2hex(data_vec_fixed_2c(addr+1)));

end

fprintf(fid_rom_file, ...

' default : RD = #1 0;\n');

fprintf(fid_rom_file, ...

' endcase\n');

fprintf(fid_rom_file, ...

'endmodule \n');

fclose(fid_rom_file);

fprintf(1,'# File: %s written\n', rom_file_dir_name);

end % function gen_rom_rtl()

%

function str = Dec2BinStr(data, word_len)

str = '';

for(idx = word_len-1:-1:0)

bit_val = bitand(1, bitshift(data, -idx));

str = strcat(str, int2str(bit_val));

end

end % function Dec2BinStr()