Dynamic Partial Reconfiguration 3 Implementation of Audio Filter on Virtex-5

【内容原创,转载请说明】

【感谢LLJ学长白皮书的帮助】

先快速阅读完下面的参考资料(在Xilinx官网上有):

《16.a_audio_filter_lab6.pdf》

《PlanAhead_Tutorial_Reconfigurable_Processor12.3.pdf》

阅读完上面资料后,对动态可重构步骤有了一定的了解,但你并没有掌握它,因为里面还存在很多细节方面需要注意与学会,如果只是按照上面的参考资料最终也完成了动态可重构,也只是比较肤浅的。这里我选用XUPV5-LX110T板作为实验板,结合《16.a_audio_filter_lab6.pdf》对动态可重构流程进行详细的介绍。

实验介绍:

在这个实验中,你将使用Xilinx Platform Studio 工具去创建一个带处理器的系统。上层设计中定义了两个可重构区域,可重构区域都有几个可重构的模块(包括高通滤波器、低通滤波器、带阻滤波器、全通滤波器)。可以创建多种配置并且运行不同的部分可重构完成生成全部或者部分配置文件流,将使用XUPV5开发板去验证硬件设计,在验证中将用到CF卡完成FPGA的初始化配置。其中部分可重构是在软件控制端利用XPS HWICAP外设来加载配置文件的。

实验能达到的目标:

在完成了这个实验后,你将:

① 能利用Xilinx Platform Studio工具创建一个带处理器的系统

② 可以利用Create/Import Peripheral Wizard 工具创建一个外设

③ 可以把创建的外设加进到处理器系统中

④ 能够创建一个PlanAhead 的PR工程

⑤ 能在PlanAhead中创建各种配置文件,用来完成部分可重构

⑥ 运行部分可重构实现流程

⑦ 完成有两个可重构区域的、并且每个区域含有多个可重构模块的动态可重构设计

⑧ 生成部分可重构的配置文件流,以及system.ace文件(CF卡用于初始化FPGA的文件),并将它们放在CF存储卡中。

⑨ 用CF卡中的system.ace文件配置FPGA,并能在程序段利用软件控制其他配置文件流的调用。

实验顶层设计:

实验将采用XILINX公司提供的audio_filter工程进行,audio_filter工程中包含全通、带阻、高通和低通音频滤波器功能,能够各种不同的滤波需求,在实际应用中很广。本实验中带阻、高通和低通三种滤波器的相应参数如下表所示:

表:三种滤波器的相关参数说明

| 滤波器类型 |

参数说明 |

| 带阻 滤波器 |

采样频率:48.0kHz、Fpass1=1600Hz、Fstop1=3800Hz Fpass2=4200Hz、Fstop2=6400Hz、通带两侧衰减分贝为60 |

| 高通 滤波器 |

采样频率:48.0kHz、Fstop=3800Hz、Fpass=6200Hz 通带两侧衰减分贝为60 |

| 低通 滤波器 |

采样频率:48.0kHz、Fstop=4200Hz、Fpass=2000Hz 通带两侧衰减分贝为60 |

实验采用动态可重构技术,完成audio_filter工程中四种滤波器的功能变换;并划分两个可重构区域,实现双声道。实验流程如下图所示:

图:实验流程图

实验第一步是各个功能(全通、带阻、高通、低通滤波器)的实现,这一步是在ISE中工具中生成,由于工程中提供了相应功能的网表,因此这一步是直接借助已给的功能网表;第二步是硬件系统的搭建,这一步是在XPS工具中将所需要的各部分通过总线方式联系在一起,本实验中采用PLB v46总线,同时需要的部分有UART(串口通信,用于PC与FPGA开发板通信,观察实验效果)、System ACE(用于对CF卡进行控制,实现文件的读写)、AC97(用于音频的解码)、XPS HWICAP(用于可重构文件的加载),可重构区域采用顶层文件内加黑盒子的模式组成,控制器采用microblaze软核。第三步是软件控制,这一步在SDK中实现,UART、System ACE和XPS HWICAP工具中给出了相应控制函数,只需要调用相应API即可。可重构区域的划分和定义是在PlanAhead工具中完成。配置文件的生成也是在PlanAhead工具中完成,先是运行完各config,然后生成相应的bitstream文件。镜像文件的生成是在Bash Shell工具中生成的,通过相应的命令将bitstream文件转换成system.ace文件。具体每一步的过程,将在下面做详细的介绍。

实验流程:

第一步:硬件系统的搭建

在进行硬件系统的搭建之前先对audio_filter工程结构进行介绍:

在audio_filter工程文件夹下包含edk、image、image_solution、resource四个文件夹,edk文件夹用于硬件和软件部分工程存放,image文件夹用来存放生成的镜像文件,image_solution文件夹里存放了Xilinx公司已生成好的镜像文件,resources文件夹中存放了Xilinx公司提供的相关文件。resources文件夹下包含ac97的驱动、各功能滤波器的网表文件、audio_filter的IPcore、xps_ac97的IPcore、示例程序、ac97的管脚约束以及音频文件。

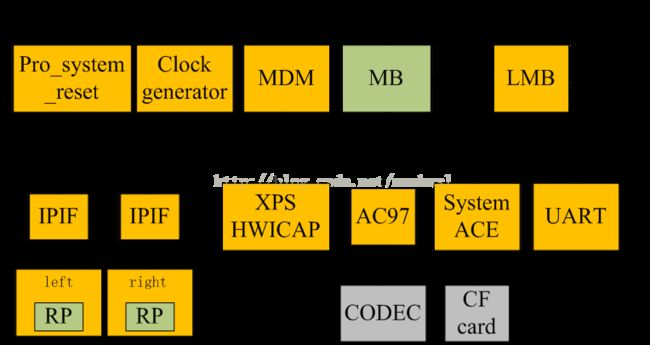

硬件体系架构如下图所示:

硬件系统搭建的具体步骤如下:

• 打开XPS工具,通过桌面相应图标或者是开始—>所有程序—>Xilinx Design Suite12.4—>Xilinx Platform Studio;

• 打开后按照默认的Base System Builder wizard,然后按OK;

• 这一步中将工程展开到edk文件夹下,会产生system.xmp文件,并保存,然后OK;

• 接下来是选择互连的总线类型,由于使用的XUPV5-LX110T不支持AXI协议,支持PLB协议,我们就选择PLB system(即默认类型),然后OK;

• 默认选择I would like to create a new design,然后Next;

• 这一步很重要,是关于芯片型号的选择;如果自己手上的板子是官方给出的经典板型,我们选择I would like to create a system for the following development board,然后在下面选择相应的型号;如果我们手上是不太大众的或者是第三方定制的开发板,那么我们选择I would like to create a system for a custom board,然后在下面选择相应的芯片型号即可,其它选项默认即可。由于本实验使用的是XUPV5-LX110T开发板,芯片是xc5vlx110t,经验证需选择I would like to create a system for a custom board这项,然后进行相应选择。对应选项Architecture—virtex5、Device—xc5vlx110t、Package—ff1136、Speed Grade— -1。然后Next。

• 这一步设置系统处理器个数,这里我选择Single-Processor System,即设置为单核系统。然后Next。

• 处理器的配置。将对应选项选择为,Reference Clock Frequency=100MHz,System Clock Frequency=100MHz,Local Memory=64KB,由于此型号芯片只支持软核MicroBlaze,所以就选择MicroBlaze,其它选项默认。然后Next。

• 添加外设。由于实验中需要通过超级终端来控制程序端运行,因此我们需要添加外设RS232_Uart然后由于需要对CF卡进行操作,所以也要添加外设SysACE_CompactFlash,另外默认自带dlmb_cntlr和ilmb_cntlr。在左侧的Available Peripherals中点击Add Device,弹出一个面板,在IO Interface Type中选择UART,再在Device下选择RS232;可以在右侧看到RS232_Uart已经添加了,这时我们需要对其进行设置,这里只需要修改比特率就可以了(Baud Rate=115200),其他默认。按照上述方法,添加SysACE_CompactFlash,不需要做任何修改。然后Next—>Next—>Next—>Finish,这时会弹出一个Running Design的面板,点击OK。

• 电脑屏幕中间弹出The Next Step面板,只需点击OK(即选择了默认的Start using Platform Studio),弹出了System Assembly View界面。

• 展开audio_filter文件夹目录,在resources—>pcores_repository中看到有audio_filter_v1_00_a和xps_ac97_v1_00_a文件,其中audio_filter_v1_00_a文件时音频滤波器的IP核,xps_ac97_v1_00_a文件是ac97解码器的IP核,将这两个IP核拷贝到edk下面的pcores目录下。

• 回来System Assembly View界面,将左侧部分选择为IP Catalog,然后在菜单栏中选择Project—>Rescan User Repositories,会发现左侧Project Local PCores中USER下面已经有了刚才加到pcores目录下的IP核。

• 展开Project Local PCores下USER,将XPS_AC97右键Add IP加入到系统中,将AUDIO_FILTER右键加两次到系统中,因为设计中左右声道都要。另外由于需要可重构,需要添加ICAP,找到FPGA Reconfiguration,展开选中FPGA Internal Configuration Access Port,右键Add IP,将其添加进系统中。

• 在System Assembly View右侧中选择Bus Interfaces。将上一步加入的两个audio_filter分别命名为left_filter和right_filter.

• 展开left_filter、right_filter、xps_ac97_0、xps_hwicap_0,并分别在后面的下拉框中选择mb_plb;将其分别连在mb_plb上(即通过plb总线连接microblaze软核),如下图所示:

• 选择Addressers标签栏,并点击Generate Addresses,这样就为各个模块分配了地址空间。由于在之前的设置中,我们设置了每个模块地址空间大小为64K,如果觉得这个地址空间大了,可以进行相应的修改。

• 在System Assembly View视图下,选择Ports标签。

• 展开xps_hwicap_0,将其中的ICAP_Clk选择为clk_100_0000MHz;展开xps_ac97_0,将AC97Reset_n、Bit_Clk、Sync、SData_Out、SDate_In设置为Make External,因为这几个音频接口是与外围的AC97芯片相连,是顶层部分。

• 完成以上部分后这里还需要管脚约束设置。这时,工程视图左侧中选择Project选项(之前是IP Catalog选项),点击其中的UCF File:data/system.ucf,打开后我们可以看到已经对应给出了部分相应的引脚连接模板,这里我们只需要把对应引脚标号加进去即可。修改后的system.ucf文件见附录(不同的芯片引脚连接是不同的):

• 修改完system.ucf后,点击菜单栏的Hardware—>Generate Netlist,这时就会生成对应的硬件网标(netlist),这个过程要花上几分钟,当console框中出现“NGCBUILD done. Done!”时说明netlist生成正确。

• 生成了netlist之后,有过FPGA方面经验的人或许会觉得下一步就是生成bitstream(硬件配置文件)了,也就是下一步Hardware—>Generate Bitstream;这是不对的,并且最终一定产生错误。为什么呢?因为我们这里是可重构,即left_filter和right_filter都是做成了黑盒子,在Xilinx ISE套件中含黑盒子是无法正常生成硬件配置文件的。所以,我们这里还没有真正的完成硬件部分,还需要对可重构部分加入相应模块后才能生成bitstream,这一步是在PlanAhead中的工作了。

• 下一步就是要进行基于上面过程中生成的netlist的软件设计了,在软件部分主要就是怎么去控制和调配各个模块如何工作。选择菜单栏中Project—>Export Hardware Design to SDK,弹出一个面板,选择Export & Launch SDK(将Include bitstream and BMM file前框框内默认的钩去掉)。

第二步:软件控制端的实现

• 这时进入了Software Development Kit(SDK)界面,首先需要新建一个板子支持的包,在包上运行相应的控制程序。选择File—>New—>Xilinx Board Support Package。

• 弹出的面板,选项默认不动,Finish。

• 这里选择standalone包,这个包能完成基本的操作;然后这里我们选择xilfatfs文件系统,这个文件系统支持FAT16/32文件格式,并且提供了一套相应的API,让程序控制变得很简单。选择完xilfatfs后,点击OK。

• 注意到这时生成了system.mss文件,这个文件中给出了RS232、SysACE、icap等相应部件的API,我们可以点击后面的Documentation 查看相应外设的说明,以及相应的函数说明。

• 这一步是导入之前完成的AC97驱动文件。

• 在Project Explore中选择standalone_bsp_0,右键,选择New—>C Project,填入Project name,这里我命名为TestApp,然后Finish。

• 这一步是导入控制程序,在TestApp中导入audio_filter\resources\TestApp\src文件夹,并勾选src,点击Finish。导入后IDE会显示错误,这里是工具的bug,这里只需要右键TestApp,然后选择Change Referenced BSP,选择其中的standalone_bsp_0,这时错误基本消除;但main.c中依然出现一个问题,需要将main.c中XPAR_RS232_UART_1_BASEADDR标示符全部替换成XPAR_RS232_BASEADDR,这样后就没有错误了,然后编译整个工程,这样程序段的模块控制程序就完成了,在audio_filter\edk\SDK\SDK_Workspace_35\TestApp\Debug文件夹中生成TestApp.elf文件。

• 程序的修改将在测试方案中根据需要修改。

• 选择Xilinx Tools—>Generate linker script,修改Heap和Stack大小为2048,点击Generate,然后点击Yes重新编译一遍工程。这样软件部分就完成了。

第三步:可重构区域的划分和定义

在第一步,已经生成了硬件系统的网表文件,但是里面存在blackbox,blackbox是用来搭载可重构modular。这一步我们将对blackbox进行modular指定,完善硬件。这一步将生成全配置及部分配置文件。具体步骤如下:

• 打开PlanAhead

• 新建工程,在New Project Design Source界面,选择Specify synthesized (EDIF or NGC) netlist,并选择Set PR Project选项,然后点击Next。注意:你这一步或许没有出现SetPR Project选项,说明你没有可重构的license。

• Top Netlist File选择audio_filter\edk\implementation中system.ngc文件,Next。

• Constraint 文件选择页面中选择audio_filter\edk\data中system.ucf,Next。

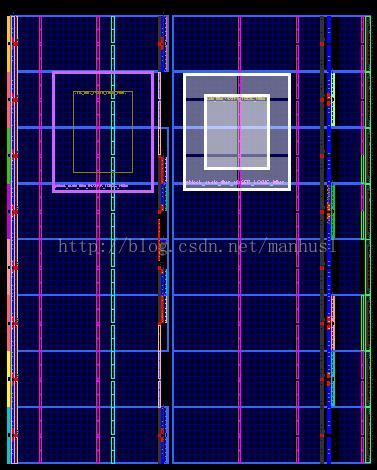

• 在芯片型号选择页面选择xc5vlx110tff1136-1,Next—>Finish,这时工程已经建立了,如下图所示,并且各个模块都在其中。

• 完成了工程建立后,下一步也就是需要对可重构区域进行相应的定义了。点击Netlist Design,这时会弹出一个警告提示框,警告你“有模块中缺少网标文件”。为什么会出现这个警告呢?因为我们的可重构的顶层模块本来就是一个黑盒子,里面就没有相应的netlist配置,所以这个提示是正常的。

• 点击提示框上OK,展开system中left_filter和right_filter模块,在left_filter模块下选择left_filter/USER_LOGIC_I/rp_instance,并且右键选择Set Partition,连续点击Next两次,这时会出现弹出一个对话框,输入left_BB,并选择Add this Reconfigurable module as a black box without a netlist,这里是在将可重构区域设置为空的。点击Next—>Finish。

• 接下来添加highpass、lowpass、bandstop、allpass四个模块,按照上面的继续选择left_filter/USER_LOGIC_I/rp_instance,右键选择Add Reconfigurable Module,点击Yes,点击Next;在弹出的对话框中,在可重构模块名那里输入high_l,选择Netlist already available for this Reconfigurable Module,然后点击Next,指向audio_filter\resources\filters\highpass,选择其中的audio_filter_cw.ngc文件,点击Open—>Next—>Next—>Finish,这样就在左声道中添加了hightpass滤波器,按照同样的步骤添加其它三种滤波器,其它滤波器模块网表文件都在audio_filter\resources\filters文件夹下,起名依次为low_l、band_l、all_l。

• 这一步是对right_filter模块进行可重构定义,按照上面两步进行,分别命名为right_BB、hight_r、low_r、band_r、all_r。

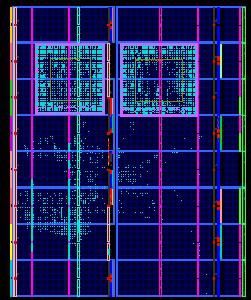

• 可重构区域的设置。上面已经添加了两个可重构区域中的modulars,,这是我们需要在硬件上划出一块区域用于left_filter和right_filter这两个模块的可重构。在Physical Constraints 标签页中,选择pblock_math_0/USER_LOGIC_I/rp_instance,右键并选择Set Pblock Size,然后分别在Device window中划出可重构区域,画完后会弹出一个选项框,即划出的区域所包含的资源。这里选择modular所需用到的资源即可。选择SLICE即可,选择其它只会浪费资源 。可重构区域如下图所示

左图为芯片布线完后的结构图

• 进行可重构电气方面的检测。选择菜单栏中Tools—>Run DRC,只选择Partial Reconfig选项,其它都不选。然后OK,这时会去检验与可重构相关的电气方面的规则是否有误。

• 新建一种策略。为什么需要新建一种策略呢?因为我们在这里的可重构区域的定义都必须是基于之前XPS中所创建的硬件,所以我们生成bitstream也必须要依照之前生成的硬件策略。选择菜单栏中Tools—>Options,选择左侧的Strategies,在Flow的下拉框中选择ISE 12,然后选择PlanAhead Strategies下面的ISE Defaults,再点击上面的加号来新建策略;命名新策略为ISE12_BM,然后点击OK。然后将Translate中-bm下拉框指定到audio_filter\edk\implementation\system.bmm。最后点击Open—>OK。

• 选择PlanAhead界面最下面Design Runs页中的config_1,在implementation Run Properties窗口中选择General页,把运行的名字改为config_blank,然后点Apply;再选择Option页,将Strategy改为ISE12_BM,确认-bm中指定为本工程system.bmm,点击Apply;在Partition页中,选择left_BB和right_BB模块选为运行模块,点击Apply。

• 在Design Run 窗口中选择mult,右键并选择Launch Runs,选择Launch Runs on Local Host,点击OK。这时会运行此配置(这个时间会有些长的)。由于上面过程中我们只完成了一种配置,这时我们还需要完成四种配置,这样才能生成所有modular的部分可重构配置文件。选择Tools—>Create Multiple Runs,然后按照上面的步骤就可以生成另一种配置了。

• 生成full bitstream和partial bitstream。生成后芯片上布线如上图所示。

第四步:开发板上FPGA的配置模式

XUPV5-LX110T开发板上的FPGA的配置模式有以下几种方式:

• 通过JTAG下载在线进行配置

• SystemACE控制器通过JTAG接口进行配置

• 通过板上的Flash PROMs进行配置

• 通过Linear Flash memory进行配置

• 通过SPI Flash memory进行配置

下面将对这几种配置方式进行介绍:

(1)JTAG配置模式(通过下载线和System ACE控制器)

在FPGA中,有两个Flash PROMs和一个CPLD能够通过JTAG接口进行配置,板上的JTAG链路图如下:

对FPGA的JTAG链路图进行描述:此链路从PC4连接端口开始,然后依次通过Platform Flash PROMs、CPLD、System ACE控制器,最后链路连接到一个可扩展的卡接口,并通过J21接口控制JTAG链路是否可接扩展卡。

JTAG链路能够用来配置FPGA芯片,并且能够用于FPGA的硬件与软件的调试。

其中JTAG链路上接着的PC4接口允许主机电脑利用iMPACT等软件工具下载bitstreams(配置文件流)到FPGA上;System ACE控制器能够通过JTAG接口配置FPGA,配置文件放在CompactFlash卡中,在使用这种方式配置FPGA时,System ACE的配置模式开关SW3必须设置为“00010101”,同时CF卡里存有配置文件,且CF卡是插入在扩展卡中的。

(2)Platform Flash PROM配置模式

Platform Flash PROMs能够被用来配置FPGA芯片,利用这种方式配置FPGA有四种模式,分别是Master Serial、Slave Serial、Master SelectMAP(并行)或Slave SelectMAP(并行)模式;可以通过iMPACT工具下载配置文件,其中配置模式开关必须选择为对应的状态。四种Platform Flash PROM配置模式对应配置开关选择状态如下表所示

表:配置模式开关选择

| Mode[2:0] |

模式 |

| 000 |

Master Serial |

| 100 |

Master SelectMAP |

| 111 |

Slave Serial |

| 110 |

Slave SelectMAP |

当设置正确,上电后或者在通电情况下按下Prog按钮,FPGA芯片都会进行配置。

(3)Linear Flash Memory配置模式

配置数据存储在线性flash中可以用来配置FPGA芯片,这种模式称为BPI模式。其中板上配置模式开关必须选择为:对于BPI_up为“010”,对于BPI_down为“011”。

当设置正确,上电后或者在通电情况下按下Prog按钮,FPGA芯片都会进行配置。

(4)SPI Flash Memory配置模式

配置数据存储在SPI Flash Memory中能够被用来配置FPGA芯片,这种模式下配置模式开关必须设为“001”。

当设置正确,上电后或者在通电情况下按下Prog按钮,FPGA芯片都会进行配置。

这一步中,由于我需要存储第三步中生成的full bitstream和partial bitstream,其中partial bitstream有四个;另外,由于本组后续科研中需要对文件进行读写操作,所以也需要能存储文件。因此,最终选择了第一种配置模式(System ACE控制器通过JTAG进行配置)。配置模式开关SW3设置为“00010101”。

由于采用System ACE控制器通过JTAG进行配置这种方式,需要full bitstream配置文件为所对应的格式才能正常运行。下一步进行格式转换。

第五步:配置文件格式转换

采用System ACE控制器通过JTAG进行配置这种方式的文件格式转换的具体步骤如下:

• 将生成的部分配置文件拷贝到\image文件夹下,分别命名为adder.bit,mult.bit,blank.bit。

• 运行Xilinx Bash Shell软件,开始> 所有程序> Xilinx ISE Design Suite > EDK > Tools> Xilinx > Bash Shell。

• 在Bash shell中进入到\image文件夹下,在bash shell中输入以下命令用来生成download.bit。命令如下:

data2mem -bm ../edk/implementation/system_bd

-bt ../PlanAhead/PlanAhead.runs/adder/config_blank.bit

-bd ../edk/SDK/SDK_Workspace_35/TestApp/Debug/TestApp.elf tag

microblaze_0 -o b download.bit

这些命令是将硬件部分system_bd、adder.bit(全配置文件)和程序部分TestApp.elf进行打包生成download.bit。

• 生成的download.bit文件将在\image文件夹下。然后再使用下面的命令将download.bit转换成system.ace文件。

xmd -tcl genace.tcl -jprog -target mdm -hw download.bit -board xupv5

-ace system.ace

• 最后就生成了system.ace镜像文件,将生成的部分可重构文件分别修改文件名为:high_l.bit、high_r.bit、low_l.bit、low_r.bit、band_l.bit、band_r.bit、blank_l.bit、blank_r.bit、all_l.bit、all_r.bit,然后将它们拷贝到CF卡中即可。

第六步:开发板的运行

调好串口上位机后,上电后,即可正常运行。

小结:

这一博文中比较详细地介绍了基于Virtex5动态可重构的过程,并指出了在这个过程中需要注意的问题。

虽然本章很详细的对每一步给出了说明,但是不经过自己的亲自实验是无法对其真正掌握的。“实践出真知”,希望大家能将上面的实验能够多做几遍,真正掌握。其中的某些步骤大家在做的时候很有可能碰到一些我没有碰到的问题,特别是在SDK的main文件那里,还有后来生成bitstream的时候,planAhead可能会有一些错误提示文件缺失(貌似当时我缺失的文件在系统的C盘里,复制到工程里面就行了)。还有的问题可能就需要大家自己google或者去Xilinx论坛里面去找了~