cadence library builder 16.6基本教程和菜单翻译

Library Builder

在下也是刚刚入门cadence的小白一个,因为感觉使用library builder建立元器件封装和原理图相当方便,故写一点自己的心得。如有不正确的地方,欢迎批评指正。

本文以STM32F103VET6的原理图和封装建立为例。

使用的cadence 为16.6,library builder为吴老师整合的16.62版本。另外说明一下,library builder 17.2不能兼容cadence16.6 ,会导致无法导出原理图。

原理图生成

Library builder(库生成器)非常适合生成管脚数量很多的芯片,大大节约了自己建立封装库和原理图库的时间。

芯片手册PDF的下载和导入

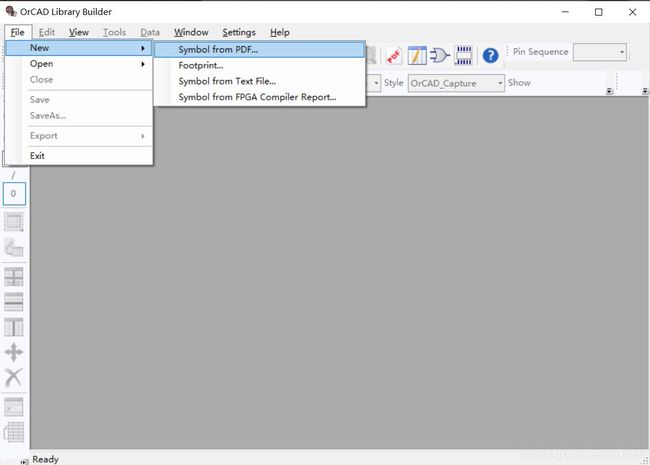

打开cadence library builder,可以看到其基本界面。我们点击[File(文件)]按钮来新建一个设计项目。

先来建立原理图文件。

[File]->[Symbol from PDF],我们先来建立一个原理图文件。

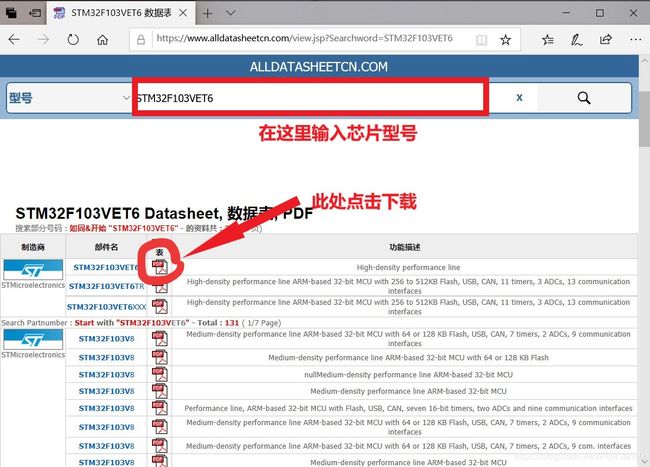

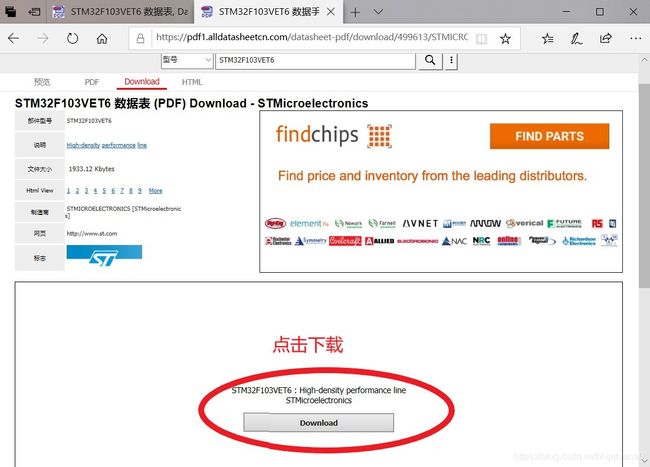

但是首先我们需要获取一个标准的芯片手册pdf文件,最好是来源于芯片的最初供应商。打开www.alldatasheetcn.com下载芯片手册。

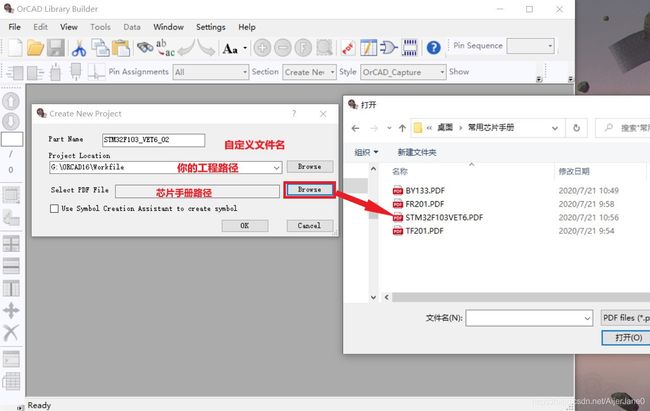

接下来回到library builder,在选择了Symbol from PDF后,我们需要为我们的库文件起一个【名称】。

【工程路径】则是在你使用cadence或者orcad时创建的工程路径,这样便于在使用工程是直接调用你自定义的库文件。当然,你也可以先建立库,在用到它们时再将其复制到工程路径内。

【PDF文件路径】选择你刚刚下载的stm32f103vet6打开即可。

在一切设置好之后,点击确定(OK)按钮。

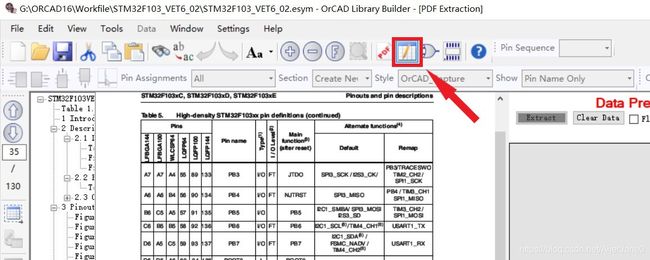

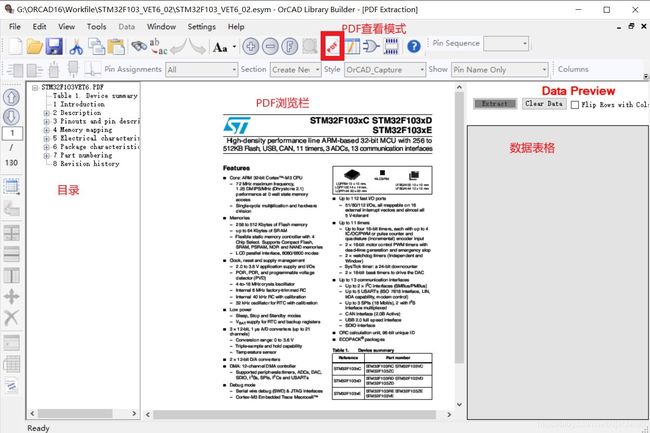

下图便是library builder的PDF查看模式界面,左边是你的PDF【目录】(有些芯片手册的PDF导入后无法识别出目录);中间是【PDF浏览界面】,而右侧则是你的【数据表格栏】,用于将管脚信息导入后做确认前的浏览。

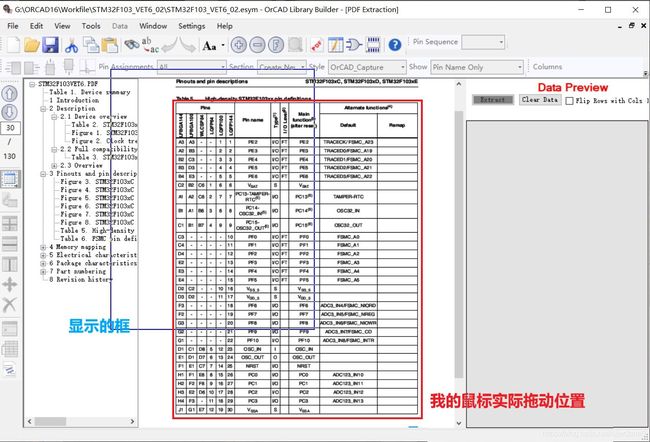

接下来,需要导入管脚信息,转到PDF的管脚页面(我的pdf在30页处),点击左侧的【选择区域(Select Area)】->【表格(Table)】按钮把你需要的管脚信息表格框选进去。

然后按住鼠标左键框选你需要的管脚表格,会出现一个蓝色的框。

PS:有时可能会因为电脑分辨率设置出现的框比你拖出来的框小,并发生错位;如图,我在框选表格时鼠标拖动的范围如红色框所示,蓝色框并没有包含整个表格;但是无需担心,软件实际包含的表格范围是以你的鼠标拖动的范围为准。

框选的表格会显示在右侧,这时你需要检查一下整个表格是否已经被完全框选,并没发生行、列错位的情况,那么你可以选择【Extract】将表格录入后台的表格模式中。如果不满意需要重新框选,点击【clear data】即可。

把几页的表格框选完毕,直到管脚映射表的最后一页。

接下来点击【View

ScratchPad】进入表格模式。

编辑管脚数据表格

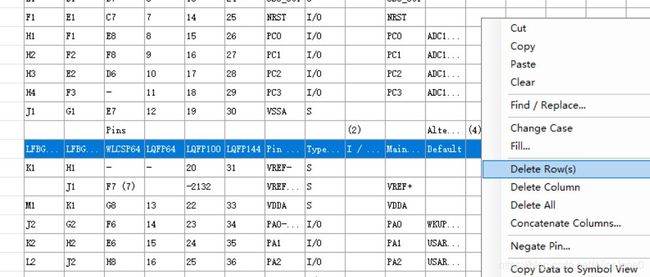

为了生成管脚我们需要把芯片手册中的表头去掉,同时,没有用的列也要删除。比如我们现在是画LQFP100的封装结构,不需要的几种封装的管脚信息,都可将其删除。

选中一格或多格,【鼠标右键】->【Delete Row】删除一行。

同样的方法删除不需要的列。【Delete Column】

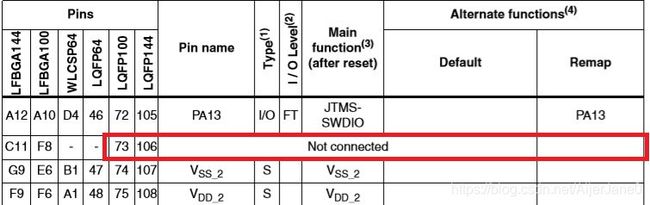

像stm32f103vet6的LQFP100封装的73脚为空脚,但是在表格里我们需要为之命名。

此处我命名为PNULL 管脚类型为NULL。

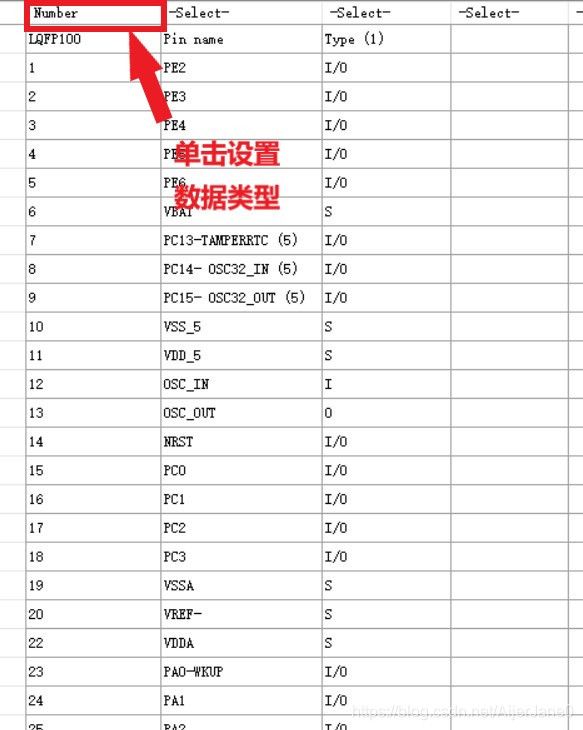

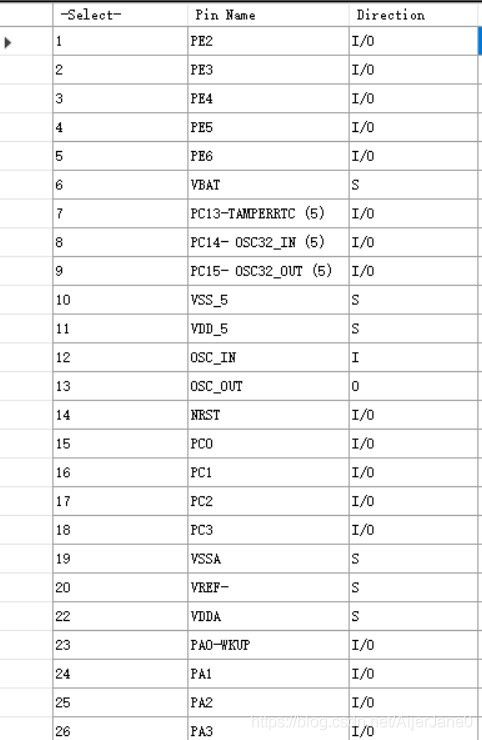

最后我们只留下【管脚号】【管脚名】和【管教类型】三列。同时设置数据类型。

完成后如下图所示。

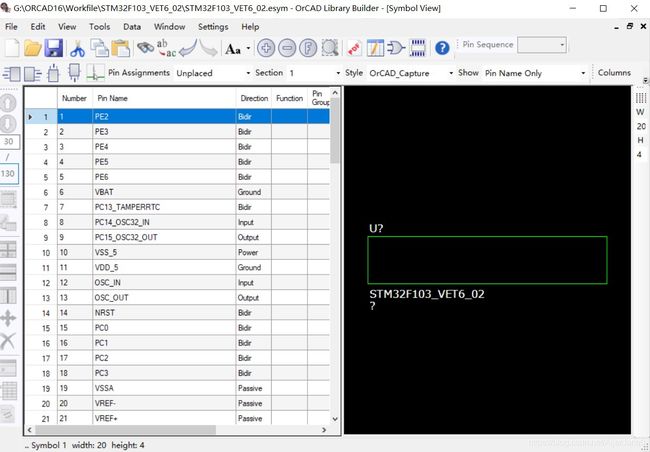

最后设置一下引脚类型,选中管脚类型,【右键】->【Fill】填入相应的管教类型。I\O口为[bidir](双向)。S对应两种:VSS和VDD;VDD相关的都为[Power],VSS为公共端[ground]。I和O对应[Input] [Output]。其余填[passive]。

再修改一下7 8 9脚的名字,管脚的名字不能出现”空格”和”-”,需要换成下划线”_”,否则待会生成原理图时会报错。

最后结果如下图:

从表格到原理图

接下来我们需要从表格生成原理图,选择任意一个方格【右键】->【Copy Date to Symbol View】->【Copy and Switch

to Symbol View】。

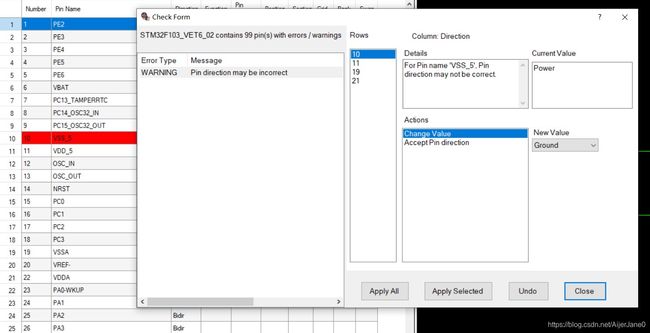

有4个警告,原因是”管脚名字可能不正确”,这个可以忽略,我们直接点【Close】。

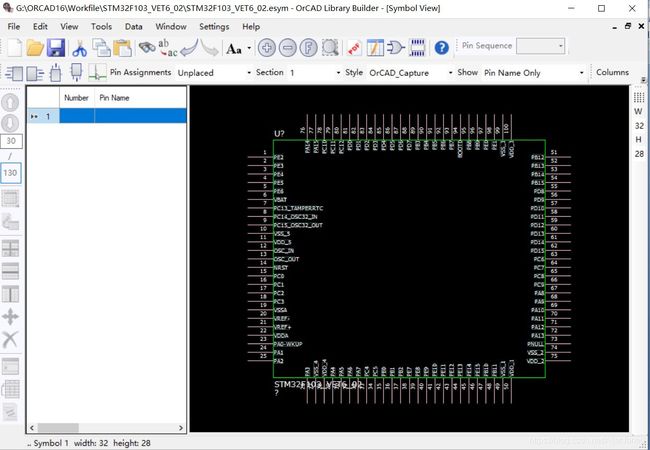

拖选1-25号引脚,点击【Assign Left】将选中的所有引脚放在左侧。

用同样的方法,将之放在下方、右方和上方。

PCB封装生成

我们需要为这一个原理图匹配一个对应的封装,接下来我们来新建一个封装文件。

生成封装模板

我们选择QFP封装格式。

修改封装模板

现在我们进入到了封装的编辑界面。我们需要调整一些设置以便达到stm32f103vett6的LQFP100的封装要求。

芯片元件参数设置

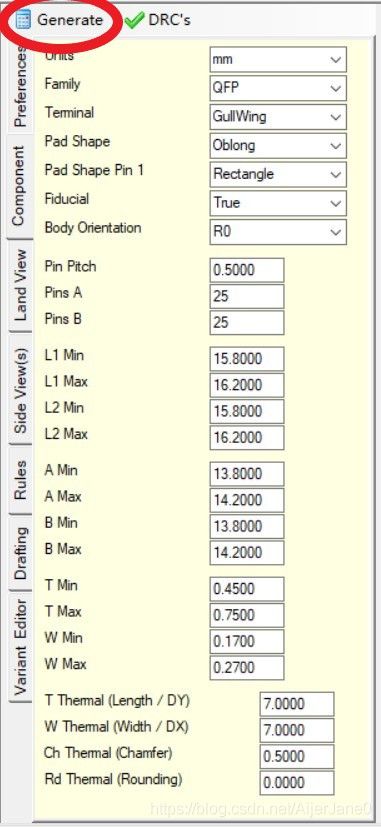

我们先来看一下各部分参数的翻译,在【原件(Componet)】选择卡,我们可以看到几个参数的选项。

【单位(Unit)】可以选择mm毫米(公制) 以及mils毫英寸(英制)。*我们选择公制mm。

【芯片族(Family)】这个源于官方芯片大类的默认不同的封装格式。*我选择QFP。

【焊盘形状(Pad Shape)】可以选择矩形和椭圆。*默认为椭圆(Oblong)。

【第一引脚焊盘形状(Pad Shape 1)】用于分辨PCB上第一引脚的位置。*我这里选择矩形(Rectangle)。

【基准点设置(Fiducial)】是否放置默认库的基准点,这里基准点是PCB固定螺钉的焊盘。*如果你的方案是直接贴片封装,请填FALSE。

【芯片旋转角度(Body Orientation)】可以选择0°

,180°, 270°

,360°。*我这里选择默认0°不变。

=======================================================

接下来进一步设置器件参数;

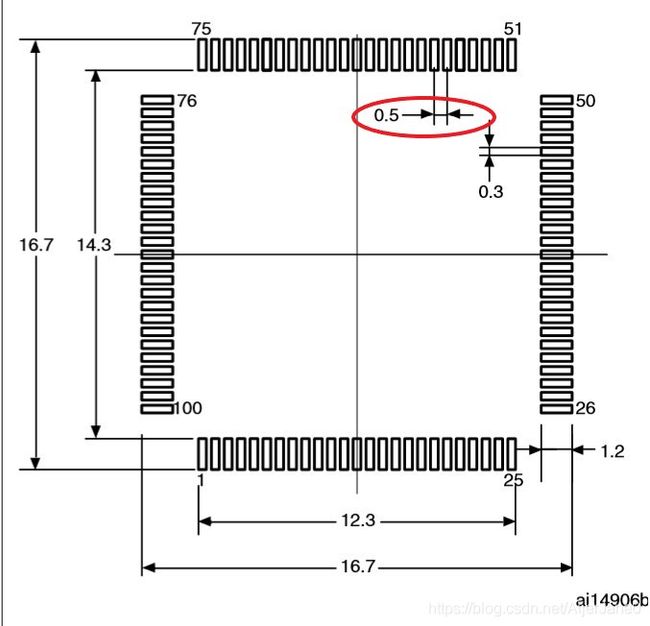

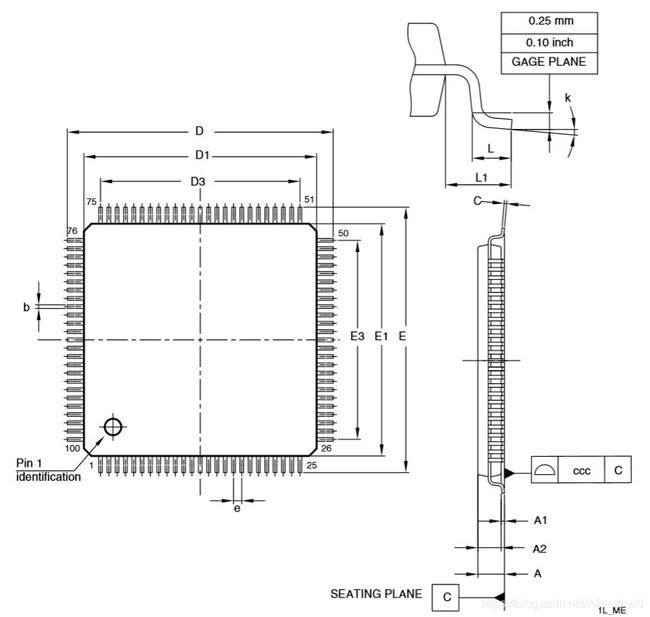

【单个引脚间距(Pin pitch)】各个引脚中心的间距。*通过查阅芯片手册,我们知道其间距为0.5mm。

【Pins A】【Pins B】由于vet6芯片水平竖直都是25个引脚,我们都设置为25。

同样根据芯片手册的参数,我们调整其芯片体的尺寸。

最后全部调整完毕如下图所示:我们点击【Generate】来更新我们的设置。(通常改变参数但未应用时,【Generate】按键会变成红色,代表你修改了参数还未保存应用)

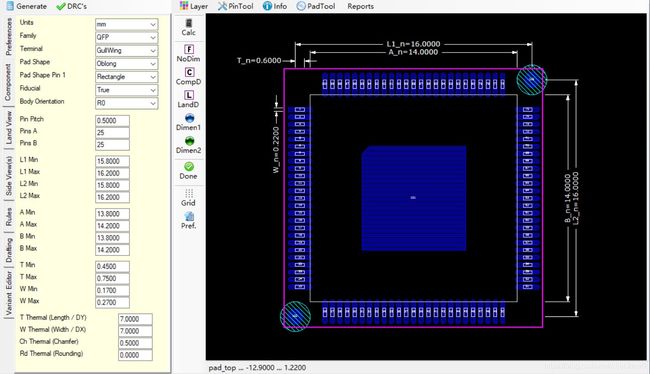

最后得到芯片元件尺寸如下图所示:

焊盘设置

芯片底部修剪(Trim Under Body)】为Ture时系统会自动删除被芯片体遮盖部分的焊盘,以减少不必要导电部分所产生的的电磁噪声。*这里我选择Ture。

【焊盘几何捕捉(Land Geometry snap)】【制造公差(Fabrication tol)】【放置公差(Placement Tol)】

在没有设计要求的情况下不变即可。

【助焊层过余(Paste Mask Excess)】【阻焊层过余(Solder Mask Excess)】除非有特殊要求,不需要额外设置。(下图给出了助焊层和阻焊层的示意图,图片来源为:百度图片)

【圆角设置】【倒角设置】用于焊盘为矩形时有效。*此处仅1脚为矩形,我们不设置。

【Courtyard Excess Nom】用于控制器件整个封装的外边框余量。*我选择0.5

【焊盘常规趾长(Toe Nom)】【焊盘常规跟长(Heel Nom)】【焊盘常规侧宽(Side Nom)】对应尺寸如下图,按自己需求更改即可。

设置结果如下:

外观

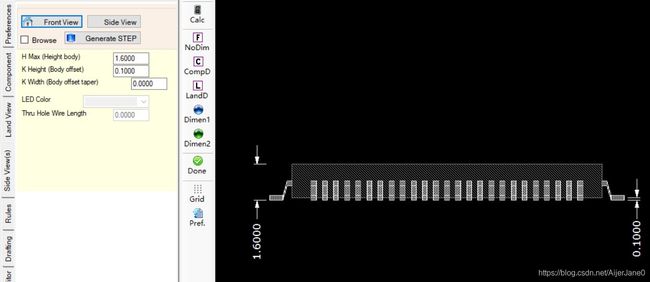

我们在【Side View】选择卡,按芯片手册中参数设置一下芯片高度。

规则检查

【规则】选择卡,无特殊要求时不需变化,这个按你的产品要求定。

无大问题后,可以进行DRC(规则检查),点击DRC按钮进行检查。

检查无误后,可以导出元器件封装了。