哈工大刘宏伟《计算机组成原理》课程框架总结

哈工大刘宏伟老师的《计算机组成原理》采用自顶向下方法,系统介绍了计算机各个基本部件的体系结构、逻辑实现、控制方式。(一定数电基础是必要的,如果了解汇编更有助于理解部分内容)

B站链接计算机组成原理——哈工大刘宏伟(B站)

慕课链接(上)计算机组成原理——哈工大刘宏伟(慕课上)

慕课链接(下)计算机组成原理——哈工大刘宏伟(慕课下)

本文是笔者听完全部课程后结合自己的理解,试图用尽可能通俗的语言,描述课程的框架,摘附主要的构图进行填充,非详细的课程笔记。

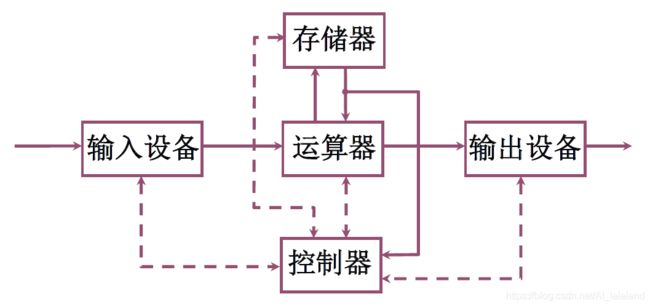

(引入)首先看一下冯-诺依曼计算机的硬件组成(5大部分):

-

控制器(CU)

-

运算器(ALU)

-

存储器

-

输入设备

-

输出设备

(图中实线代表数据,虚线代表控制信号)

接下来进行两步处理:

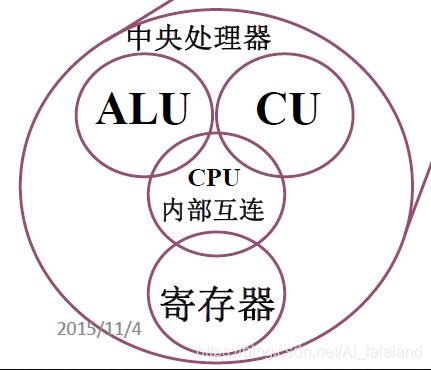

1、控制器CU + 运算器ALU = 中央处理器CPU

2、CPU、存储器、I/O设备之间的通信载体抽象为系统总线

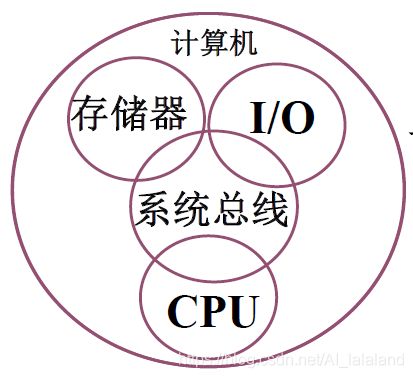

一、我们提炼出对计算机组成的抽象:

说明:内容重点介绍存储器和I/O设备,其中一些DRAM和SRAM实现原理相关的内容需要有一定的数字电路基础才能理解,本文未对其中细节展开描述。

其中各部件的布局:

(1)关于存储器

存储器的基本结构由三部分组成:

- 存储体

- 地址寄存器MAR(反映存储单元个数)

- 数据寄存器MDR(反映存储字长)

根据作用不同,存储器分为三类:

- 主存

- 缓存

- 辅存

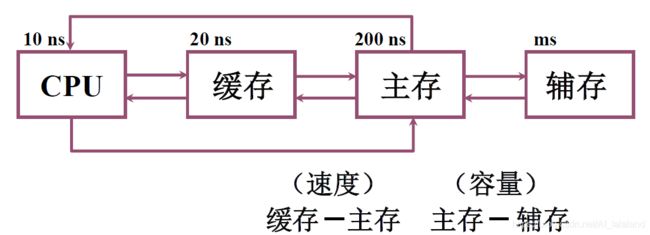

原始的计算机只有CPU和主存结构,随着计算机的发展,逐渐设计实线了如图的多级层次化结构。

关于缓存:现代计算机运行速度的瓶颈是访存速度,在CPU和主存之间加入访存速度更快的缓存,可以提高CPU使用效率,整体提高计算机运算速度,当然,缓存的经济成本高于主存,存储实现方式不同(后续介绍)。

关于辅存:提高数据存储量,迎合时代需要,缺点是CPU不能直接访问缓存,需要嵌入主存加载访存的过程,处理速度慢。

不同原理的存储器根据特性的不同部署在存储体系的不同层次中,但也不是严格一一对应的,根据不同规格的计算机有一定差别,一般情况下:

- CPU内部寄存器:静态RAM

- 缓存(可以有多级缓存,高级缓存可设计在CPU内部):静态RAM

- 主存:动态RAM(用于存储数据)、ROM(用于存储系统程序)

(2)关于I/O设备

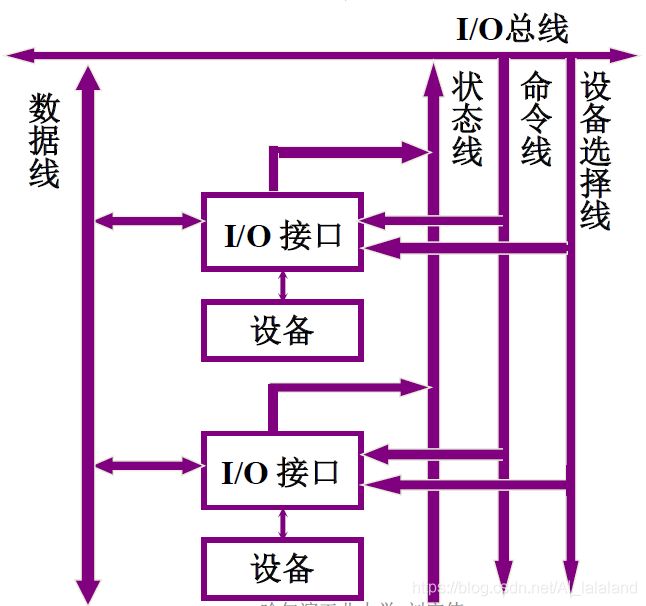

首先看一下I/O设备连接到I/O总线的方式:

主要包括4条线路:

- 设备选择线

- 命令线

- 状态线

- 数据线

I/O设备的控制方式分为3种:

- 程序查询方式(串行)

- 程序中断方式(并行)

- DMA方式(并行)

我们主要了解程序中断方式和DMA方式。

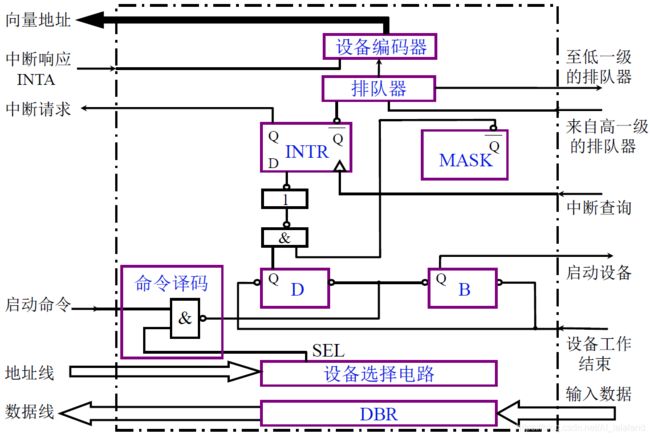

(1.1)程序中断方式

程序中断方式的I/O接口电路:

以CPU读命令为例简述响应过程:

(1.1.1)CPU发布“对某个地址的I/O设备的读命令”

设备选择电路从地址总线读取地址,若地址就是本I/O接口的地址,发出SEL信号;

命令译码器同时接受到来自CPU的启动命令和SEL信号,发出启动命令,通过触发器B启动设备。

(1.1.2)I/O设备为执行读命令做准备

将要读的存储单元的数据写入缓存器DBR

写入完毕后,触发器B置0,触发器D置1

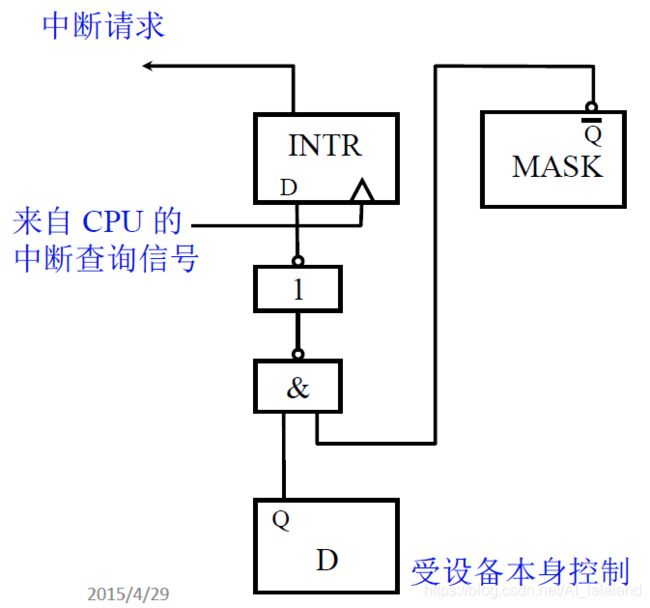

(1.1.3)I/O接口对CPU发出中断请求信号

若中断屏蔽器MASK(由CPU控制)给出信号允许中断请求,当接收到CPU发出的中断查询信号,通过总线向CPU发出中断请求信号INTR

(1.1.4)I/O设备经由排队器(这里使用链式排队器)确定中断响应的优先次序

由简单的非门和与门电路搭建,图中4个I/O设备优先级为1>2>3>4

若此时无更高优先级的I/O设备同时发出中断请求信号,则允许该设备响应中断

(1.1.5)I/O接口执行中断响应

当接收到CPU发出的中断响应INTA信号,且排队器判优允许,则进入设备编码器,形成中断向量地址(指示是哪一个I/O设备在执行中断响应)

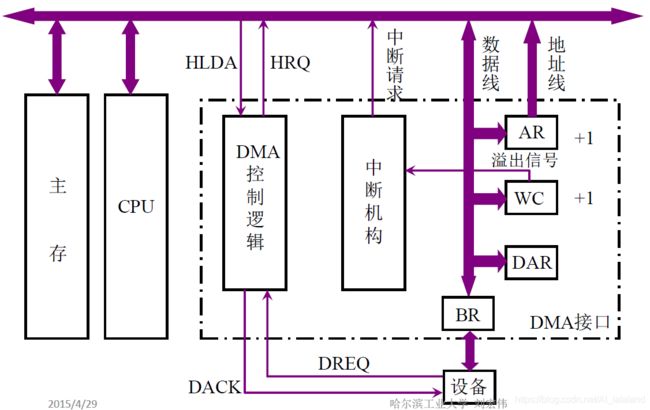

(1.2)DMA方式

DMA方式的I/O接口电路:

其中:

- AR:地址寄存器

- WC:计数器(记录传输数据量)

- BR:数据寄存器

- DAR:设备地址寄存器

以CPU读命令为例简述响应过程:

- 设备将欲传的第一个数据输入到DR

- 设备向DMA控制逻辑发送DREQ请求

- DMA控制逻辑向控制总线发送HRQ请求

- 控制总线向DMA控制逻辑发送HLDA响应

- AR向地址总线发送欲访问的内存地址

- DMA控制逻辑向设备发送DACK响应

- BR向数据总线发送欲传的第一个数据,同时AR+1,WC+1(为下一个数据的传输做准备)

- 循环步骤1-7,直至WC向中断机构发出溢出信号

- 中断机构向控制总线发送中断信号

(1.3)程序中断方式和DMA方式的比较

(3)关于总线

总线=控制总线+地址总线+控制总线,各个中心的功能顾名思义,很好理解,这部分内容已经夹杂在存储器和I/O设备的接口电路中进行介绍。

二、对CPU部分进行细化(自顶向下):

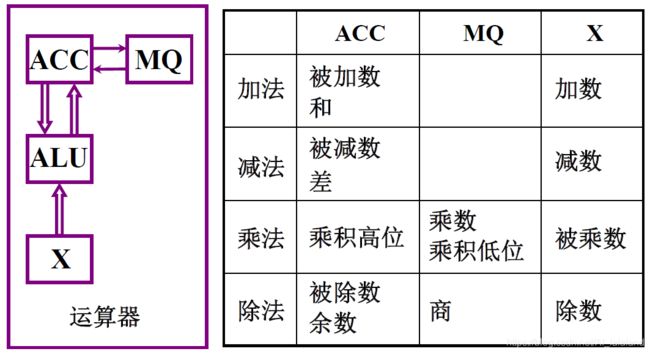

(1)关于ALU

说明:这部分主要结合二进制数的无符号数、有符号数、原码、补码、反码、移码、定点表示、浮点表示相关的知识,介绍ALU实现算术移位、加减法运算、乘除法运算的具体过程和数字逻辑硬件实现方法,篇幅较大,难度也不太高,这里不作展开。

(2)关于寄存器

(2.1)用户可见的寄存器

- 通用寄存器:存放操作数(如8086中的AX、BX)

- 数据寄存器:存放操作数

- 地址寄存器:存放地址

- 条件码寄存器:存放条件吗,可作为程序分支的依据(如溢出、进位等)

(2.2)用户不可见的寄存器

- 控制寄存器:控制CPU操作

- 状态寄存器:存放状态字

(3)关于指令

(3.1)指令格式:操作码 + 地址码

操作类型:

- 数据传送:MOVE STORE LOAD PUSH POP

- 算术逻辑运算:ADD SUB MUL DIV INC DEC CMP NEG AAA AAS AAM AAD AND OR NOT XOR TEST

- 移位操作

- 转移:JMP JZ JO JC SKP

- 输入输出:IN OUT

寻址方式:

- 立即寻址:OP # A

- 直接寻址:EA = A

- 相对寻址:EA = (PC) + A

- 间接寻址:EA = (A)

- 寄存器寻址:EA = Ri

- 寄存器间接寻址:EA = (Ri)

- 基址寻址:EA = (BR) + A

- 变址寻址:EA = (IX) + A

- 堆栈寻址

- 隐含寻址:ADD 寻址特征 A

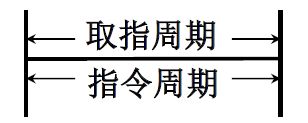

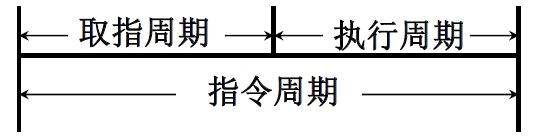

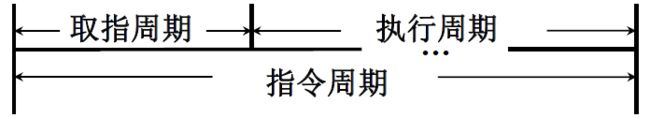

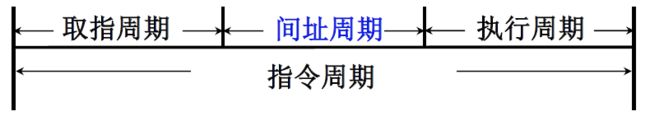

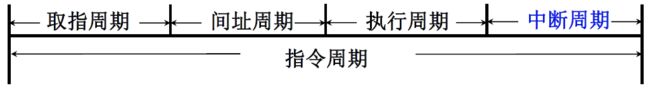

(3.2)指令周期

四种情况:

1、不需要访存(如:NOP)

2、需要访存(如:ADD)

执行周期长度根据执行内容决定(如:MUL)

3、需要间址寻址

4、带有中断指令

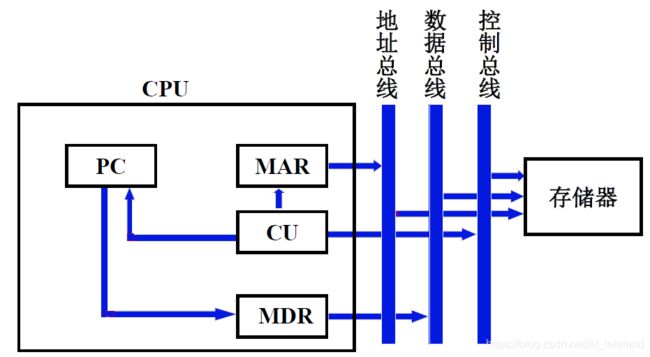

(3.2.1)取指周期

具体过程:

- PC -> MAR -> 地址总线 -> 存储器(内存地址)

- CE -> 控制总线 -> 存储器(读命令)

- 存储器 -> 数据总线 -> MDR -> IR(指令内容)

- CU + 1 -> PC(准备读下一条指令)

(3.2.2)间址周期

具体过程:

- MDR -> MAR -> 地址总线 -> 存储器(内存地址)

- CU -> 控制总线 -> 存储器(读命令)

- 存储器 -> 数据总线 -> MDR(下一条指令的实际地址)

(3.2.3)执行周期

情况根据具体的执行内容决定。

(3.2.4)中断周期

具体过程:

- CU -> MAR -> 地址总线 -> 存储器(欲保存断点的内存地址)

- CU -> 控制总线 -> 存储器(写命令)

- PC -> MDR -> 数据总线 -> 存储器(中断之后要恢复的指令内容)

- CU -> PC(中断程序的入口地址)

三、对CU部分的细化(自顶向下):

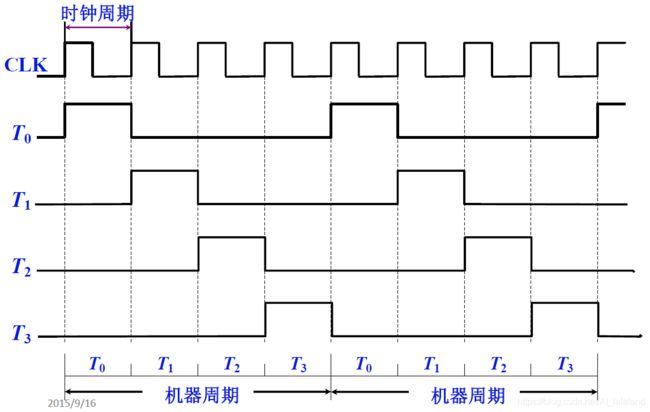

说明:这部分讲述加入了时钟,重点理解操作执行的时序问题。

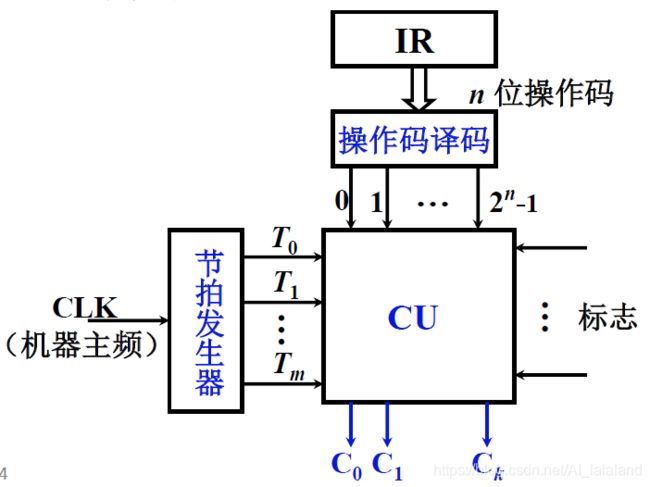

(1)CU的功能

输入信号:

- 时钟:一个时钟脉冲发一个操作命令或一组可并行的操作命令

- 指令寄存器:控制信号(与指令的标志码有关 OP(IR) -> CU)

- 标志:CU受标志控制

- 来自系统总线的信号:如中断请求INTR、总线请求HRQ

输出信号:

- CPU内部的各种控制信号:如Ri -> Rj、(PC) + 1 -> PC、ALU的算术运算

- 传送至控制总线的信号:如读写命令、中断响应信号INTA、总线响应信号HLDA

注:若干个时钟周期组成一个机器周期(图示4个时钟周期组成一个机器周期),每个时钟周期(也称节拍)执行一条或一组可并行的指令。

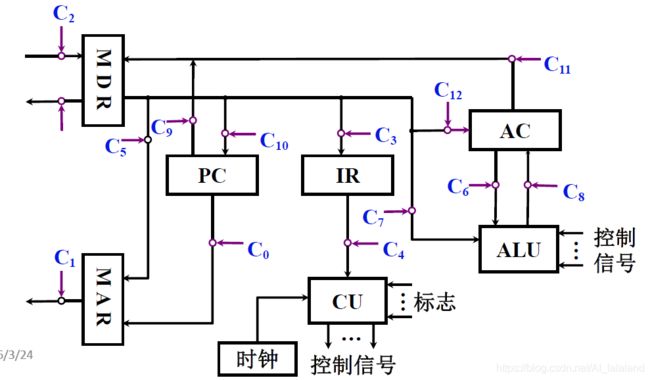

(2)CU设计方法一:组合逻辑设计

完全使用硬件即可完成设计,运行速度快,不过结构较为庞杂,不易于调试和修改,适用于RISK(精简指令集)。

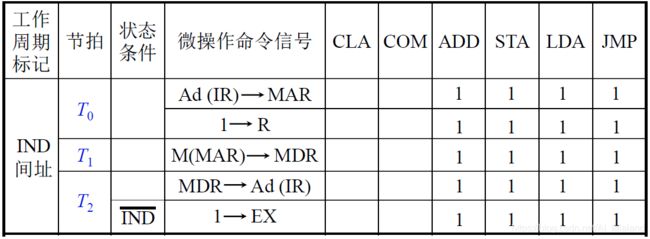

对前文提到的一些简单指令,根据各个指令的特性,设计每一个指令在一个机器周期内的各个节拍(T0-T2)上的操作(这部分内容较多,而有了之前章的基础也很容易理解,不在这里具体展开)。

将各个指令在每个节拍下的操作内容,列出具体的时序关系表:

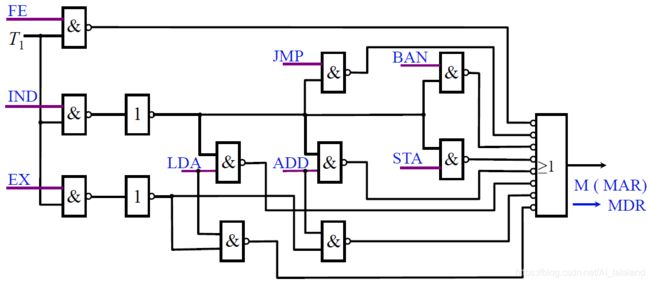

写出逻辑关系表达式(以M(MAR) -> MDR操作为例):

根据逻辑表达式可以绘制出逻辑图:

(3)CU设计方法二:微程序设计

核心思想和上述方法类似,实现方法利用软件,用存储逻辑替代数字电路逻辑,增加了译码等操作。这里仅附原理图,不做展开。

基本控制单元框图:

机器指令对应的微程序:

最终形成的微程序码点: