计算机原理之存储器组织

目录

一、八位锁存器

二、8-1选择器

三、3-8译码器

四、随机访问存储器

五、RAM阵列

六、大规模RAM阵列

七、64K x 8 的RAM阵列

一、八位锁存器

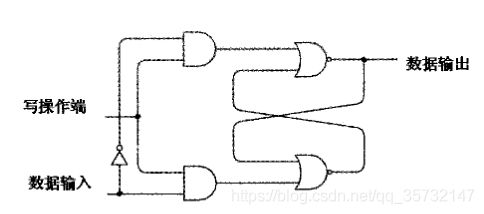

可以将电平触发的D型锁存器表示成如下形式:

从结构上来讲,这套电路与先前的电平触发的D型锁存器是同一种触发器,只是命名的方式不尽相同:

- Q输出端被称为数据输出端(Data Out)

- 时钟输入端命名为写操作端(Write)

一般情况下:

- 如果写操作端为0,则数据输入信号的状态对输出无影响

- 如果想把数据输入信号存储在触发器中时,可以把写入信号应先置1后置为0

前面已经讲过,这种类型的电路也被称为锁存器,因为存储进去的数据就好像被锁住了一样。

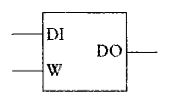

上面的电路结构可以简写为:

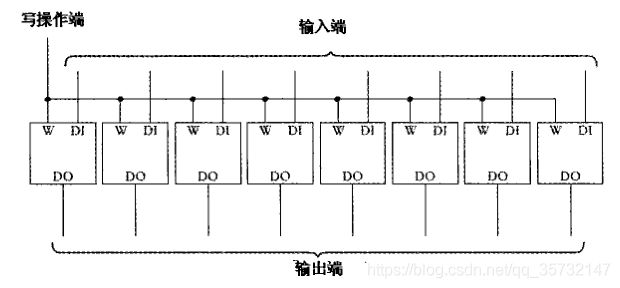

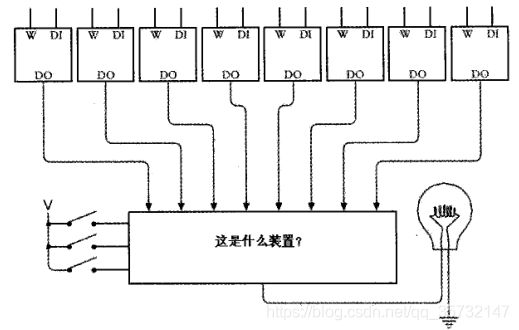

可以把多个1位锁存器组织成为多位锁存器,所要做的就是把写操作端的信号连接到系统中:

如果要把一个8位二进制数存储在锁存器中,首先要把写操作端置1,然后置0。

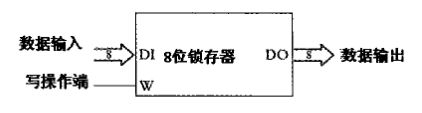

上面的8位锁存器可以简写为:

二、8-1选择器

还有另一种方法集成8个1位锁存器,但其结构并不像上面的这样直观。

这种方法能够用一个灯泡来确定锁存器的数据输出信号:

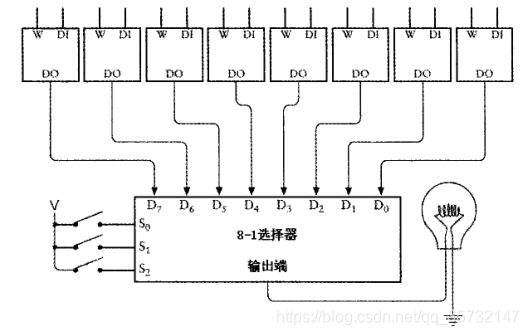

如下所示,只需要一个8-1数据选择器(8-Line-to-1-Line Data Selector)。

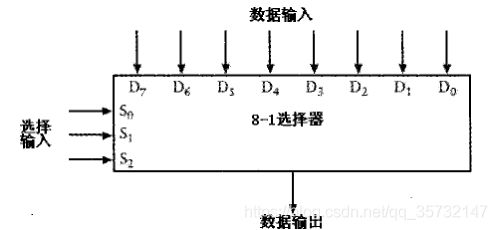

8-1选择器有8个数据输入端(在其顶部),以及3个选择输入端(在其左侧)。

选择输入端的功能就是选择一个输入端数据,然后使其在输出端输出。

如果选择输入端为000,则将D0锁存器的值输出,若选择端为111,则D7锁存器的值将被输出。

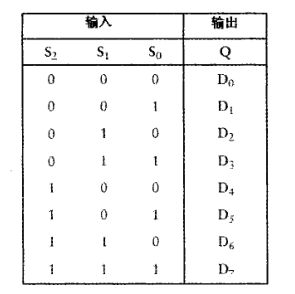

系统的真值表如下:

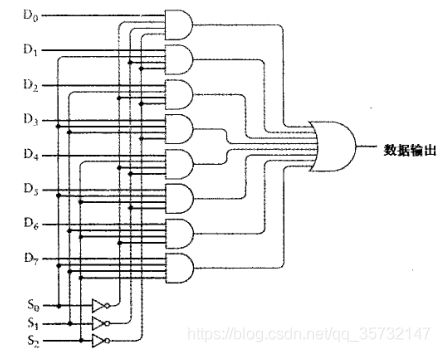

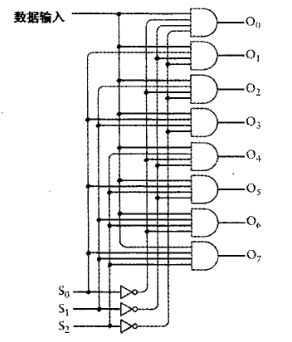

8-1选择器主要组成部件为:

- 三个反向器

- 八个4端口输入与门

- 一个8端口输入或门

8-1选择器的组织结构如下图所示:

所以可以使用一个8-1选择器对8个锁存器进行选择操作,并将相应锁存器的数据输出:

三、3-8译码器

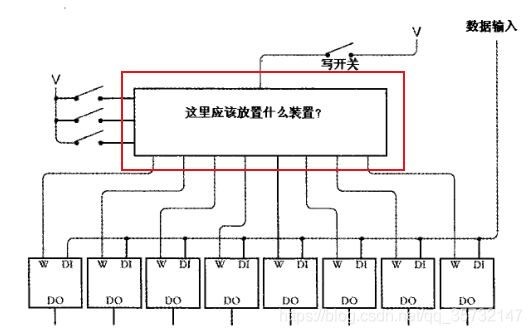

除此之外,还需要一个独立的写入信号,它能被写到任意(且唯一)的锁存器上。

需要另外一款电路元件,这款元件与8-1选择器功能类似,但它的作用正好相反:

这款电路元件叫3-8译码器(3-to-8 Decoder):

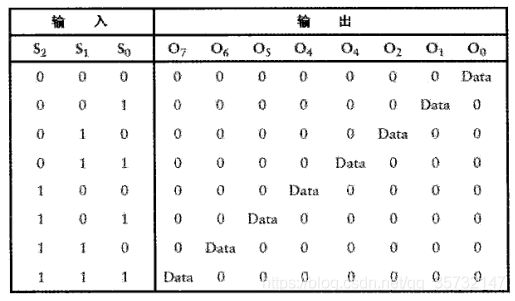

3-8译码器的输出端口共有8个。

在任何时候,译码器只会有一个锁存器的输出为1,其余均为0。

每一个输出端的结果都是由S0、S1、S2这三个信号的排列组合决定的。

3-8译码器的逻辑表如下:

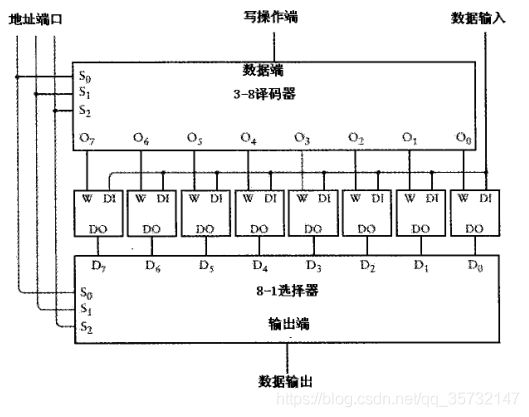

四、随机访问存储器

将8个锁存器加入到电路就形成了完整的系统:

译码器和选择器具有相同的选择信号,在上图中这三个信号一起被称为地址端口(Address)。

地址的作用就像我们平时使用的邮箱号,长度为三位的地址决定了8个锁存器中的哪一个将被引用。

在3-8译码器的输入端,地址起到了决定哪些锁存器可以被写操作端的信号触发来保存数据的引用。

在输出端,8-1选择器通过地址来选择8个锁存器中的一个作为输出。

这种配置下的锁存器普遍的叫法是随机访问存储器(Random Access Memory),或RAM。

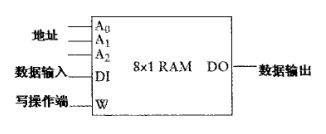

以上的随机访问存储器可存储8个独立比特的RAM,它的简化结构如下:

相比于其他的顺序型的存储器,这种存储器在使用时有一定的限制,如果想要读取地址为101的数据,必须先把地址为100的数据读取出来。

五、RAM阵列

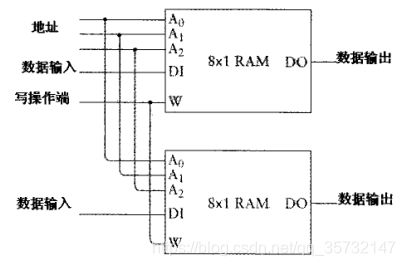

将RAM进行特殊的配置可形成RAM阵列(Array)。

RAM阵列的组合形式多种多样,比如可以通过共享地址的方式可以把两个8 x 1 的RAM阵列连接起来,如下所示:

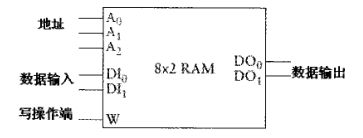

可以把这两个8 x 1的RAM阵列的地址和输出都分别看成一个整体,这样就得到了一个8 x 2的RAM阵列:

这个RAM阵列可存储的二进制数依然是8个,但每个数的位宽为2位。

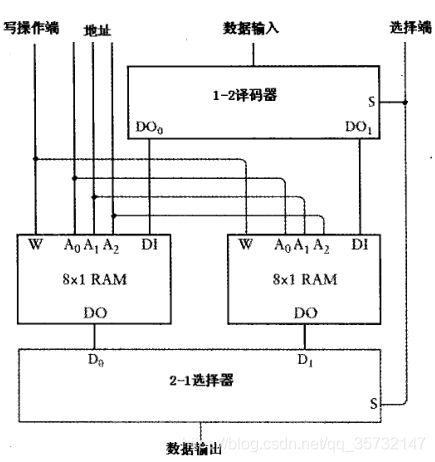

还可以把两个8 x 1的RAM阵列看作是两个锁存器,使用一个2-1选择器和一个1-2译码器就可以把它们按照单个锁存器连接方式进行集成:

“选择”端之所以连接到1-2译码器和2-1选择器,主要作用是在两个8 x 1RAM阵列中选择一个,本质上它扮演了第4根地址线的角色。

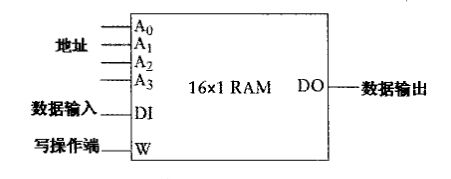

因此这种结构实际上是一种16 x 1的RAM阵列,如下图所示:

RAM阵列的存储容量与其地址输入端的数量有直接的联系:

- 在没有地址输入端的情况下(只有1位锁存器和8位锁存器的情况) —— 只能存储1个单位的数据

- 当存在1个地址输入端时(2-1选择器和1-2译码器) —— 可以存储2个单位的数据

- 有两个地址输入端时(4-1选择器和2-4译码器) —— 可以存储4个单位的数据

- 有3个地址输入端时(8-1选择器和3-8译码器) —— 可以存储8个单位的数据

- 有4个地址输入端时(16-1选择器和4-16译码器) —— 可以存储16个单位的数据

可以把它们之间的关系归纳成如下等式:

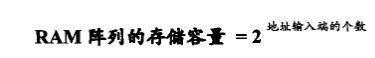

六、大规模RAM阵列

搭建了小型RAM阵列,自然就能搭建一个大规模的RAM阵列,就像下面这样:

上图所示的RAM阵列可存储8192个比特的信息,每8个比特为一组,共分为1024个组。

因为2的10次方恰好是1024,所以地址端共有10个输入端口。

电路还包括8位的数据输入端和8位的数据输出端。

从专业的角度来讲,这个RAM阵列的存储容量为1024个字节(1字节等于8比特)。

就好比一个邮局放置了1024个邮箱,而每个邮箱里面都可以存放1字节大小的邮件。

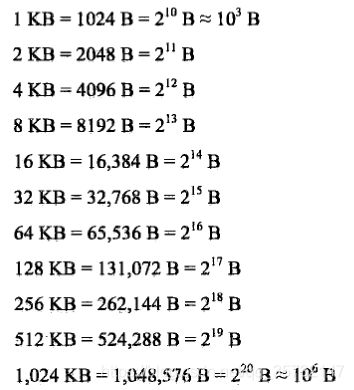

1024字节通常称为1千字节,千字节可以简写为KB。

所以这种RAM阵列存储容量也可以表示为1KB,如果再加上一条地址线,它的存储容量将变成原来的两倍。

下面的公式表示了存储容量的翻倍的过程:

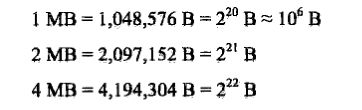

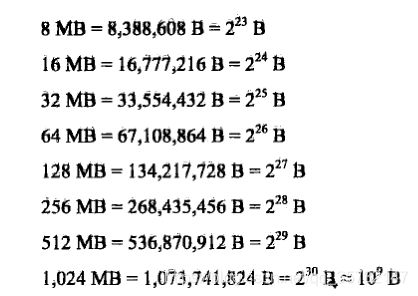

相同的逻辑,可以把1024KB统称为1兆字节(megabyte,希腊文中的mega意味着宏大)。

兆字节通常缩写为MB。

下面的例子表示了兆字节为单位的存储容量翻倍的过程。

1024MB也被顺气自然地称为1吉字节(gigabyte,希腊文中的giga意味着巨大),缩写为GB。

同理,1024GB被称为1太字节(terabyte,teras希腊语意思为巨人),缩写为TB。

1KB近似为1000个字节,1MB近似为100万个字节,1GB近似为10亿个字节,1TB近似为1万亿个字节。

在1999年时,家用电脑的随机存储器的容量一般为32MB、64MB或128MB。

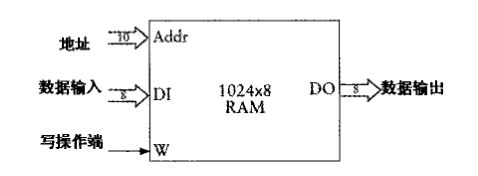

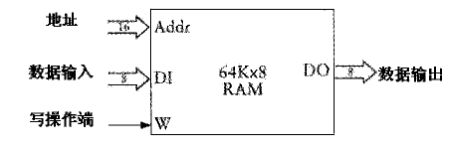

七、64K x 8 的RAM阵列

能够构造任意大小的RAM阵列后,就可以构造一个容量为64KB(65535字节 = 64 x 1024 x 8 比特)的存储器组织,如下所示:

为什么选择大小为64KB的RAM阵列?而非32KB或128KB?

因为65536是一个约整数,转换为幂的形式就是![]() ,这个RAM阵列需要配备16位的寻址端。

,这个RAM阵列需要配备16位的寻址端。

换句话说,该地址恰好可以用2个字节表示。

64KB的内存是1980年的个人电脑的主流配置,但它的确不是用电报继电器组成的。

在先前的讨论中,存储每个比特需要9个继电器(因为1个电平触发的D型锁存器由9个继电器构成),推算一下64K x 8的RAM阵列就需要至少500万个继电器!(准确的数字是64 x 1024 x 8 x 9 = 4718592)

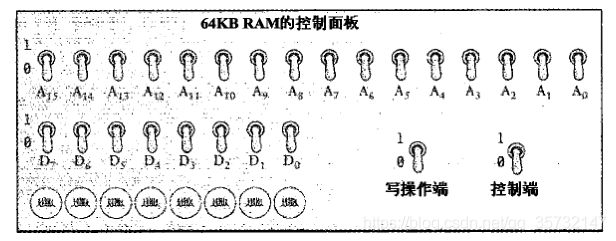

如果用一种控制面板来辅助管理对这块64KB存储器的操作—— 包括写数据和读数据,一切将会直观明了。

在这款控制面板上,有16个开关用于控制地址位,还有8个开关用来控制要输入的8比特数据。

写操作端也用一个开关来表示,8个灯泡用来显示8位数据,这个控制面板如下所示:

初始状态下所有的开关均置为0。其中右下角有一个标识为控制端的开关。

这个开关的作用是确定由控制面板还是由外部所连接的其他电路来控制存储器。

如果控制端置0,存储器由其他电路系统接管,控制面板上的其他开关将不起任何作用。

当控制端置1时,控制面板将重新获得对存储器的控制能力。

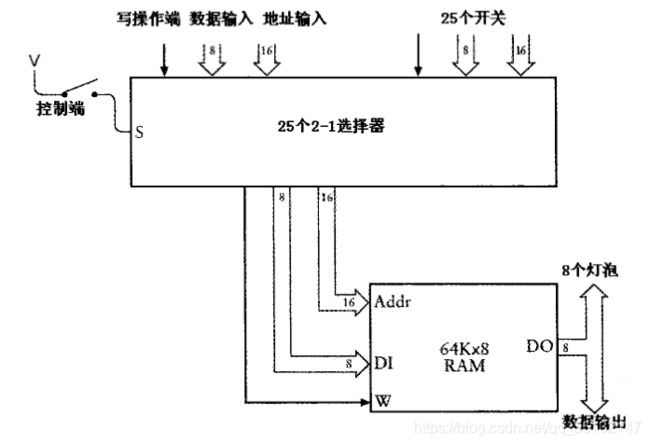

这种功能可以用25个2-1选择器来实现 —— 其中包括16个地址输入端、8个数据输入端,以及1个写操作端。

电路如下图所示:

- 当控制端开关断开时,RAM阵列的地址端、数据输入端和写操作端的数据全部来源于外部信号,也就是在2-1选择器的左上角的输入信号

- 当控制端开关闭合时,RAM阵列的地址端、数据输入端和写操作端的数据来源于控制面板开关发出的信号。

但最终RAM阵列的输出信号都会传输到8个灯泡上或其他可能的地方。

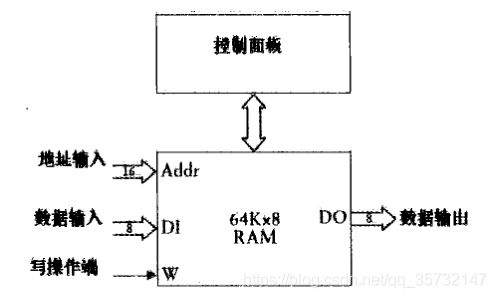

下面这幅是控制面板与64K x 8 RAM阵列的逻辑结构框图:

当控制端开关闭合时,通过操作16个地址开关,可以选择65536个地址中的任何一个。

灯泡的状态将表示该地址中所保存的8位数据。

可以使用8个数据开关表示出一个新数,然后把写操作端置1,从而将数据写入存储器。

64k x 8 的RAM阵列和控制面板这一组合的确很实用,它可以帮助我们存储65536个8位数据并且读取其中的任意一个。

与此同时,它也给其他部件提供了接入系统的机会——需要接入系统的通常是一些电路部件——这些部件可以轻易地读取并利用存储器中存放的数据,还可以把数据写入存储器。

关于存储器有一个问题尤其值得注意,而且需要特别注意:

一个辛辛苦苦装满了65536字节珍贵数据的64K x 8 RAM阵列,如果断掉电源,会发生什么事情呢?

首先所有的电磁铁都将因为没有电流而失去磁性,随着“梆”的一声,金属片将弹回原位,所有继电器将还原到未触发状态。

RAM中存储的数据呢?它们将如风中残烛般消失在黑暗中。

正因为如此,随机访问存储器也被称为易失性存储器。

为了保证存储数据不丢失,易失性存储器需要恒定的电流。