EDA原理及应用 个人笔记

在学,就是一点点笔记,有错误的话,望请大佬指正,非常感谢。

目录

- 1.1 VHDL结构

- 1.1 实体和端口模式

- 1.2 结构体

- 1.3 库和库的种类

- 1.4 库和程序包的调用方法

- 1.5 配置

- 2.1 VHDL结构

- 2.2 VHDL文字规则

- 2.2.1 数字

- 2.2.2 关键词

- 2.2.3 标识符及其表述规则

- 2.2.4 文件取名和存盘

- 2.2.5 规范的程序书写格式

- 2.3 VHDL数据对象

- 2.3.1 常数

- 2.3.2 变量

- 2.3.3 信号

- 3.1 VHDL数据类型

- 3.1.1 BIT和 BIT_VECTOR类型

- 使用

- 3.1.2 STD_LOGIC和 STD_LOGIC_VECTOR类型

- 3.1.3 整数类型 INTEGER

- 3.1.4 布尔数据类型 BOOLEAN

- 3.1.5 SIGNED和 UNSIGNED类型

- 3.1.6 例题

- 3.1.7 其他预定义类型

- 3.1.8 数据类型转换函数

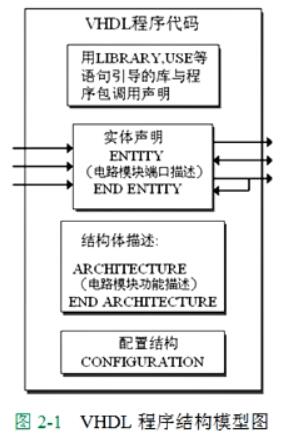

1.1 VHDL结构

1.1 实体和端口模式

实体的端口描述主要有四类:

- IN端口----输入端口

- OUT端口----输出端口

- INOUT端口----输入输出端口

- BUFFER端口----缓冲端口(与INOUT端口功能类似,区别在于当需要输入数据时,只允许回读输出的数据,也就是允许反馈。)

ENTITY 实体名 IS

[GENERIC ( 参数名: 数据类型 );]

[PORT ( 端口表: 数据类型);]

END ENTITY 实体名;

1.2 结构体

ARCHITECTURE 结构体名 OF 实体名 IS

[说明语句]

BEGIN

[功能描述语句]

END ARCHITECTURE 结构体名;

1.3 库和库的种类

LIBRARY WORK ;

LIBRARY STD ; //打开sTD库

USE STD.STANDARD.ALL ; //能够使用STD库中的所有内容

重点所需要的库有:

- IEEE库

- STD库

- WORK库

- VITAL库

1.4 库和程序包的调用方法

LIBRARY 库名;

USE 库名.程序包名.ALL ;

USE 库名.程序包名.项目名 ;

USE 库名.程序包名.ALL;

例子:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.STD_ULOGIC ;

USE IEEE.STD_LOGIC_1164.RISING_EDGE ;

1.5 配置

2.1 VHDL结构

2.2 VHDL文字规则

2.2.1 数字

- 整数

5, 678, 0, 156E2(=15600), 45_234_287(=45234287)

- 实数

1.335, 88_670_511.453_909(=88670551.453909), 1.0, 44.99E-2(=0.4499)

- 文字示例

SIGNAL d1,d2,d3,d4,d5,: INTEGER RANGE 0 TO 255;//全部定义为整数类型

d1 <= 10#170#; //向d1赋值10#170#(十进制表示,等于170)

d2 <= 16#FE#; //(十六进制表示,等于254)

d3 <= 2#1111_1110#; //(二进制表示,等于254)->也是整数类型!

d4 <= 8#376#; //(八进制表示,等于254)

d5 <= 16#A#E3; //(六进制表示,等于16#A000#)

- 物理量文字

60s(60秒),100m(100米),k(千欧姆),177A(177安培)

- 字符串

data1 <= B"1_1101_1110" //二进制数数组,位矢数组长度是9位

data2 <= O"15" //八进制数数组,位矢数组长度是6位

data3 <= X"AD0" //十六进制数数组,位矢数组长度是12

data4 <= B"101_010_101_010" //二进制数数组,位矢数组长度是12

data5 <= "101_010_101_010" //表达错误,缺B

data6 <= "101010101010" //表达正确。这里可以略去B,但不可加下划线

data6 <= "0AD0" //表达错误,缺x

2.2.2 关键词

2.2.3 标识符及其表述规则

- 有效的字符:包括26个大小写英文字母,数字包括0~9以及下划线“_”。

- 任何标识符必须以英文字母开头。

- 必须是单一下划线“_”,且其前后都必须有英文字母或数字。

- 标识符中的英语字母不分大小写。

- 允许包含图形符号(如回车符、换行符等),也允许包含空格符。

| 错误 | 原因 |

|---|---|

| _Decoder_1 | 起始为非英文字母 |

| 74Ls164 | 起始为数字 |

| Sig_#N | 符号“#”不能成为标识符的构成 |

| Not-Ack | 符号“-”不能成为标识符的构成 |

| RyY_RST_ | 标识符的最后不能是下划线"_" |

| data_ _BUS | 标识符中不能有双下划线 |

| return | 关键词 |

2.2.4 文件取名和存盘

- 文件名必须与实体名相一致

- 放在某文件夹中(非中文文件名),不要存在根目录或桌面上,否则不符合WORK库的要求。

2.2.5 规范的程序书写格式

2.3 VHDL数据对象

2.3.1 常数

初始化:

CONSTANT 常数名:数据类型:= 表达式;

例如:

CONSTANT FBT : STD_LOGIC_VECTOR := "010110"; //定义常数为标准位矢类型

CONSTANT DATAIN : INTEGER :=15 ; //定义常数为整数类型

2.3.2 变量

初始化:

VARIABLE 变量名 : 数据类型 := 初始值 ;

例如:

VARIABLE a : INTEGER RANGE 0 TO 15; //变量a定义为整数类型,取值范围是0~15

VARIABLE d : STD_LOGIC := '1'; //变量d定义为标准逻辑位数据类型,初始值是1

赋值:

目标变量名 := 表达式 ;

例如:

VARIABLE x,y : INTEGER RANGE 15 DAWNTO 0 ; //分别定义变量x和y为整数类型

VARIABLE a,b : STD_LOGIC_VECTOR(7 DOWNTO 0) ;

x := 11 ; //整数直接赋值,这是因为x的类型是整数类型

y := 2 + x; //运算表达式赋值,y也是整数变量

a := b ; //b向a赋值

a(5 DOWNTO 0) := b(7 DOWNTO 2) ; //位矢量类型赋值

2.3.3 信号

初始化:

SIGNAL信号名:数据类型:=初始值;

目标信号名 <= 表达式 AFTER 时间量;注:AFTER是关键词

3.1 VHDL数据类型

VHDL对运算关系与赋值关系中各量的数据类型都有严格要求,VHDL要求设计实体中的每一个常数、信号、变量以及设定的各种参量必须具有确定的数据类型,只有相同数据类型的量才能互相传递和作用。

VHDL中的数据类型又可分成在现成程序包中可以随时获得的预定义数据类型和用户自定义数据类型两大类别。预定义的VHDL数据类型是VHDL最常用、最基本的数据类型。这些数据类型都已在VHDL的标准程序包STANDARD和STD_LOGIC_1164及其他的标准程序包中做了定义。

LIBRARY WORK;

LIBRARY STD; //打开STD库

USE STD.STANDARD.ALL; //能够使用STD库中的所有内容LIBRARY IEEE; //打开STD库

USE IEEE.STD_LOGIC_1164.ALL; //能够使用STD_LOGIC_1164库中的所有内容

3.1.1 BIT和 BIT_VECTOR类型

VHDL的数据类型BIT和BIT_VECTOR,在程序包STANDARD中定义的源代码如

TYPE BIT IS(‘0’, ‘1’);

TYPE BIT_VECTOR IS ARRAY(NATURAL RANGE<>) OF BIT; //属于非限制类数组类型

BIT和 BIT_VECTOR数据类型可以参与多种运算操作,如逻辑运算、关系运算算术远算。若为逻辑运算,其结果仍是逻辑位的数据类型。

例子:

在4选1多路选择器中,将端口信号a,b,c,d的数据类型都定义为BIT,则表达式应为:

a,b,c,d: IN BIT;

这时,它们的取值范围,或者说数据范围即被限定在逻辑位“1”和“0”两个值的范围内。

使用

以下为BIT和 BIT_VECTOR类型的定义和使用实例:

SIGNAL x, Y : BIT;

SIGNAL A, B : BIT_VECTOR(3 DOWNYO 0)

。。。

x <= '1' ; //对BIT类型的信号x赋值'1'

A <= "1101" ; //赋值后,A(3)、A(2)、A(1)、A(0)分别等于'1'、'1'、'0'、'1'

B(2 DOWNTO 1) <= A(3 DOWNTO 2); //赋值后,B(2)=A(3),B(1)=A(2)

B(2 DOWNTO 0) <= x & Y & '1' ; //赋值后,B(2)=x、B(1)=y,B(O)='1'

注:BIT和 BIT_VECTOR类型的定义是包含在HDL标准程序包 STANDARD中的,而程序包 STANDARD包含于VHDL标准库STD中,由于STD符合VHDL语言标准,因此在定义BIT或 BIT_VECTOR类型的程序中不必像使用EEE库那样必须显式的打开STD库和STANDARD程序包。

3.1.2 STD_LOGIC和 STD_LOGIC_VECTOR类型

标准逻辑数据类型 STD_LOGIC被定义在 STD_LOGIC_VECTOR程序包中,而此程序包属于IEEE库,这就是为什么定义端口为 STD_LOGIC类型前必须打开IEEE库和STD_LOGIC_VECTOR程序包的原因。

TYPE STD_LOGIC IS (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’, ‘H’, ‘-’); //有九种取值

| Value | 表示 |

|---|---|

| ‘U’ | 未初始化的 |

| ‘X’ | 强未知的 |

| ‘0’ | 强逻辑0 |

| ‘1’ | 强逻辑1 |

| ‘Z’ | 高阻态 |

| ‘W’ | 弱未知的 |

| ‘L’ | 弱逻辑0 |

| ‘H’ | 弱逻辑1 |

| ‘-’ | 忽略 |

预定义标准逻辑位矢量 STD_LOGIC_VECTOR和 STD_LOGIC一样,也是定义在STD_LOGIC_1164程序包中,在使用STD_LOGIC_VECTOR时,必须注明其数组宽度,即位宽。

B : STD_LOGIC_VECTOR(7 DOWNTO 0); //元素排序从高到低

SIGNAL A : STD_LOGIC_VECTOR(1 TO 4);

根据以上两式的定义,对B的赋值方式如下:

B <= “01100010” //可以对B赋值8位二进制数"01100010"

B(4 DOWNTO 1) <= “1101” ; //赋值后,其中的B(4)为’1’

B(7 DOWNTO 4) <= A ; //其中B(6)等于A(2),B(7)等于A(1)

3.1.3 整数类型 INTEGER

定义为整数类型 INTEGER的数代表正整数、负整数和零,整数类型与算术整数相似,可以使用运算操作符,如“+”,“-”,“*”,“/”进行算术运算。

SIGNAL Q : INTEGER RANGE 15 DOWNTO 0;

1 十进制整数

35 十进制整数

1.0E3 十进制整数,等于十进制整数1000

16#D9# 十六进制整数,等于十六进制数D9H

8#720# 八进制整数,等于八进制数720O

2#11010010# 二进制整数,等于二进制数11010010B

Q: BUFFER NATURAL RANGE 15 DOWNTO 0;

该类型与BIT一样,不显式打开STD库和程序包 STDANDARD。

3.1.4 布尔数据类型 BOOLEAN

布尔类型有 FALSE和TRUE两种,不属于数值,不能用作运算。

TYPE BOOLEAN IS(FALSE, TRUE);

3.1.5 SIGNED和 UNSIGNED类型

在IEEE库加入的程序包STD_LOGIC_VECTOR中定义的数据类型有:无符号数据类型 UNSIGNED,有符号数据类型 SIGNED以及小整型 SMALL_INT,如果将信号或变量等数据对象定义为这几种数据类型,就可以使用此程序包中定义的运算符。

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_VECTOR.ALL ;

定义:

TYPE UNSIGNED IS ARRAY( NATURAL RANGE <> )OF STD_LOGIC ;

TYPE SIGNED IS ARRAY( NATURAL RANGE <> )OF STD_LOGIC ;

从定义代码上看,似乎 UNSIGNED和 SIGNED类型属于 STD_LOGIC类型,其实,只是表述形式类似 STD_LOGIC,运算操作上是按照整数类型进行的。

UNSIGNED用于无符号数的运算,代表一个无符号的数值,在综合器中,这个数值被解释为一个二进制数,这个二进制数的最左位是其最高位,例如,十进制的8可以表示如下:

UNSIGNED’(“1000”)

如果要定义一个变量或信号的数据类型为 UNSIGNED,则其位矢长度越长,所代表的的数越大。

以下是两个无符号数据定义的示例:

VARIABLE var : UNSIGNED(0 TO 10);

SIGNAL sig : UNSIGNED(5 DOWNTO 0);

SIGNED数据类型表示一个有符号的数值,综合器将其解释为补码,此数的最高位是符号位。例如:

SIGNED’(“0101”)代表+5,5(去除符号位得到)

SIGNED’("1011”)代表-5(去除符号位-1取反得到)

若将上例中的var定义为 SIGNED数据类型,则数值意义就不同了:

VARIABLE var : SIGNED(0 To 10);

其中变量var有11位,最左位var(0)是符号位。

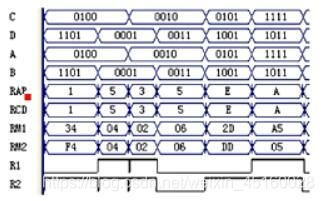

3.1.6 例题

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_ARITH.ALL ;

ENTITY COMP IS

PORT(C, D : IN UNSIGNED(3 DOWNTO 0);

A, B : IN SIGNED(3 DOWNTO 0);

RCD : OUT UNSIGNED(3 DOWNTO 0);

RAB : OUT SIGNED(3 DOWNTO 0);

RM1 : OUT UNSIGNED(7 DOWNTO 0);

RM2: OUT SIGNED(7 DOWNTO 0);

R1, R2 : OUT BOOLEAN );

END ENTITY COMP;

ARCHITECTURE ONE OF COMP IS

BEGIN

R1 <= (C>D);R2 <= (A>B);

RCD <= C+D; RAB <= A+B;

RM1 <= C*D; RM2 <= A*B;

END ARCHITECTURE ONE;

3.1.7 其他预定义类型

- 字符类型

‘A’ ‘a’

- 实数类型

1.0 十进制浮点数

0.0 十进制浮点数

65971.3333333 十进制浮点数

65_971.333_3333 与上一行等价

8#43.6#e+4 八进制浮点数

43.6E-4 十进制浮点数

- 字符串类型

VARIABLE string_var : STRING (1 To 7 );

string_var := “a b c d”;

- 时间类型

TYPE time IS RANGE -2147483647 TO 2147483647

units

fs ; -- 飞秒,VHDL中的最小时间单位

ps = 1000fs ; -- 皮秒

ns = 1000ps ; -- 纳秒

us = 1000ns ; -- 微秒

ms = 1000us ; -- 毫秒

sec = 1000ms ; -- 秒

min = 60sec ; -- 分

hr = 60min ; -- 时

end units ;

3.1.8 数据类型转换函数

可综合的数据类型归纳:

| 数据类型 | 可综合的取值范围 |

|---|---|

| bit, bit_vector | ‘1’, ‘0’ |

| std_logic, std_logic_vector | ‘X’, ‘0’, ‘1’, ‘Z’ |

| boolean | ture, false |

| natural | 0~2147483647 |

| Integer | -2147483647~+2147483647 |

| signed | -2147483647~+2147483647 |

| unsigned | 0~2147483647 |

| 用户自定义类型 | 用户自定义数组或元素 |

| 数组类型(aray) | 可综合数据类型的组合 |

| 子类型(subtype) | 数据类型的子集 |

IEEE库类型转换函数表:

| 函 数 名 | 功能 |

|---|---|

| 所在程序包:STD_LOGIC_1164 | |

| to_stdlogicvector(A) | 由 bit_vector类型转换为 std_logic_vector |

| to_bitvector(A) | 由 std_logic_vector转换为 bit_vector |

| to_stdlogic(A) | 由bit转换成 std_logic |

| to_bit(A) | 由 std_logic类型转换成bit类型 |

| 所在程序包:STD_LOGIC ARITH | |

| conv_std_logic_vector(A, 位长) | 将 integer转换成 std_logic_vector类型,A是整数 |

| conv_integer(A) | 将 std_logic_vector转换成 integer |

| conv_unsigned(A, 位长) | 将unsigned, signed, integer类型转换为指定位长的unsigned类型 |

| conv_signed(a, 位长) | 将unsigned, signed, integer类型转换为指定位长的signed类型 |

| 所在程序包:STD_LOGIC_UNSIGNED | |

| conv_integer(A) | 由std_logic_vector转换成 integer |