FPGA 考试题目

一、读程题.以下是一段4位计数器的yerilog程序,试填空使程序完整.(10分)

module count4(out,reset,clk);

output[3:0]out;

input reset,clk;

reg [3:0]out;

always@(posedgeclk)

begin

if(reset)

out=4'b0000:/复位

else out= out + 1'b1;/计数

end

endmodule

二、编程题.有一个2路数据比较器,输入A、B(位宽为2),三个输出ABB、AEB、ASB分别代表A>B、A=B和A

源程序:

//2位数据比较器——采用行为描述方式

//comp_2_ex3.v

module comp_2_ex3(A,B,ABB,AEB,ASB);

input [1:0]A,B;

output ABB,AEB,ASB;

reg ABB,AEB,ASB;

always@(A or B)

begin

if(A>B)

ABB<=1'b1;

AEB<=1'b0;

ASB<=1'b0;

if(A==B)

ABB<=1'b0;

AEB<=1'b1;

ASB<=1'b0;

if(A<B)

ABB<=1'b0;

AEB<=1'b0;

ASB<=1'b1;

end

endmodule

TestBench程序:

`timescale 1us/1ps //延时单位为1us,精度为1ps

module tb_comp_2_ex3();

reg [1:0] A,B;

parameter delay=5; //每产生一个结果,延时5us

//例化

comp_2_ex3 instance1(

.A(A),

.B(B)

);

//初始化赋值4组样例

initial

begin

A=2'b01,B=2'b00; //ABB

#delay

A=2'b00,B=2'b00; //AEB

#delay

A=2'b01,B=2'b01; //AEB

#delay

A=2'd00,B=2'b01; //ASB

#delay;

end

endmodule

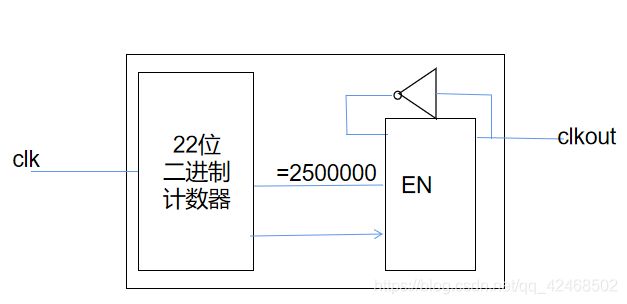

三、编程题。某系统时钟频率是5MHz,试用Verilog.语言设计一个分频器获得1Hz的频率:

(1)画出电路框图

(2)写出其VerilogHDL程序。(20分)

//div5000000.v

module div5000000(clk,clkout);

input clk;

output clkout;

reg clkout;

reg [22:0] cnt;

always@(posedge clk)

begin

if(cnt==22'd2500000)

cnt<=1'b0;

else cnt=cnt+1'b1;

end

always@(posedge clk)

begin

if(cnt==22'd2500000)

clkout=~clkout;

else;

end

endmodule

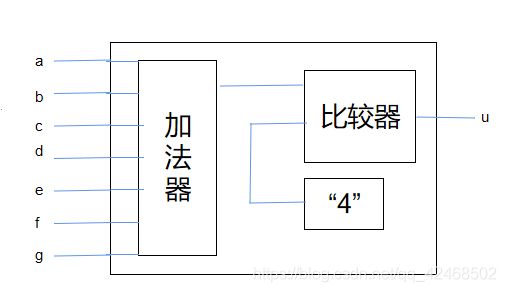

四、编程题。利用VerilogHDL语言设计一个7人表决器电路,使其能够满足功能:7人投票,票数大于等于4则表决通过,否则不通过:

(1)要求画出该电路框图

(2)写出其VerilogHDL程序。(25分)

//seven_voter_ex.v

module seven_voter_ex(a,b,c,d,e,f,g,u);

input a,b,c,d,e,f,g;

output u;

wire [1:0] add_result;

assign add_result=a+b+c+d+e+f+g;

assign u=(add_result >=4)? 1'b1 : 1'b0;

endmodule

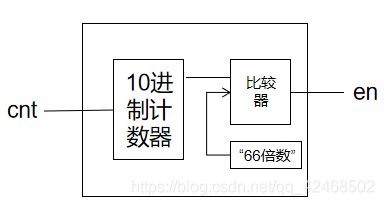

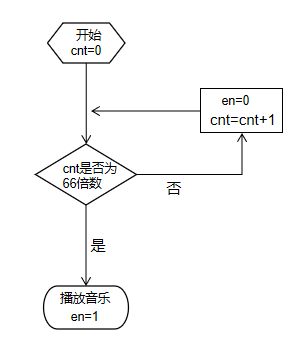

五、某商场为了促销,希望给每天第66位(比如第66位、132位、198位…)进店的消费者小礼品,试用VerilogHDL语言设计一自动电路满足下面的需求:当满足条件的消费者进店时播放音乐,迎宾小姐上前给予礼品。(1)画出电路框图(2)画出程序流程图(3)写出其yerilogHDL程序。(30分)

//voter_ex.v

module voter_ex(cnt);

input cnt;

reg[22:0]cnt=0;

output en;

always@(cnt)

begin

if(cnt==22'd66||22'd132||22'd198)en=1;

else cnt=cnt+1'b1 ;en=0;

end

endmodule