一周搞定期末考系列之《数字电子技术》

数电老师给出了期末考试的提纲,我们就通过这个来按知识点和例题分析一波

一、各种进制之间的转换(数值信息)

1、任意进制数转十进制数

方法:按位权展开

2、十进制转其他进制

方法:基数乘除法

整数部分:除r取余,逆序排列

小数部分:乘r取整,顺序排列

3、其他进制转换

二进制转八进制:3位2进制转一位八进制数

二进制转十六进制:4位2进制转一位十六进制数

八进制转十六进制:先转二进制后再转十六进制

二进制转余三码:先转为十进制,后按位转化位余三码

PS:从小数点开始转化,不足补零

二、主要的编码方式(非数值信息)

1、有权码:

8421BCD码

5421BCD码

2421BCD码

2、无权码:

余三码(8421BCD码+3)

3、格雷码:码距为1

4、二进制的原码、反码、补码

反码:保持符号位,其他按位取反(正数反码与原码相同)

补码:在反码的基础上,加一(正数补码与原码相同)

三、逻辑代数化简的公式和法则

1、异或(=1)和同或(=)

异或:AB’+A’B

同或:AB +A’B’

2、常用公式

A+A’B = A+B

A+AB = A

含相同元素的多项可删,含相同反元素的多项可删反项

AB+A’C+BC = AB + A’C

AB+A’C+BCD = AB + A’C

(A+B)(A’+C)(B+C) = (A+B)(A’+C)

消除多余项

A+A=A

A+A’=1

配项法

PS:A+BC=(A+B)(A+C)

3、对偶和反演定理

4、卡诺图化简法

PS:

i.对于一个确定的逻辑函数:真值表和卡诺图唯一

ii.卡诺图中圈0的逻辑表达式的反函数

iii.注意利用无关项对逻辑表达式进行化简

5、竞争和冒险的判别和消除方法

竞争:门电路两个输入信号同时向相反的逻辑电平跳变

竞争-冒险:由于竞争而在电路输出端可能产生尖峰脉冲,若后继负载电路是一个对脉冲敏感的电路,这种尖峰脉冲可能使负载电路发生误操作

a.偏一冒险(主要存在于与或电路中)

F = A+A’

PS:如Y=AB+AC’,当B=C=1时,Y=A+A’,存在偏一冒险

b.偏零冒险(主要存在于或与电路中)

F = AA’

PS:如Y=(A+B)(B’+C),当A=C=0时,Y=BB’,存在偏零冒险

c.消除方法

i.增加多余项

ii.增加选通电路

iii.利用滤波电路

d.利用卡诺图发现静态冒险

若卡诺图中,圈与圈间有相切现象,则可能出现静态冒险。

四、组合逻辑电路设计(从问题抽象化到画出电路图)

1、进行逻辑抽象,得到真值表或逻辑表达式

2、选择器件的类型

3、逻辑化简或变换成适当的形式

4、电路处理,得到电路图

五、常用组合逻辑器件

1、加法器

i.列出真值表

ii.写出逻辑表达式

iii.画出逻辑图

2、编码器(仍何时刻只有一个输入端有效)

例:8-3编码器(三位二进制编码器)

i.确定编码矩阵和编码表

ii.由编码表列出二进制代码每一位的逻辑表达式

iii.按此表达式画出用门电路组成的编码电路

3、优先编码器

例:8-3优先编码器

http://www.51hei.com/bbs/dpj-51344-1.html

4、译码器

例:3-8译码器(三位二进制译码器)

i.确定译码矩阵和编码表

ii.由译码矩阵列出译码函数的逻辑表达式

iii.按此表达式画出用门电路组成的编码电路

5、数据选择器

图中,D0-D3是数据输入端,其中A1、A0是数据通道选择控制信号,即地址变量;E是使能端(地址变量对侧),他能控制数据选通是否有效,即禁止数据输入,故又称E端为禁止端。

i.通过图片可以写出,四选一数据选择器的输出逻辑表达式

F = (A1’A0’D0 + A1’A0D1 + A1A0D1 +A1A0D3)E’(当E为低电平有效时)

功能表

| 控制1 | 控制2 | 选择的输出源 |

|---|---|---|

| A1 | A0 | Y |

| 0 | 0 | D0 |

| 0 | 1 | D1 |

| 1 | 0 | D2 |

| 1 | 1 | D3 |

五、各种触发器管脚功能设置及特征方程

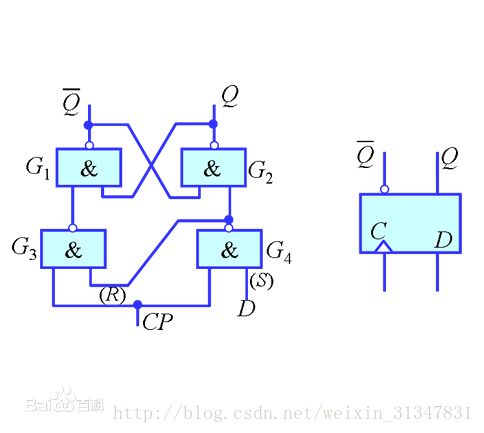

1、基本RS触发器(与非门组成)

状态真值表

| Rd | Sd | Qn | Qn+1 | 说明 |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 不允许 |

| 0 | 0 | 1 | 1 | 不允许 |

| 0 | 1 | 0 | 0 | 置零 |

| 0 | 1 | 1 | 0 | Qn+1=0 |

| 1 | 0 | 0 | 1 | 置一 |

| 1 | 0 | 1 | 1 | Qn+1=1 |

| 1 | 1 | 0 | 0 | 保持 |

| 1 | 1 | 1 | 1 | Qn+1=Qn |

特征方程:Qn+1= Sd’+RdQn

PS : 若为或非门,则特征方程为Qn+1=Sd+Rd’Qn

| Rd | Sd | Qn | Qn+1 | 说明 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 保持 |

| 0 | 0 | 1 | 1 | Qn+1=Qn |

| 0 | 1 | 0 | 1 | 置一 |

| 0 | 1 | 1 | 1 | Qn+1=1 |

| 1 | 0 | 0 | 0 | 置零 |

| 1 | 0 | 1 | 0 | Qn+1=0 |

| 1 | 1 | 0 | X | 禁止 |

| 1 | 1 | 1 | X | 禁止 |

当CP=1时,触发器工作,S=1时置一,R=1时置零,同位0时保持

特征方程:Qn+1 = S + R’Qn

约束条件:RS = 0

3、D触发器(上升沿触发)

因为钟控RS触发器存在禁止条件,不能同时为1,所以D触发器令R=S’,排除了禁止条件。

状态真值表

| D | Qn | Qn+1 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

特征方程:Qn+1=D

PS:

i.为克服空翻和震荡,应采用CP边沿触发

3、JK触发器(下降沿触发)

| J | K | 动作 | Q | Qnext | 动作 |

|---|---|---|---|---|---|

| 0 | 0 | 保持 | X | X | 不变 |

| 0 | 1 | 设置 | X | 0 | 置零 |

| 1 | 0 | 设置 | X | 1 | 置一 |

| 1 | 1 | 反转 | 1(0) | 1(0) | 反转 |

特征方程:Qn+1=JQn’ + K’Qn

5、

激励方程:观察电路写出输入端表达式

特征方程:根据触发器给出

次态方程:将激励方程带入特征方程

六、时序逻辑电路的分析和设计

时序逻辑电路的分析步骤一般有如下几步

1)看清电路,确定是同步时序电路还是异步时序电路。

2)写出方程。

3)列出状态真值表

4)做出状态转换图

5)进行功能描述

6)画波形图

7)检查自启动能力

时序逻辑电路设计步骤

1)逻辑抽象

i.确定输入输出变量,电路状态数

ii.定义输入输出逻辑状态以及每个电路状态的含义,并对电路状态进行编号

iii.按设计要求列出状态转换表,或画出状态转换图

2)状态化简

若两个状态在相同的输入下有相同的输出,并转换到同一个状态,则称为等价态,等价状态可合并

3)状态分配(编码)

i.确定 触发器数量

ii.给每个状态一个编码(按照一定规律)

4)选定触发器类型

求出状态方程,驱动方程,输出方程

5)画出逻辑图

6)检查自启动

七、单片集成加法计数器(74LS161/74LS90)

1、74LS90(实现2-5-10进制计数)

功能归纳:

1)直接置零。当R都为高电平,S都为低电平时,触发器输出均为零。实现清零功能。

2)置9(输出1001)当S都为高电平时,实现置9功能,它是异步方式置9

3)计数。当RS均为低电平时,具有计数功能

4)功能拓展。

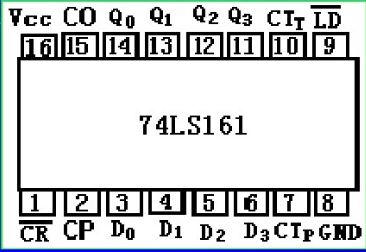

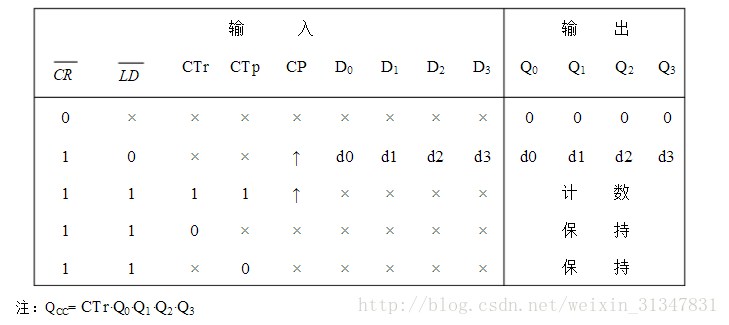

2、74LS161(同步四位二进制计数器)

功能描述:

1)异步清零。当清零端Cr=0时,立即清零,与CP无关

2)同步预置。当预置端LD=0,Cr=1时,在CP处于上升沿时,将数据送入计数器

3)保持。当LD=Cr=1时,只要控制端P,T有低电平,就使每级触发器J=K=0,处于维持态。

4)计数。当LD=Cr=P =T=1时,电路时模16同步递增计数器。

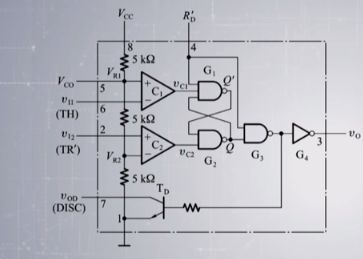

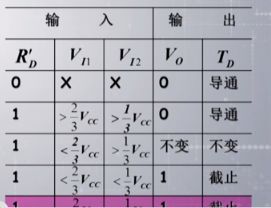

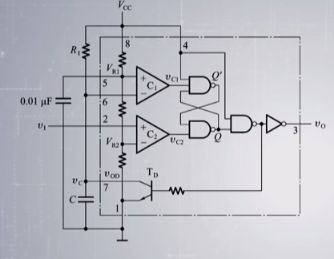

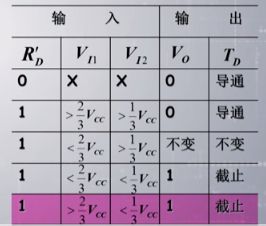

八、555定时器的应用电路分析

单稳态电路

多谐振荡器

施密特电路