FPGA笔试面试题之设计篇

1、描述一个交通信号灯的设计。(仕兰微电子)

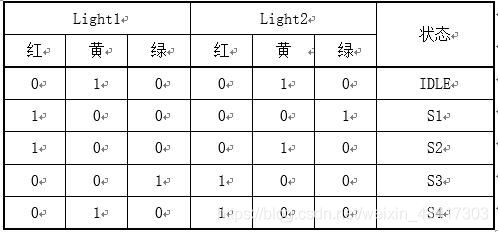

东西南北四个方向,东西与南北两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。五个状态如下:

分别设计状态机控制程序,计数程序,顶层程序和测试程序

module top_light(clk,rst_n,light1,light2)

input clk,rst_n;

output [2:0] light1;

output [2:0] light2;

wire [5:0] cnt;

StateMachine_light StateMachine_light_m0

(

.clk (clk),

.rst_n (rst_n),

.count (cnt),

.light1 (light1),

.light2 (light2)

);

count_light count_light_m0

(

.clk (clk),

.rst_n (rst_n),

.count (cnt)

);

endmodule

module StateMachine_light(clk,rst_n,count,light1,light2)

input clk;

input rst_n;

input [5:0] count;

output [2:0]light1;

output [2:0]light2;

reg [2:0] light1,light2;

reg [2:0] state;

parameter idle = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

begin

state <= idle;

light1 <=3'b111;

light2 <=3'b111;

end

else

begin

case(state)

idle:

begin

state <= s1;

light1 <= 3'b100;

light2 <= 3'b001;

end

s1:if(count == 'd25)

begin

state <= s2;

light1 <= 3'b100;

light2 <= 3'b010;

end

s2:if(count == 'd30)

begin

state <= s3;

light1 <= 3'b001;

light2 <= 3'b100;

end

s3:if(count == 'd55)

begin

state <= s4;

light1 <= 3'b010;

light2 <= 3'b100;

end

s4:if(count == 'd60)

begin

state <= s1;

light1 <= 3'b100;

light2 <= 3'b001;

end

endcase

end

end

endmodule

module count_light(clk,rst_n,count)

input clk;

input rst_n;

output count;

reg [5:0] count;

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

count <= 'd0;

else if(count <'d60)

count <= count +1;

else

count <= 'd0;

end

endmodule

module tb_light;

reg clk,rst_n;

wire[2:0] light1,light2;

wire[5:0] count;

top_light u3(count,clk,rst_n,light1,light2);

always

#5 clk = ~clk;

initial

begin

clk <= 1;

rst_n <= 0;

#5 rst_n <= 1;

end

endmodule

2、Verilog实现接受1,2,5分钱的卖报机,每份报纸5分钱。(扬智电子笔试)

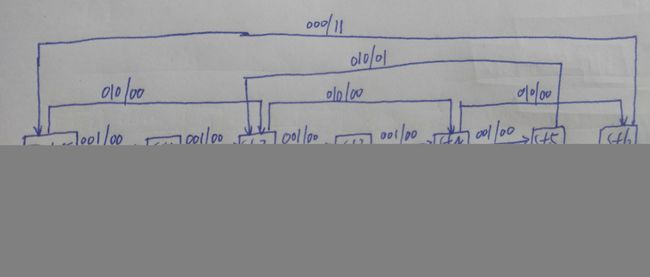

(1)手绘状态机如下:

(2)verilog代码如下:

module machine_125

(

input clk;

input rst_n;

input [2:0] din; //din[001]输入1分 din[010]输入2分 din[100]输入5分

output [1:0] dout //dout[01]输出报纸 dout[11]找1分和报纸

);

parameter idle = 0,

s1 = 1,

s2 = 2,

s3 = 3,

s4 = 4,

s5 = 5,

s6 = 6;

reg [2:0] curr_state, next_state;

reg dout;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

curr_state <= idle;

else

curr_state <= next_state;

end

always @(curr_state or din)

begin

case(curr_state)

idle:

begin

if(din == 3'b001)

next_state <= s1;

else if(din == 3'b010)

next_state <= s2;

else if(din == 3'b100)

next_state <= s5;

else

next_state <= idle;

end

s1:

begin

if(din == 3'b001)

next_state <= s2;

else if(din == 3'b010)

next_state <= s3;

else

next_state <= s1;

end

s2:

begin

if(din == 3'b001)

next_state <= s3;

else if(din == 3'b010)

next_state <= s4;

else

next_state <= s2;

end

s3:

begin

if(din == 3'b001)

next_state <= s4;

else if(din == 3'b010)

next_state <= s5;

else

next_state <= s3;

end

s4:

begin

if(din == 3'b001)

next_state <= s5;

else if(din == 3'b010)

next_state <= s6;

else

next_state <= s4;

end

s5:

begin

if(din == 3'b001)

next_state <= s1;

else if(din == 3'b010)

next_state <= s2;

else if(din == 3'b100)

next_state <= s5;

else

next_state <= idle;

end

s6:

begin

if(din == 3'b000)

next_state <= idle;

else

next_state <= idle;

end

default:

next_state <= idle;

endcase

end

always @(posedge clk)

begin

if(next_state == s5)

dout <= 2'b01;

else if(next_state == s6)

dout <= 2'b11;

end

endmodule

3、设计一个自动饮料售卖机,饮料10分钱,硬币有5分和10分两种,并考虑找零:

(1)画出fsm(有限状态机);

(2)用verilog编程,语法要符合fpga设计的要求;

(3)设计工程中可使用的工具及设计大致过程。

(1)状态机如下:在状态机的选择上,虽然这个逻辑比较简单,还是选择了二段式状态机。其优点,第一,组合逻辑和时序分开了。其二,比三段式节约资源

(2)Verilog编程

machine_5_10

(

input clk,

input rst_n,

input [1:0] din, //00无输入 01输入5分 10输入10分

output [1:0] dout //01出饮料 11找5分出饮料

);

reg curr_state, next_state;

parameter idle = 0,

st1 = 1;

always @(posedge clk or rst_n)

begin

if(!rst_n)

next_state <= idle;

else

curr_state <= next_state;

end

always @(curr_state or din)

begin

case

idle:

begin

if(din == 2'b01)

next_state <= s1;

else if(din == 2'b10)

begin

dout <= 2'b01;

next_state <= idle;

end

else

next_state <= idle;

end

s1:

begin

if(din == 2'b01)

begin

dout <= 2'b01;

next_state <= idle;

end

else if(din == 2'b10)

begin

dout <= 2'b11;

next_state <= idle;

end

end

default:

next_state <= idle;

endcase

end

(3)设计工程中可使用的工具及设计大致过程

①功能定义与器件选型

②设计输入: ultra

③功能仿真:modesim

④逻辑综合:quartus ii 或者 ise,vivado的逻辑综合器

⑤实现布局布线:pin planner

⑥时序仿真:modesim

⑦静态时序仿真: timequest

⑧上板调试。quartus 的signal Tap或者ise的chipscope

5、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx,其中,x为4位二进制整数输入信号。y为二进制小数输出,要求保留两位小数。电源电压为3~5v假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程。(仕兰微电子)

参考:

(1)https://blog.csdn.net/sunshinelifes/article/details/83449698

(2)https://blog.csdn.net/dongdongnihao_/article/details/79954335