FPGA基础知识(五)系统集成知识

本文档重点探讨vivado软件的使用和系统集成的相关知识。

完成此过程可以参阅的文档有

UG892: Vivado Design Suite User Guide, Design Flows Overview

背景:我们用vivado HLS对相关软件生成了相应的IP core,现在需要对IP core进行系统集成,形成完整的设计。

目录

一、明确任务

UG893:Using the vivado IDE.

UG893 chapter 3 :Using project mode

Project mode的优点:

不同类型的project

二、IP相关

Working with IP

在设计中运用IP的可用方法有:

Configuring IP

生成IP output products

运用IP core containers

Out-of-context design flow

IP constraints

Validating the IP

Packaging custom IP与IP 子系统

创建IP子系统

设计辅助

用plaform board flow

Validation IP子系统

生成block design的output products

把block design集成为top-level design

逻辑仿真

Compile simulation libraries

一、明确任务

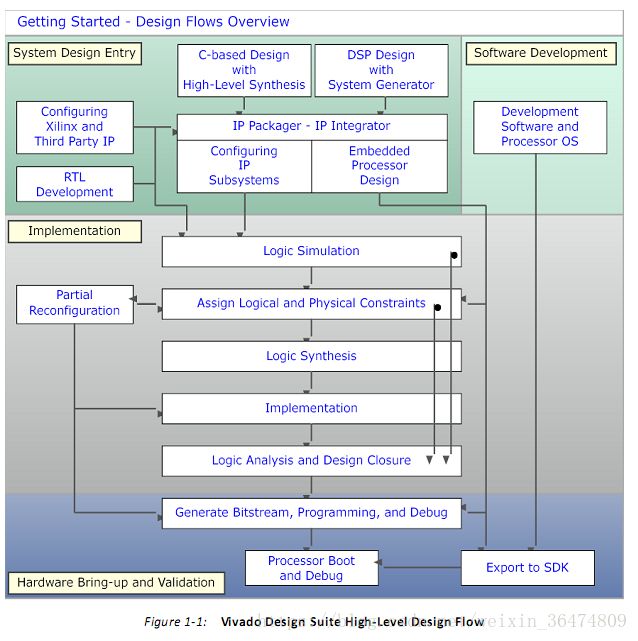

为了确定下步需要怎么做,我们需要明白vivado design suite,包括三个软件,第一个vivado HLS,用于将c语言生成相应的IP core,第二个vivado,用于将相应的模块生成系统并且可以用单片机控制的系统。第三个SDK,用于生成应用级的FPGA。

通过此流程,我们可以确定我们下一步的任务是学习使用vivado软件。

design flows属于HLS。

通过此流程我们发现下一步需要做的是IP package and IP integrate。其中,IP可以通过AXI4总线协议创建IP子系统。

需要看文档UG892中关于vivado IDE(integrated design environment)的部分

UG893:Using the vivado IDE.

Tcl是经常出现的一个文件,但是tcl到底是什么意思呢?tcl是一种面向ASIC和FPGA的一种近乎标准的脚本语言。

相应的设计分project mode和non-project mode,看上去non-project mode相对较为抽象,多用命令行来进行相应的设计,难度相对较大;project mode的步骤和意义文档中给的相对详细一些,并且有相应的GUI界面,所以我们采用project mode来进行,重点看文档中non-project mode

UG893 chapter 3 :Using project mode

有RTL-based projects, netlist-based projects(?),可以运用tcl commands 或者tcl scripts来进行porject mode.在IDE中,你会看到当前设计的状态,运行结果,生成的报告和信息。你可以创建或者修改sources,apply constraints和debug information、configure tool settings,和进行相应的设计任务。

vivado可以在任何设计阶段来打开设计。你可以在RTL elaboration、synthesis、和implementation之后进行analysis和constrains definition。vivado设计工具会compile相应的netlist,并且由目标设备进行相应的constrains 。

Project mode的优点:

- 方便管理project status,HDL sources,constraint files, IP core和block designs

- 产生和存储相应的synthesis和implementation 的结果。

- 具有一些前沿的设计分析功能,包括由implementation results到RTL sources files的cross probing

- 用run strategies 和generates standard reports自动的生成command options

- 支持创建mutiple run以用于configure 与explore available constraint,自动设置command options.

不同类型的project

- RTL project:加入RTL source files and constrains、用vivado IP catalog configure IP、用IP integrator创建IP subsystems、synthesis与implement design,perform design palnning and analysis

- Post-synthesis project:导入第三方netlists, implement the design,perform design planning and analysis.

- I/O planning project:创建空的project以用于IO planning和device exploration用于RTL resources。

- Imported project:用已有的ISE design suite导入已有project sources,Xilinx synthesis technology(XST),或者synopsys synplify。

- Configure an example Embedded Evaluation Board project

- Partial Recognition project:这两个可能用不到,先不管

通过之前和上面的大致了解,我们明确了下步工作就是把之前HLS创建的IP用起来。

二、IP相关

Working with IP

vivado design suite创建了一个IP为中心的design flow,可以implement, varify, integrate IP modules。具体内容在UG896 Designing with IP。

可以用IP-XACT protocol来package定制的IP,让相应的IP可以在IP catalog中被找到。Xilinx IP运用AMBA AXI4标准连接来确保快速的系统集成。已有的IP可以加入一个design或者RTL source或者netlist。vivado设计套件也可以读取之前创建的CORE Generator™ tool cores (.xco extension).

在设计中运用IP的可用方法有:

- 用managed IP flow来customized IP与生成相应的products,包括用synthesized design checkpoint(DCP)来保存。更多信息参见UG896:Designing with IP

- 用project或者non-project模式来引入或者读入已经创建的Xilinx core instance(XCI) file. 这是很多人参与的大工程推荐的方法。

- 用IP catalog来从project中加入制作IP,在项目的本地或者外地存储相应的IP,这是小项目推荐的方法。

Configuring IP

IP catalog 可以浏览可用于目标设备的IP,catalog可以显示相应IP的licensing information,version和相应的data sheet。

IP catalog可以显示Included和purchase 的IP,一种收费一种不收费。

可以双击相应的IP来launch相应的configuration wizard初始化IP用于你的设计,在configure IP之后,Xilinx Core Instance(.xci)文件被创建。这个文件包含了所有IP相应的customization options。通过这个工具可以生成所有IP输出的products,这些products包括:HDL for synthesis and simulation, constraints, possibly a test bench, C modules, example designs, etc.

生成IP output products

IP products用specific configuration of the IP来enable synthesis, simulation, and implementation tools ,vivado设计套件会生成以下product:

- Instantiation template

- RTL source files and XDC constraints

- Synthesized design checkpoint (default)

- Third-party simulation sources

- Third-party synthesis sources

- Example design (for applicable IP)

- Test bench (for applicable IP)

- C Model (for applicable IP)

在IP custiomized的design中,你应当尽量生成所有的output products,包括一个synthesized design checkpoint。万一未来的设计中丢失了相应的IP,或者没有包含相应的IP,之前的所有output product还是保留着的。

运用IP core containers

可选的可选择的core container 可以用一个文档表示一个IP从而简化工作,通过这个选项,你可以存储IP configuration files(XCI)和相应的output product用单个的binary的IP core container file(XCIX), 而不是一个松松垮垮的目录结构。XCIX文件与XCI文件工作方式相似,

Out-of-context design flow

OOC design flow可以从IP catalog中synthesis IP,从vivado IP integrator中block design,进行相应的top-level design。OOC flow可以减少设计周期,减少设计迭代次数,并且可以保留和复用synthesis results。

IP constraints

许多IP core包含着在synthesisi和implementation中用到的XDC constraint文件,这些constraints会自动的用在IP catalog中的IP被customized的时候。

Validating the IP

可以通过behavioral、structural logic或者synthesizing IP来verify IP,同时用implementing IP module来validate 相应的时间,功耗,资源消耗等。

相关功能可参看文档UG896 Designing with IP

运用memory IP(?)看不太懂

Packaging custom IP与IP 子系统

这个过程能将做好的IP或者block进行package,这样就能在IP integrator用目录中的IP catalog中。UG1118:Create and packaging custom IP

用IP integrator创建IP subsystems

vivado的IP集成器支持创建IP子系统,和block designs(.bd),用AXI4总线协议把许多个IP连在一起。

用IP集成器可以拖拽和放置IP,用线连接AXI接口或者放置port和interface port来连接IP子系统到top level design。这些IP块可以被打包成sources(.bd)或者在其他应用中被用到。

创建IP子系统

IP集成器可以进行交互的块设计,并且可以成组的configuring和assembling相应的IP。

在block design中引入RTL modules

IP集成器可以快速的加入module或者整个verilog或者VHDL source file。

设计辅助

为了加快创建相应的设计和子系统,IP集成器可以提供自动的block与自动连接。Block automation可以configure基本的processor-based设计和一些复杂的IP子系统,connection automation可以在不同的pins和ports之间自动的创建重复的连接。

用plaform board flow

vivado设计套件可以自动的从board文件中找出相应的IO constrains和IP configuration数据。vivado设计套件知道每个板子的组成,所以可以根据相应的板子customize与configure相应的IP。

IP集成器会展示所有目标板的成分接口,在一个叫Board tab的separate tab中。

Validation IP子系统

IP集成器可以运行一些实时的基础的设计规则并且检查他们。但是仍有一些潜在的出错的风险,例如时钟周期和时钟管脚可能被设置错误。设计工具可以找到这些错误,运行更加完全的validation。(assmebled就是集成,就是表示设计过程中不同的器件被集成在一起。validate就是验证,保证相应的设计不出错)。验证方法可以选择tools>validata design或者通过tcl命令,validate_bd_design

生成block design的output products

在设计完IP子系统之后,你可以生成相应的block design的所有source codes,necessary constraints for the IP cores, and the structural netlist。你可以在source window中右键block design,选择generate output products。或者选择IP integrator>generate block design.

把block design集成为top-level design

一个IP集成器的block design设计可以被集成为更高级别的设计,可以把相应的block design具体化为HDL文件。可以选择IDE source window中的Create HDL wrapper。这样会生成一个最高级别的HDL文件,来为IP集成相应的IP子系统。

逻辑仿真

Compile simulation libraries

vivado软件预编译很多simulation libraries,当simulation script被创建的时候,他们会reference这些之前编译好的libraries。可以在IDE的tools>compile simulation libraries

看这些文档大致熟悉了流程,下面就来搭一些简单的系统实验一下。