NVIDIA安培架构

NVIDIA安培架构

NVIDIA Ampere Architecture In-Depth

在2020年英伟达GTC主题演讲中,英伟达创始人兼首席执行官黄仁勋介绍了基于新英伟达安培GPU架构的新英伟达A100 GPU。本文将介绍新的A100 GPU,并描述NVIDIA安培体系结构GPU的重要新功能。

在现代云数据中心运行的计算密集型应用程序的多样性推动了NVIDIA GPU加速云计算的爆炸式增长。这些密集型应用包括人工智能深度学习(AI deep learning,DL)培训和推理、数据分析、科学计算、基因组学、边缘视频分析和5G服务、图形渲染、云游戏等。从扩展人工智能培训和科学计算,到扩展推理应用程序,再到实现实时对话人工智能,NVIDIA gpu提供了必要的马力来加速当今云数据中心中运行的众多复杂和不可预测的工作负载。

NVIDIA GPU是推动人工智能革命的领先计算引擎,为人工智能训练和推理工作提供了巨大的加速。此外,NVIDIA gpu加速了许多类型的HPC和数据分析应用程序和系统,使您能够有效地分析、可视化数据,并将数据转化为见解。NVIDIA加速计算平台是世界上许多最重要和增长最快的行业的核心。

Introducing the NVIDIA A100 Tensor Core GPU

NVIDIA A100 Tensor Core GPU基于新的NVIDIA安培GPU体系结构,并建立在以前的NVIDIA Tesla V100 GPU的能力之上。它增加了许多新功能,为HPC、AI和数据分析工作负载提供了显著更快的性能。

A100为运行在单个和多个GPU工作站、服务器、集群、云数据中心、边缘系统和超级计算机中的GPU计算和DL应用程序提供了强大的扩展能力。A100 GPU支持构建弹性、多用途和高吞吐量的数据中心。

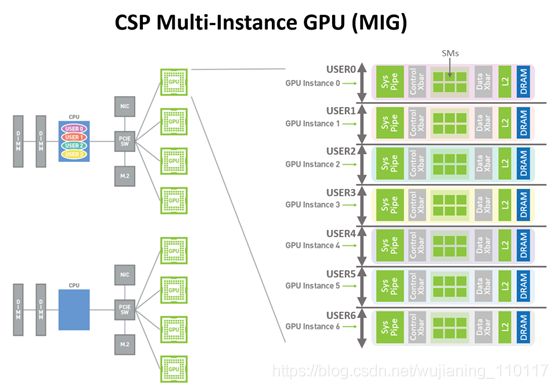

A100 GPU包括一个革命性的新的多实例GPU(MIG)虚拟化和GPU分区功能,这对云服务提供商(csp)特别有利。当配置为MIG操作时,A100允许csp提高其GPU服务器的利用率,以不增加成本的方式提供最多7倍的GPU实例。健壮的故障隔离允许他们安全地划分单个A100 GPU。

A100增加了一个强大的新的第三代Tensor核心,它在增加了对DL和HPC数据类型的全面支持的同时,还增加了一个新的稀疏特性,使吞吐量进一步增加了一倍。

A100中新的TensorFloat-32(TF32)Tensor Core操作为在DL框架和HPC中加速FP32输入/输出数据提供了一条简单的途径,运行速度比V100 FP32 FMA操作快10倍,或在稀疏情况下快20倍。对于FP16/FP32混合精度DL,A100张量核的性能是V100的2.5倍,稀疏性增加到5倍。

新的Bfloat16(BF16)/FP32混合精度张量核运算以与FP16/FP32混合精度相同的速率运行。INT8、INT4和二进制舍入的张量核心加速支持DL推断,A100稀疏INT8的运行速度比V100 INT8快20倍。对于HPC,A100 Tensor Core包括新的符合IEEE标准的FP64处理,其性能是V100的2.5倍。

NVIDIA A100 GPU的架构不仅可以加速大型复杂工作负载,还可以有效地加速许多较小的工作负载。A100支持构建能够适应不可预测的工作负载需求的数据中心,同时提供细粒度的工作负载配置、更高的GPU利用率和改进的TCO。

NVIDIA A100 GPU为人工智能训练和推理工作负载提供了超过V100的异常加速。

Key features

在台积电7NMN7制造工艺上制造的基于NVIDIA安培架构的GA100 GPU为A100供电,包括542亿个晶体管,芯片尺寸为826平方毫米。

A100 GPU streaming multiprocessor

NVIDIA安培体系结构中的新的流多处理器(SM)基于A100张量核GPU显著提高了性能,建立在Volta和Turing SM体系结构中引入的特性的基础上,并增加了许多新功能。

A100第三代张量核增强了操作数共享和效率,并添加了强大的新数据类型,包括:

加速处理FP32数据的TF32张量核心指令

符合IEEE标准的HPC FP64张量核指令

与FP16吞吐量相同的BF16张量核心指令

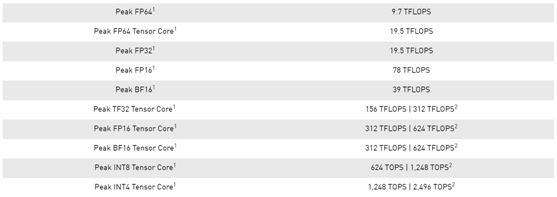

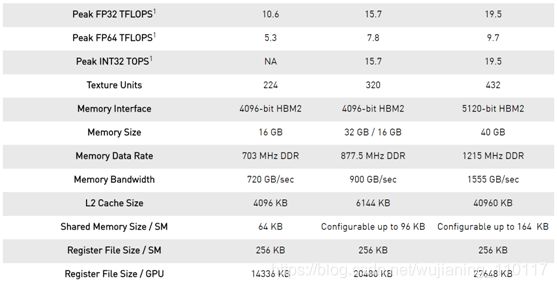

表1. A100张量核心GPU性能规范。

1) 峰值速率基于GPU升压时钟。

2) 使用新稀疏特性的有效TFLOPS/TOPS。

在100个张量核中新的稀疏性支持可以利用DL网络中的细粒度结构稀疏性来加倍张量核操作的吞吐量。稀疏性特征在本文后面的A100介绍细粒度结构稀疏性一节中有详细描述。

A100中更大更快的一级缓存和共享内存单元提供的每SM聚合容量是V100的1.5倍(192 KB/SM,128 KB/SM),可为许多HPC和AI工作负载提供额外的加速。

其他一些新的SM特性提高了效率和可编程性,降低了软件复杂性。

40 GB HBM2 and 40 MB L2 cache

为了满足巨大的计算吞吐量,NVIDIA A100 GPU拥有40gb的高速HBM2内存,其内存带宽达到1555gb/s,比Tesla V100提高了73%。此外,A100 GPU的片上内存显著增加,包括一个比V100大近7倍的40MB二级(L2)缓存,以最大限度地提高计算性能。A100二级缓存采用了一种新的分区交叉结构,提供了V100二级缓存读取带宽的2.3倍。

为了优化容量利用率,NVIDIA安培体系结构为您提供了二级缓存驻留控制,用于管理要保留或从缓存中收回的数据。A100还增加了计算数据压缩,使DRAM带宽和二级带宽提高了4倍,二级容量提高了2倍。

Multi-Instance GPU

新的多实例GPU(MIG)功能允许A100 Tensor Core GPU安全地划分为多达七个单独的GPU实例,用于CUDA应用程序,为多个用户提供单独的GPU资源以加速其应用程序。

使用MIG,每个实例的处理器在整个内存系统中都有独立的路径。片上纵横端口、二级缓存组、内存控制器和DRAM地址总线都是唯一分配给单个实例的。这确保了单个用户的工作负载可以在相同的二级缓存分配和DRAM带宽下以可预测的吞吐量和延迟运行,即使其他任务正在冲击自己的缓存或使DRAM接口饱和。

MIG提高了GPU硬件利用率,同时提供了定义的QoS和不同客户端(如vm、容器和进程)之间的隔离。MIG对于拥有多租户用例的csp尤其有利。它确保了一个客户机不会影响其他客户机的工作或调度,此外还提供了增强的安全性并允许为客户机提供GPU利用率保证。

Third-generation NVIDIA NVLink

第三代NVIDIA高速NVLink互连在A100 GPUs和新NVIDIA nvlswitch中实现,显著提高了多GPU的可扩展性、性能和可靠性。由于每个GPU和交换机有更多的链路,新的NVLink提供了更高的GPU-GPU通信带宽,并改进了错误检测和恢复功能。

第三代NVLink每个信号对的数据速率为50gbit/sec,几乎是V100中25.78gbit/sec速率的两倍。一个A100NVLink在每个方向上提供25GB/秒的带宽,与V100类似,但每个链路使用的信号对数仅为V100的一半。链路总数在A100中增加到12个,而在V100中增加到6个,从而产生600 GB/秒的总带宽,而在V100中为300 GB/秒。

Support for NVIDIA Magnum IO and Mellanox interconnect solutions

A100 Tensor Core GPU与NVIDIA Magnum IO和Mellanox最先进的InfiniBand和以太网互连解决方案完全兼容,可加速多节点连接。

Magnum IO API集成了计算、网络、文件系统和存储,以最大限度地提高多GPU、多节点加速系统的I/O性能。它与CUDA-X库接口,以加速从人工智能和数据分析到可视化等各种工作负载的I/O。

PCIe Gen 4 with SR-IOV

A100 GPU支持PCI Express Gen 4(PCIe Gen 4),通过提供31.5

GB/s而不是15.75 GB/s的x16连接,PCIe 3.0/3.1的带宽翻了一番。更快的速度对于连接到支持PCIe 4.0的cpu的100 gpu和支持快速网络接口(例如200gbit/sec InfiniBand)尤其有利。

A100还支持单根输入/输出虚拟化(SR-IOV),允许为多个进程或虚拟机共享和虚拟化单个PCIe连接。

Improved error and fault detection, isolation, and containment

通过检测、包含并经常纠正错误和故障,而不是强制GPU重置,最大化GPU正常运行时间和可用性至关重要。在大型多GPU集群和单GPU、多租户环境(如MIG配置)中尤其如此。A100 Tensor Core GPU包括新技术,用于改进错误/故障属性、隔离和遏制,如本文后面深入的架构部分所述。

Asynchronous copy

A100 GPU包括一个新的异步复制指令,该指令将数据直接从全局内存加载到SM共享内存中,从而消除了使用中间寄存器文件(RF)的需要。异步复制减少了寄存器文件带宽,更有效地使用了内存带宽,并降低了功耗。顾名思义,异步复制可以在后台完成,而SM正在执行其他计算。

Asynchronous barrier

A100 GPU在共享内存中提供硬件加速屏障。这些障碍是使用CUDA 11的形式,ISO C++ +符合壁垒对象。异步屏障将屏障到达和等待操作分开,可用于将从全局内存到共享内存的异步副本与SM中的计算重叠。它们可用于使用CUDA线程实现生产者-消费者模型。屏障还提供了同步不同粒度的CUDA线程的机制,而不仅仅是扭曲或块级别。

Task graph acceleration

CUDA任务图为向GPU提交工作提供了一个更有效的模型。任务图由一系列操作组成,如内存拷贝和内核启动,这些操作通过依赖关系连接起来。任务图允许定义一次并重复运行执行流。预定义的任务图允许在单个操作中启动任意数量的内核,极大地提高了应用程序的效率和性能。A100增加了新的硬件特性,使任务图中网格之间的路径明显更快。

A100 GPU hardware architecture

NVIDIA GA100 GPU由多个GPU处理集群(gpc)、纹理处理集群(tpc)、流式多处理器(SMs)和HBM2内存控制器组成。

GA100 GPU的完整实现包括以下单元:

· 8 GPCs, 8 TPCs/GPC, 2 SMs/TPC, 16 SMs/GPC, 128 SMs per

full GPU

· 64 FP32 CUDA Cores/SM, 8192 FP32 CUDA Cores per full GPU

· 4 third-generation Tensor Cores/SM, 512 third-generation

Tensor Cores per full GPU

· 6 HBM2 stacks, 12 512-bit memory controllers

GA100 GPU的A100 Tensor Core GPU实现包括以下单元:

· 7 GPCs, 7 or 8 TPCs/GPC, 2 SMs/TPC, up to 16 SMs/GPC, 108

SMs

· 64 FP32 CUDA Cores/SM, 6912 FP32 CUDA Cores per GPU

· 4 third-generation Tensor Cores/SM, 432 third-generation

Tensor Cores per GPU

· 5 HBM2 stacks, 10 512-bit memory controllers

A100 SM architecture

新的A100SM显著提高了性能,建立在Volta和Turing SM体系结构中引入的特性的基础上,并增加了许多新的功能和增强。

A100 SM图如图5所示。Volta和Turing每个SM有8个张量核,每个张量核每个时钟执行64个FP16/FP32混合精度融合乘法加法(FMA)操作。A100 SM包括新的第三代张量核心,每个核心执行256 FP16/FP32 FMA操作每时钟。A100每个SM有四个张量核,每个时钟总共提供1024个密集的FP16/FP32 FMA操作,与Volta和Turing相比,每个SM的计算功率增加了两倍。

本文简要强调了SM的主要功能,并在后面的文章中详细介绍了这些功能:

第三代张量磁芯:

所有数据类型的加速,包括FP16、BF16、TF32、FP64、INT8、INT4和Binary。

新的张量核稀疏特性利用了深度学习网络中的细粒度结构稀疏性,使标准张量核操作的性能提高了一倍。

A100中的TF32 Tensor核心操作为在DL框架和HPC中加速FP32输入/输出数据提供了一条简单的途径,运行速度比V100 FP32 FMA操作快10倍,或在稀疏情况下快20倍。

FP16/FP32混合精度张量核运算为DL提供了前所未有的处理能力,运行速度比V100张量核运算快2.5倍,稀疏性增加到5倍。

BF16/FP32混合精度张量核心运算的运行速度与FP16/FP32混合精度相同。

FP64 Tensor核心操作为HPC提供了前所未有的双精度处理能力,运行速度比V100 FP64 DFMA操作快2.5倍。

具有稀疏性的INT8张量核操作为DL推理提供了前所未有的处理能力,运行速度比V100 INT8操作快20倍。

192kb的共享内存和L1数据缓存,比V100 SM大1.5x。

新的异步复制指令将数据直接从全局内存加载到共享内存中,可以选择绕过一级缓存,并且不需要使用中间寄存器文件(RF)。

新的基于共享内存的屏障单元(异步屏障),用于新的异步复制指令。

二级缓存管理和常驻控制的新说明。

CUDA协作组支持的新的扭曲级缩减指令。

许多可编程性改进以降低软件复杂性。

图6比较了V100和A100 FP16张量核心操作,还将V100 FP32、FP64和INT8标准操作与各自的A100 TF32、FP64和INT8张量核心操作进行了比较。吞吐量是每个GPU的聚合,A100使用FP16、TF32和INT8的稀疏张量核心操作。左上角的图显示了两个V100 FP16张量核,因为V100 SM每个SM分区有两个张量核,而A100 SM分区有两个张量核。

Figure 6. A100 Tensor Core operations compared to V100 Tensor Core and standard operations for different data types.

Figure 7. TensorFloat-32 (TF32) provides the range of FP32 with the precision of FP16(left). A100 accelerates tensor math with TF32 while supporting FP32 input and output data (right), enabling easy integration into DL and HPC programs and automatic acceleration of DL frameworks.

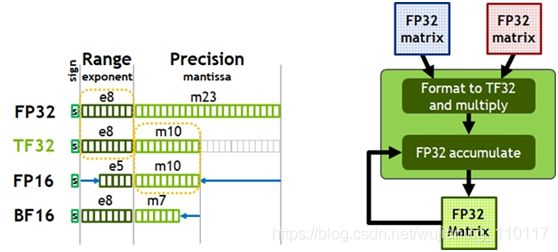

今天,人工智能训练的默认数学是FP32,没有张量核心加速度。NVIDIA安培体系结构引入了对TF32的新支持,使得人工智能训练在默认情况下可以使用张量核,而用户不必费劲。在产生标准IEEE FP32输出之前,非张量操作继续使用FP32数据路径,而TF32张量核读取FP32数据并使用与FP32相同的范围,同时降低内部精度。TF32包括8位指数(与FP32相同)、10位尾数(与FP16精度相同)和1个符号位。

与Volta一样,自动混合精度(AMP)使您能够使用FP16的混合精度进行人工智能训练,只需更改几行代码。使用AMP,A100提供比TF32快2倍的张量核心性能。

综上所述,用户对NVIDIA安培架构数学进行DL培训的选择如下:

默认情况下,使用TF32张量核,不调整用户脚本。与A100上的FP32相比,吞吐量高出8倍;与V100上的FP32相比,吞吐量高出10倍。

应使用FP16或BF16混合精度训练以获得最大训练速度。与TF32相比,吞吐量增加了2倍,与A100上的FP32相比,吞吐量增加了16倍,与V100上的FP32相比,吞吐量增加了20倍。

A100张量核加速高性能混凝土

高性能计算机应用的性能需求正在迅速增长。许多科学和研究领域的应用都依赖于双精度(FP64)计算。

为了满足HPC计算快速增长的计算需求,A100 GPU支持张量运算,加速符合IEEE标准的FP64计算,使FP64的性能达到NVIDIA Tesla V100 GPU的2.5倍。

A100上新的双精度矩阵乘法加法指令取代了V100上的8条DFMA指令,减少了指令获取、调度开销、寄存器读取、数据路径功率和共享内存读取带宽。

A100中的每个SM总共计算64个FP64 FMA操作/时钟(或128个FP64操作/时钟),是特斯拉V100吞吐量的两倍。A100 Tensor Core GPU具有108条短信息,峰值FP64吞吐量为19.5tflops,是Tesla V100的2.5倍。

有了对这些新格式的支持,A100张量核可以用于加速HPC工作负载、迭代求解器和各种新的AI算法。

Table 2. A100 speedup over V100 (TC=Tensor Core, GPUs at respective clock speeds).

- Effective TOPS / TFLOPS using the new Sparsity feature

A100 introduces fine-grained structured sparsity

NVIDIA使用A100 GPU引入了细粒度结构稀疏性,这是一种新的方法,可以使深部神经网络的计算吞吐量翻倍。

在深度学习中,稀疏性是可能的,因为个体权重的重要性在学习过程中不断演化,到网络训练结束时,只有一个子集的权重在确定学习输出时获得了有意义的目的。剩下的权重不再需要了。

细粒度结构稀疏性对允许的稀疏性模式施加了约束,使硬件更有效地对输入操作数进行必要的对齐。由于深度学习网络能够在基于训练反馈的训练过程中自适应权值,NVIDIA工程师发现,结构约束一般不会影响训练网络的推理精度。这使得能够以稀疏性推断加速度。

对于训练加速,需要在训练过程的早期引入稀疏性以提供性能效益,而训练加速而不损失精度的方法是一个活跃的研究领域。

稀疏矩阵定义

结构是通过一个新的2:4稀疏矩阵定义来实现的,该定义允许每四个入口向量中有两个非零值。A100支持行上2:4的结构化稀疏性,如图9所示。

由于矩阵结构清晰,因此可以有效地压缩它,并将内存存储和带宽减少近2倍。

Figure 9. A100 fine-grained structured sparsity prunes trained weights with a 2-out-of-4 non-zero pattern, followed by a simple and universal recipe for fine-tuning the non-zero weights. The weights are compressed for a 2x reduction in data footprint and bandwidth, and the A100 Sparse Tensor Core doubles math throughput by skipping the zeros.

NVIDIA开发了一个简单而通用的方法,用这种2:4结构的稀疏模式来稀疏化深层神经网络进行推理。该网络首先使用稠密权值进行训练,然后应用细粒度结构化剪枝,最后通过附加的训练步骤对剩余的非零权值进行微调。这种方法实际上不会导致基于横跨视觉、对象检测、分割、自然语言建模和翻译的数十个网络的评估的推断精度损失。

A100 Tensor-Core GPU包含新的稀疏Tensor-Core指令,这些指令跳过值为零的条目的计算,从而使Tensor-Core计算吞吐量加倍。图9显示了Tensor Core如何使用压缩元数据(非零索引)将压缩的权重与为输入到Tensor Core点积计算而适当选择的激活相匹配。

Combined L1 data cache and shared memory

首先在NVIDIA Tesla V100中引入的NVIDIA将L1数据缓存和共享内存子系统架构相结合,显著提高了性能,同时还简化了编程并减少了达到峰值或接近峰值应用程序性能所需的调整。将数据缓存和共享内存功能组合到单个内存块中,为这两种类型的内存访问提供最佳的总体性能。

一级数据缓存和共享内存的组合容量在A100中为192 KB/SM,而在V100中为128 KB/SM。

Simultaneous execution of FP32 and INT32 operations

与V100和Turing gpu类似,A100 SM还包括单独的FP32和INT32内核,允许以全吞吐量同时执行FP32和INT32操作,同时也增加了指令发出吞吐量。

许多应用程序都有执行指针算术(整数内存地址计算)的内部循环,这些内部循环与浮点计算结合使用,可从同时执行FP32和INT32指令中获益。流水线循环的每次迭代都可以更新地址(INT32指针算法)并为下一次迭代加载数据,同时在FP32中处理当前迭代。

A100 HBM2 DRAM subsystem

随着HPC、AI和分析数据集的不断增长以及寻找解决方案的问题变得越来越复杂,需要更多的GPU内存容量和更高的内存带宽。

特斯拉P100是世界上第一个支持高带宽HBM2存储技术的GPU架构,而特斯拉V100提供了更快、更高效、更大容量的HBM2实现。A100再次提高了HBM2的性能和容量。

HBM2内存由与GPU位于同一物理包上的内存堆栈组成,与传统的GDDR5/6内存设计相比,它提供了大量的功耗和面积节省,允许在系统中安装更多的GPU。有关HBM2技术基本细节的更多信息,请参阅NVIDIA Tesla P100:有史以来最先进的数据中心加速器白皮书。

A100 GPU的SXM4型电路板上有40GB的快速HBM2 DRAM内存。内存被组织为五个活动的HBM2堆栈,每个堆栈有八个内存片。A100 HBM2具有1215 MHz(DDR)的数据速率,可提供1555 GB/秒的内存带宽,比V100内存带宽高出1.7倍以上。

ECC内存弹性

A100 HBM2存储子系统支持单纠错双纠错码(SECDED)纠错码(ECC)保护数据。ECC为对数据损坏敏感的计算应用程序提供了更高的可靠性。在大规模集群计算环境中,gpu处理大型数据集或长时间运行应用程序时,它尤其重要。A100中的其他密钥存储结构也受到SECDED ECC的保护,包括二级缓存和一级缓存以及所有短消息中的注册文件。

A100 L2 cache

A100 GPU包含40 MB的二级缓存,比V100二级缓存大6.7倍缓存二级缓存分为两个分区,以实现更高的带宽和更低的延迟内存访问。每个二级分区定位和缓存数据,以便从直接连接到分区的gpc中的SMs进行内存访问。这种结构使A100能够提供比V100高2.3x的L2带宽。硬件缓存一致性在整个GPU中维护CUDA编程模型,应用程序自动利用新的二级缓存的带宽和延迟优势。

二级缓存是GPC和SMs的共享资源,位于GPC之外。A100 L2缓存大小的大幅增加显著提高了许多HPC和AI工作负载的性能,因为现在可以以比读取和写入HBM2内存快得多的速度缓存和重复访问更大部分的数据集和模型。一些受DRAM带宽限制的工作负载将受益于较大的二级缓存,例如使用小批量的深度神经网络。

为了优化容量利用率,NVIDIA安培体系结构为您提供了二级缓存驻留控制,用于管理要保留或从缓存中收回的数据。您可以为持久数据访问预留一部分二级缓存。

例如,对于DL推断工作负载,ping-pong缓冲区可以持久地缓存在L2中,以便更快地访问数据,同时还可以避免对DRAM的写回。对于生产者-消费者链(如在DL培训中发现的那些),二级缓存控件可以跨写-读数据依赖关系优化缓存。在LSTM网络中,递归权重可以优先缓存并在L2中重用。

NVIDIA-Ampere体系结构增加了计算数据压缩,以加速非结构化稀疏性和其他可压缩数据模式。二级压缩可使DRAM读/写带宽提高4倍,二级读取带宽提高4倍,二级容量提高2倍。

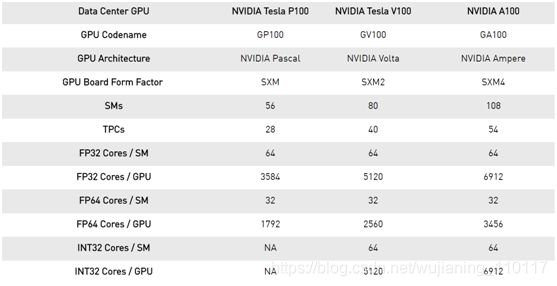

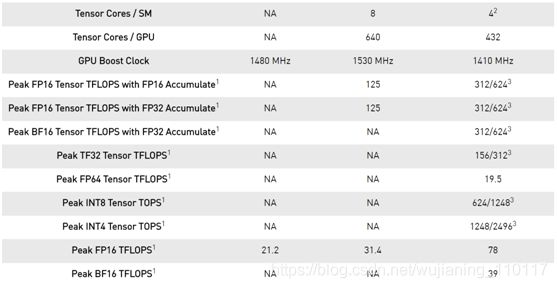

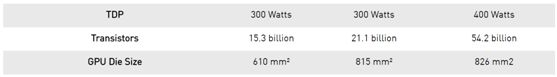

Table 3. Comparison of NVIDIA data center GPUs.

-

Peak rates are based on the GPU boost clock.

-

Four Tensor Cores in an A100 SM have 2x the raw FMA

computational power of eight Tensor Cores in a GV100 SM. -

Effective TOPS / TFLOPS using the new Sparsity feature.

注:由于A100 Tensor Core GPU设计用于安装在高性能服务器和数据中心机架中,为AI和HPC计算工作负载供电,因此它不包括显示连接器、用于光线跟踪加速的NVIDIA RT内核或NVNC编码器。

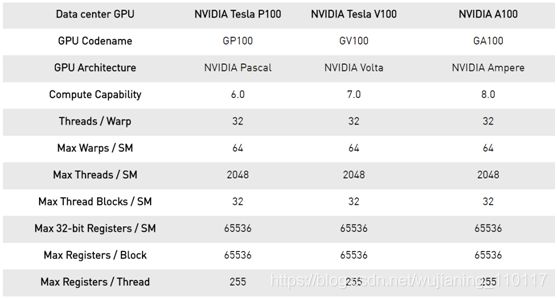

Compute capability

A100 GPU支持新的计算能力8.0。表4比较了NVIDIA GPU体系结构的不同计算能力的参数。

Table 4. Compute Capability: GP100 vs. GV100 vs. GA100.

MIG architecture

尽管许多数据中心工作负载在规模和复杂性上都在不断扩展,但一些加速任务并没有那么苛刻,例如早期开发或在低批量大小的简单模型上进行推理。数据中心管理者的目标是保持高资源利用率,因此一个理想的数据中心加速器不仅会变得很大,还会有效地加速许多较小的工作负载。

新的MIG特性可以将每个A100划分为多达7个GPU实例以获得最佳利用率,有效地扩展了对每个用户和应用程序的访问。

图10显示了Volta MPS如何允许多个应用程序在单独的GPU执行资源(SMs)上同时执行。但是,由于内存系统资源在所有应用程序之间共享,如果一个应用程序对DRAM带宽有很高的要求,或者其请求超额订阅了二级缓存,则可能会干扰其他应用程序。

图11中所示的A100 GPU新的MIG功能可以将单个GPU划分为多个GPU分区,称为GPU实例。每个实例的短消息在整个内存系统中都有独立的路径——片上纵横端口、二级缓存组、内存控制器和DRAM地址总线都是唯一分配给单个实例的。这确保了单个用户的工作负载可以在相同的二级缓存分配和DRAM带宽下以可预测的吞吐量和延迟运行,即使其他任务正在冲击自己的缓存或使DRAM接口饱和。

使用此功能,MIG可以对可用的GPU计算资源进行分区,以便为不同的客户端(如vm、容器、进程等)提供具有故障隔离的定义服务质量(QoS)。它允许多个GPU实例在单个物理A100 GPU上并行运行。MIG还保持CUDA编程模型不变,以最小化编程工作量。

csp可以使用MIG来提高其GPU服务器上的利用率,以不增加成本的方式提供最多7倍的GPU实例。MIG支持csp所需的必要的QoS和隔离保证,以确保一个客户端(VM、容器、进程)不会影响另一个客户端的工作或调度。

csp通常根据客户使用模式来划分硬件。只有当硬件资源在运行时提供一致的带宽、适当的隔离和良好的性能时,有效的分区才起作用。

使用基于NVIDIA安培体系结构的GPU,您可以在新的虚拟GPU实例上查看和调度作业,就像它们是物理GPU一样。MIG与Linux操作系统及其管理程序协同工作。用户可以使用诸如Docker Engine之类的运行时运行带有MIG的容器,并且很快就会支持使用Kubernetes的容器编排。

Figure 10. CSP Multi-user node today (pre-A100). Accelerated GPU instances are available for usage only at full physical GPU granularity for users in different organizations, even if the user applications don’t require a full GPU.

Figure 11. CSP multi-user with MIG diagram. Multiple independent users from the same or different organizations can be assigned their own dedicated, protected, and isolated GPU Instance within a single physical GPU.

错误和故障检测、隔离和控制

通过检测、包含并经常纠正错误和故障,而不是强制GPU重置,提高GPU的正常运行时间和可用性至关重要。这在大型、多GPU集群和单GPU、多租户环境(如MIG配置)中尤其重要。

NVIDIA安培体系结构A100 GPU包括改进错误/故障归因的新技术(对导致错误的应用程序进行属性化)、隔离(隔离故障应用程序,使其不影响在同一GPU或GPU集群中运行的其他应用程序),和包容(确保一个应用程序中的错误不会泄漏并影响其他应用程序)。这些故障处理技术对于MIG环境尤其重要,以确保共享单个GPU的客户端之间的正确隔离和安全性。

NVLink连接的gpu现在具有更强大的错误检测和恢复功能。远程GPU上的页面错误通过NVLink发送回源GPU。远程访问故障通信是大型GPU计算集群的一个重要恢复功能,有助于确保一个进程或VM中的故障不会导致其他进程或VM宕机。

A100 GPU还包括其他一些新的和改进的硬件功能,可以提高应用程序性能。有关更多信息,请参阅即将发布的NVIDIA A100 Tensor Core GPU体系结构白皮书。

CUDA11 advances for NVIDIA Ampere architecture GPUs

在NVIDIA-CUDA并行计算平台上构建了数千个GPU加速应用程序。CUDA的灵活性和可编程性使其成为研究和部署新的DL和并行计算算法的首选平台。

NVIDIA安培体系结构GPU旨在提高GPU的可编程性和性能,同时降低软件复杂性。NVIDIA安培体系结构gpu和CUDA编程模型的发展加速了程序执行,降低了许多操作的延迟和开销。

新的CUDA 11特性为第三代Tensor核、稀疏性、CUDA图、多实例gpu、L2缓存驻留控制以及NVIDIA-Ampere体系结构的其他一些新功能提供编程和API支持。

有关新CUDA功能的更多信息,请参阅即将发布的NVIDIA A100 Tensor Core GPU体系结构白皮书。有关新DGX A100系统的详细信息,请参见使用NVIDIA DGX A100定义AI创新。有关开发人员区域的更多信息,请参阅NVIDIA Developer,有关CUDA的更多信息,请参阅新的CUDA编程指南。

Conclusion

英伟达的使命是加速我们这个时代的达芬奇和爱因斯坦的工作。科学家、研究人员和工程师致力于利用高性能计算(HPC)和人工智能解决一些世界上最重要的科学、工业和大数据挑战。

NVIDIA A100 Tensor Core GPU为我们的加速数据中心平台带来了下一个巨大的飞跃,在每个规模上都提供了无与伦比的加速,使这些创新者能够在一生中完成他们一生的工作。A100为许多应用领域提供动力,包括HPC、基因组学、5G、渲染、深度学习、数据分析、数据科学和机器人技术。

推进当今最重要的HPC和AI应用个性化医疗、对话式AI和深度推荐系统需要研究人员做大。A100为包括Mellanox HDR InfiniBand、NVSwitch、NVIDIA HGX A100和Magnum IO SDK在内的NVIDIA数据中心平台提供了升级功能。这个集成的技术团队有效地扩展到数以万计的gpu,以前所未有的速度训练最复杂的AI网络。

A100 GPU的新MIG功能可以将每个A100划分为多达7个GPU加速器,以实现最佳利用率,有效地提高GPU资源利用率和GPU对更多用户和GPU加速应用程序的访问。通过A100的多功能性,基础设施管理人员可以最大限度地利用其数据中心中的每个GPU,以满足不同规模的性能需求,从最小的作业到最大的多节点工作负载。