微机原理·第六章输入输出技术总结(未写完)

6.1.1外部设备概述

主机:CPU和主存

输入输出设备:主机之外,外部设备,又称外设

基本的输入输出方法:1.程序控制I/O方式,2.DMA方式

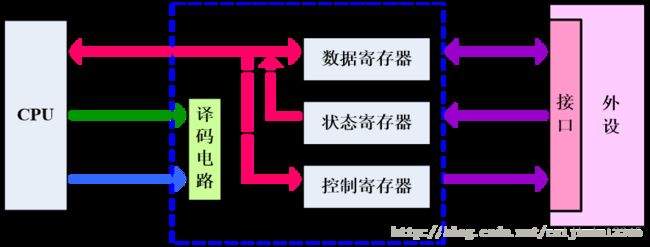

I/O接口可以反映接口的状态,传输数据以及控制读写。

CPU对外设的访问实际上是对I/O接口电路的端口访问

不同的端口可以是同一I/O地址(一个输入输出共用一个I/O地址)

内存地址:统一编址

I/O地址:独立编址

6.1.4 I/O端口地址译码

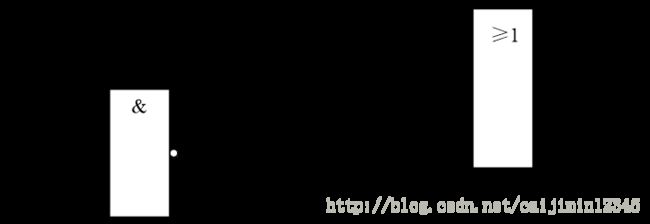

【例6.1】使用8位I/O地址5CH选择输入端口。用逻辑门器件实现。

|A15|A14|A13…|A7|A6|A5|A4|A3|A2|A1|A0|

0……………………….0 1 0 1 1 1 0 0

A2,3,4,6都要为1才能选中使左边都为非,IOR也是非,这样最后或起来的结果才是5C非,即选中了5C作为输入端口。

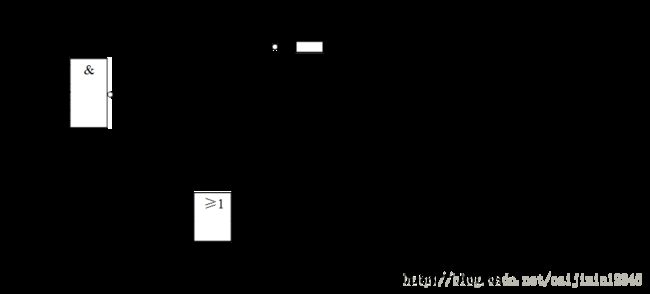

【例6.2】使用16位I/O地址A0D8H~A0DFH选择I/O端口。用译码器件实现。

全地址译码,就是通过LS138把每个都选出来,不会出现遗漏,但是部分地址译码可能会出现地址重叠的情况,但是占用空间小。

6.1.5基本的并行输入/输出接口

三态缓冲器是最基本的输入接口,数据锁存器是最基本的输出接口

原因:三态缓冲器是变化的值,不具有保持功能,适合加载到不断变化的总线上。而数据锁存器可以提供稳定的输出。

一、并行输入接口

这是一种并行输入接口

IN AL,80H;从80H端口获得8个开关接通或断开的信息放入AL寄存器中。执行这条语句的时候,IO地址是有效的,IOR非是有效的

8个开关就是256个单元。也就是从内存地址为80开始往下256个单元。

AL=0是关闭,AL=1是打开。

电阻这么大的原因是过大的电流会对273的接口造成损伤。

二、并行输出端口

利用74LS273设计8/16位输出端口

这里的反向驱动器是防止电流倒灌,减轻273的压力

这里的电阻跟之前的电阻不一样的原因可能是每个驱动器对电流的承受力不同吧。

这里273是没有CP的,说明锁存器内数据不变。

另外273是做实验是跟灯泡连在一起的,330欧不大不小,刚好合适。

有一段输出的程序,来稍微分析一下

MOV DX,3804H;3804是一个端口,把端口地址放在段寄存器

MOV AL,00H;将AL寄存器里面的数据设为低

OUT DX,AL;让端口的8个二极管都不亮

MOV DX,3805H;

MOV AL,0FFH;数据第一位是字母的时候,应该加0,0FF表示都为高

OUT DX,AL;让端口与8035的8个三极管都亮

MOV DX,3804H;

MOV AX,0FFFFH;放到AX里面,就是16位,4个FFFF

OUT DX,AX;让3804和3805的一共16个灯都不亮。

| 地址 | 字节 |

|---|---|

| 3804 | FF |

| 3805 | FF |

自动填充到3805。

6.2程序查询I/O方式

三态门作为数据输入接口的一般连接模式

查询方式

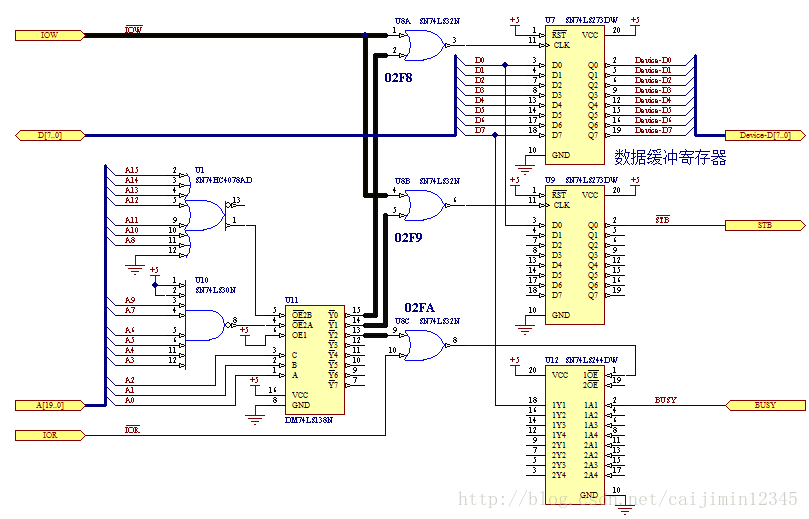

要将8086/88系统中内存首地址为D2000H开始的顺序1000个数据输出给此外设。

嗯,是这样的

STB相当于一个选通信号,BUSY表示忙,如果不忙的话就可以输入数据进入这个设备。

从第一条竖线开始看,这个时候,没有选通,不忙,数据正在输入到设备,4号位置的时候,选通了输出设备,但是有个延迟,还需要100us的延迟(这里可以确保输入数据接着输入),100us后STB的上升沿触发到BUSY,使BUSY变为忙,这个时候就开始处理数据了,就无法再接受数据了,处理完数据后BUSY又置为0,表示不忙。

这个图的解析:

需要控制,数据,状态三种端口,三种信息均与数据总线相连,根据当前指令决定哪个端口有效(产生不同的I/O地址控制三个端口)

这里有段代码

作用是将8088系统中从内存地址为D2000H开始的顺序1000个数据输出给图6.14中的外设,代码如下:

DAOUT: MOV AX, 0D200H

MOV DS, AX;前两句是段地址初始化

MOV BX, 0 ;初始化内存首地址

MOV CX, 1000 ;初始化计数器

MOV DX, 02F9H;16位地址,用DX 间接提供

MOV AL, 01H;

OUT DX, AL ;初始化选通信号STB非

NEXT: MOV DX, 02FAH

WAT: IN AL, DX

AND AL, 80H;这里为什么要比较的是80呢,因为80是10000000,比较的是最高位为1,因为244是Y1跟数据总线的D7相连,也就是需要判断最高位为1。

JNZ WAT ;状态查询环

MOV DX, 02F8H

MOV AL, [BX]寄存器间接寻址到02F8地址的内容

OUT DX, AL ;数据输出

MOV DX, 02F9H

MOV AL, 00H

OUT DX, AL;这里又执行了一遍是完成了数据输出,通知选通信号

CALL DLY100us ;DLY100μs为100μs的延迟子程序

MOV AL, 01H

OUT DX, AL ;产生选通信号 ,这里使得产生一个多脉冲数到数据输出到device中。

INC BX ;修改内存指针

LOOP NEXT ;输出次数的循环控制

RET ;过程返回

多外设的查询控制:轮询。多外设查询非重点。

6.3中断方式

6.3.1中断概述

查询方式缺点:CPU**效率低,无法满足实时性**要求

中断的作用:

实现CPU与I/O设备并行工作:键盘输入响应,打印机输出

处理硬件故障和软件错误:故障→中断→自动恢复,掉电后自动保存当前状态

实现人机交互:键盘、鼠标中断;死循环处理(Ctrl-C)

实现多道程序、分时操作:时钟中断

实时处理快速响应:对随机事件的快速响应

实现应用程序与操作系统的切换

操作系统安全,软中断,陷阱

中断:CPU暂停现行程序,转而处理随机到来的事件,待处理完后再回到被暂停的程序继续执行

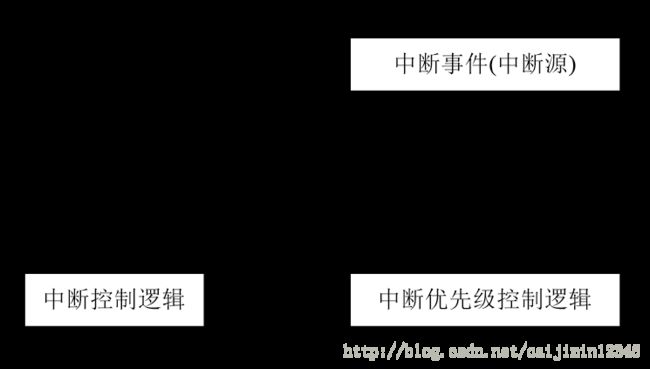

微机系统中实现中断的基本模型

中断源:内部→内中断;外部→外中断

中断过程:

1.中断请求:由中断源发出,上升沿,高电平

2.中断响应:在每条指令的最后一个时钟周期,CPU检测INTR或NMI信号。

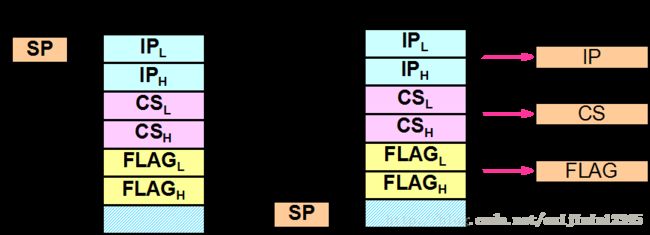

3.断点保护:通过压栈的方式进行断点保护

4.中断源识别:A.软件查询法,对于外中断,该方法在硬件上需要输入接口的支持。B.中断矢量法,该方法对多个中断源进行编码,以此编码作为中断源识别的标志。(中断向量表,放在主存最低的1K)

| 示意图 |

|---|

| 引导程序或指向引导程序的地址->启动地址 |

| … |

| … |

| …->入口地址 |

| … |

| … |

| 中断向量表->1k |

5.中断服务

6.断点恢复

7.中断返回:执行中断返回指令IRET(IRET指令将使CPU把堆栈内保存的断点信息弹出到IP、CS和FLAG中,保证被中断的程序从断点处能够继续往下执行)

INTR中断过程

中断优先级嵌套:多个中断源同时提出中断请求。正在执行某中断服务程序时,更高优先级的中断源提出请求。

嵌套原则:速度快的外设优先;对于等速设备,输入优先于输出。

中断嵌套示意图

中断嵌套的解决办法有如下:

(1,2,3非重点)

1.软件查询

2.硬件链式优先级排队电路

3.硬件优先级编码比较电路

4.利用可编中断控制器(PIC)

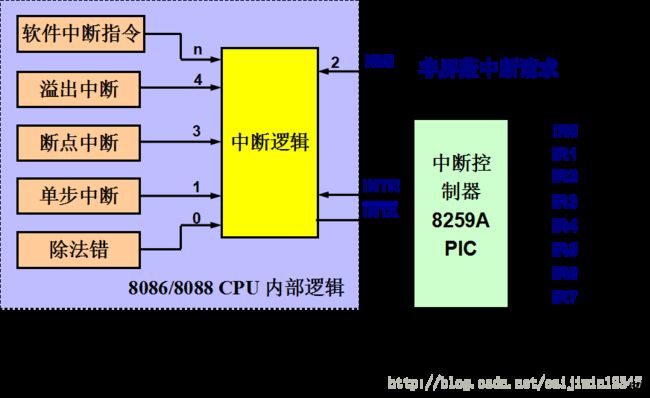

6.3.2 Intel 16位中断系统

1.中断源类型:与中断有关的控制线为:NMI、INTR、INTA非

8088系统的中断源

内部中断

除法溢出:类型号0,商大于目的操作数所能表达的范围时产生。

单步中断:类型号1,TF=1时产生(当前指令需执行完)

断点中断:类型号3,这是一个软件中断,即INT 3指令。

溢出中断:类型号4,这是一个软件中断,即INTO指令。

软件中断:即INT n指令,类型号n(0-255)。

外部中断

非屏蔽中断NMI:类型号2,不可用软件屏蔽,PU必须响应它。

可屏蔽中断INTR:类型号由PIC提供。IF=1时CPU才能响应。

8086/8088中断源类型