简谈 Intel altera 和 Xilinx 的 FPGA 区别

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天和大侠简单聊一聊 Intel altera 和 Xilinx 的 FPGA 区别,话不多说,上货。

最近有很多人在问,学习FPGA到底是选择 Intel altera 的还是 xilinx 的呢,于是我就苦口婆心的说了一大堆,中心思想大概就是,学习FPGA一定要学习 FPGA 的设计思想以及设计原理,不要纠结于单一的实验平台或者操作软件,因为你想在这个行业越走越高的话,广度和深度都是要有所了解的,初期学习的时候尤其注重动手,选择一款操作平台以及操作软件是为了让你更好的去动手做,而不是让你在这款软件或者实验平台去做文章,因为不懂原理的话,换个环境你同样是什么都不明白。尤其是现在的科技公司产品更新升级换代还比较快,要学会去掌握最核心的知识点才是王道。下面,就我自己接触,咱们就来简单聊聊 Intel altera和 Xilinx 的FPGA 区别,欢迎大家一起交流,三人行,必有我师,共同学习,共同进步。

对于 Intel altera 和 Xilinx 的FPGA,本人认为可以分为两个方面去比较一下,基本逻辑资源和内部基本架构。

从目前企业中做开发使用的广泛性来说,Xilinx 占得比重确实是大一些,但是从其他方面来说,比如价格,相对而言 Intel altera 的便宜些。对于两者的特点,Xilinx 的短线资源非常丰富,这样在实现的时候,布线的成功率很高,尤其是逻辑做得比较满的时候。而 Intel altera 的 FPGA 的短线资源经常不够用,经常要占用LE来充当布线资源,这也是为什么 Intel altera 的 FPGA可以便宜的原因,资源少些当然便宜,但是如果你是高手,也能把他的性能发挥得很好。 另外就是关于块RAM,Xilinx的双口RAM是真的,Intel altera的没有双口RAM,如果你要实现真正的双口RAM,只能用两块RAM来背靠背地实现,这样你的RAM资源就少了一半,如果你的应用对片内双口RAM的需求很重要,用 Intel altera 的就划不来。

下面咱们就从我刚才说的基本逻辑资源和内部基本架构这两个方面来聊聊。

1、基本逻辑资源

基本的逻辑资源我建议大家可以去看看两家的芯片做个比较,今天时间有限就不给各位详谈了,通过比较你会发现我上面说的还是有点道理的。

2、内部基本架构

从1985年Xilinx公司推出第一片FPGA到现在,FPGA的使用已经有近30年的历史了。目前主流市场的FPGA主要还是Xilinx和Intel altera两大系列,下面分别来介绍下它们各自的基本结构组成。

Xilinx的FPGA主要由以下单元结构组成:可配置逻辑块(CLB)、时钟管理模块(CMT)、存储器(RAM/FIFO)、数字信号处理模块(DSP)和一些专用模块。以Virtex-5为例,简单介绍下各模块的功能。

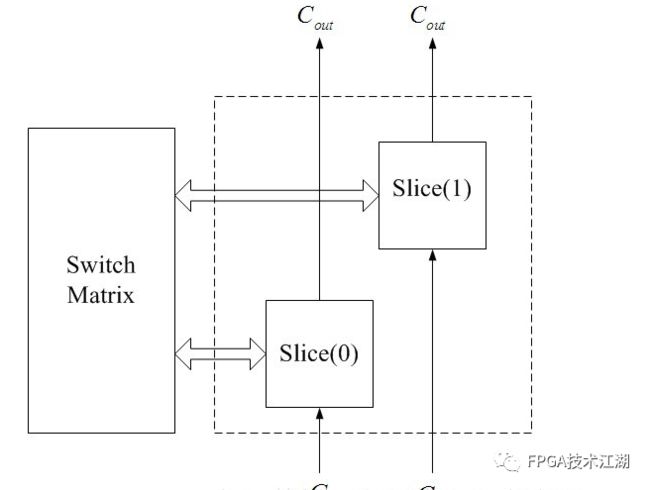

1、CLB是FPGA中组成设计逻辑的主要资源,也是电路设计中工作的主要对象,下面对CLB的内外结构做一个简单介绍。FPGA的逻辑就是由阵列排布的CLB实现的,每个CLB单元都和一个开关阵列相连,并受其控制以实现逻辑,如下图所示:

每一个CLB中包含有两个基本结构(Slice),每个基本结构中包含4个查找表(LUT)、4个存储单元、广函数多路器(Wide_function Multiplexer)和进位逻辑,这种基本结构(Slice)称为SLICEL。另外,有些基本结构(Slice)中还包含使用RAM存储数据的功能和使用32位寄存器移位的功能,支持这些功能的基本结构称为SLICEM。

2、时钟管理模块(CMT

时钟管理模块(CMT)用于产生高质量的时钟,以Virtex-5系列器件为例,CMT包括两个 数字时钟管理单元(DCM)和一个锁相环电路(PLL)。

3、存储器(RAM/FIFO

现代Xilinx的FPGA都有内部的存储器块,以Virtex-5为例,内部包含若干块RAM,每一块36KB,并且RAM的大小可以灵活配置。Virtex-5内的RAM是同步的双口RAM,并且可以配置为多速率的FIFO存储器,极大地提高了设计的灵活性。

4、数字信号处理模块(DSP

大多数的FPGA产品都提供了DSP。

5、其他专用模块

除了上述模块外,在现代的Xilinx的FPGA产品中还有一些其他专用模块,例如:Rocket IO千兆位级收发器、PCI Express端点模块和三态以太网MAC模块等。

Intel altera 的产品一般包括如下单元结构:逻辑阵列模块(LAB)、TriMatrix存储器模块(RAM)、数字信号处理模块(DSP)和锁相环模块(PLL)。下面以StartixII 器件为例说明Altera 公司产品的结构。

1、逻辑阵列模块(LAB)

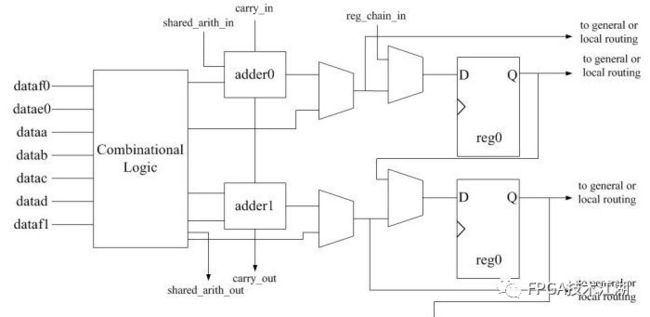

逻辑阵列模块(LAB)的主要结构是8个适应逻辑模块(ALM),还包括一些进位链和控制逻辑等结构。适应逻辑模块(ALM)是StratixII器件的基本模块,其结构如下图。

每个ALM中都包含了两个可编程的寄存器、两个专用全加器、一个进位链、一个共享算术链和一个寄存器链。需要注意的是,在上图所示的组合逻辑块(Combinational Logic)中包含了两个4输入4 查找表(LUT)和4个三输入的查找表。

2、 存储器模块(RAM)

StratixII器件具有TriMatrix存储结构,它包括3种大小的嵌入式RAM块。TriMatrix存储器包括512位的M512块、4Kb的M4K块和512Kb的M-RAM块,每个都可以配置支持各种特性。

3、 数字信号处理模块(DSP)

DSP块结构是为实现多种 最大性能和最小逻辑资源利用率的DSP功能而优化的。

4、 锁相环(PLL)

StratixII器件具有多达12个锁相环(PLL)和48个独立系统时钟,可以作为中央时钟管理器满足系统时序需求。

以上可以看出,Xilinx与 Intel altera的FPGA的结构最大不同还是其逻辑单元部分:Xilinx的逻辑单元基本组成为可配置逻辑模块(CLB),而Intel altera 的为LAB,但更深一层讲,CLB和LAB里面也都是由LUT、触发器等构成的。两个公司的FPGA组成各有特点,这也决定了它们的FPGA产品在功能上各有特点。

总的来说,Xilinx家独有 可配置逻辑块(CLB)/Slice,Altera家独有逻辑阵列模块(LAB),可以这么理解。

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!